可控矽控制之嵌入式軟體實現思路

阿新 • • 發佈:2018-12-21

可控矽控制之嵌入式軟體實現思路

前言

在嵌入式中可控矽控制在很多地方是不可替代的,本人在使用可控矽對燈帶的控制中遇了到很多問題,但最終還是解決了這個控制問題,並且在這兒分享給大家,希望對各位有所幫助。

原理

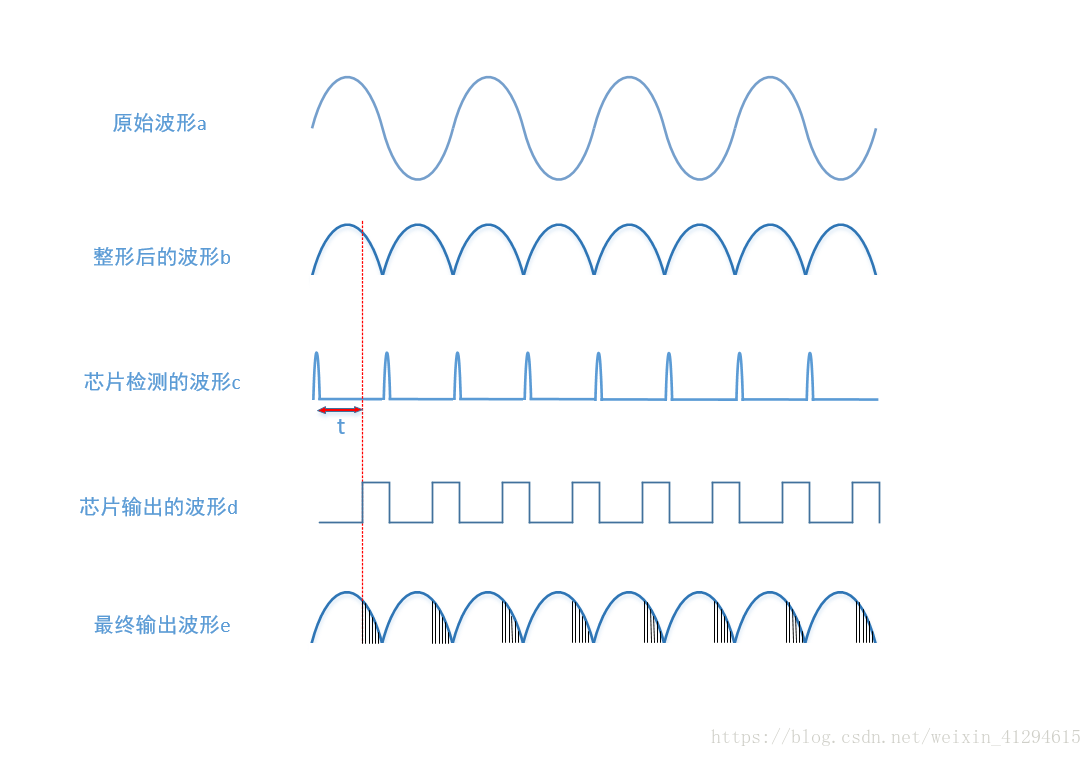

在這兒先講一下大致的原理以及問題描述,先來一張圖:

通常硬體得到的是,

【原始波形a】, 硬體方面通過濾波整形等一系列操作後拿到

【整形後的波形圖b】,過零檢測就是要檢測零點,硬體方面也可以實現。最後傳給我晶片的波形圖大致如

【晶片檢測的波形c】所示, **難點:晶片就是檢測這個零點,然後通過軟體設定t的長度,然後輸出類似

【晶片輸出的波形d】

通常硬體得到的是,

【原始波形a】, 硬體方面通過濾波整形等一系列操作後拿到

【整形後的波形圖b】,過零檢測就是要檢測零點,硬體方面也可以實現。最後傳給我晶片的波形圖大致如

【晶片檢測的波形c】所示, **難點:晶片就是檢測這個零點,然後通過軟體設定t的長度,然後輸出類似

【晶片輸出的波形d】那就開始吧

既然原理知道了就開始吧!

(因為涉及公司程式碼不方便給出,所以這裡將思路流程講給大家,希望聰明的你能夠看明白^_^)

講解

需要的資源

- PWM波:這裡我是用的是STM32的晶片,裡面需要進行輸出PWM的配置,晶片只要有定時器基本上都能夠配置,(不要用IO口模擬PWM輸出,因為很佔用CPU資源)這裡講PWM波的週期設定為和輸入波形週期一致,或者略小一點。

- 外部中斷:需要配置一個外部中斷,用於檢測零點,觸發方式我採用的是下降沿觸發(主要作用是檢測【晶片檢測的波形c】中的小尖尖),大部分工作是在外部中斷函式中實現的。

檢測輸出

首先晶片上電——進入主程式——進行各種功能的初始化操作——等待外部中斷

當接收到過零點時,會進入外部中斷函式在外部中斷中進行PWM波的佔空比進行設定(如果不需要改變輸出的狀態就不需要改變PWM的佔空比),接下來進行PWM計數值重置(相當於PWM波從低電平開始從新輸出),然後就回到主函式執行其他功能,沒錯!就這麼簡單。

這樣控制的優點

- 中斷函式中執行的程式不多,不會很佔用CPU資源

- 留給主程式其他功能的時間很多,可以在外部完成自己的任務。當外部進行PWM波佔空比的設定後,再進入中斷函式會自動按照新的佔空比進行輸出,響應的時間不超過過零檢測的週期。

- 因為是【晶片輸出的波形c】和【晶片檢測的波形c】週期差不多的PWM波,當某一個或者幾個【晶片檢測的波形c】的波形丟失後,不會對最終控制結果有太大影響。

小編使用過,但最終放棄的控制方法

- 採用延時操作:改變【晶片檢測的波形c】中的” t “, 這樣非常消耗CPU資源,如果跑Linux系統或者其他的小型作業系統還好。裸板開發這樣做的話CPU根本就不能去完成其他的功能。

- 採用定時器:通過加入時間標誌位,記錄每次進入定時器中斷的時間,在進入外部中斷時將這個時間標誌位清零。然後在裡面用很多標誌位用IO口模擬輸出觸發電平。這樣有很多弊端,定時器必須比【晶片檢測的波形c】的週期更小,定時器週期越小輸出等級越多CPU消耗就越大,定時器週期越小輸出等級越少CPU消耗就越小,這樣接造成了一個不能夠兩全其美的方法,最重要的是,在具體控制過程中波形會週期性平移(這個我找了好久都沒找到原因,哪個小夥伴知道原因的話希望能夠給鄙人講解一下,先謝過了),無論怎麼樣,這方案已經被我PASS掉了。

總結

本人在控制過程中嘗試過很多種方法,最終選擇了最上面這種方法,而且控制效果真的很不錯。

因為客觀原因真的不能貼程式碼 ::>_<:: 再次抱歉啦。