測試MCU I/O和CPLD的通信(舊博客遷移)

阿新 • • 發佈:2018-12-24

電阻 cas bec 判斷 其余 edge apt data- 博客 一、硬件連接

STC89LE52RC的P0[7:0]、P2[7:0]、P3[7:2]、P1[2:0]和ALE共26個信號與EPM1270相連;

另外利用CPLD外接的四位撥碼開關和八個LED燈進行控制及指示;

二、測試流程

根據四位撥碼開關的狀態,選擇P0~P3的端口值輸出到LED上,用ALE作時鐘同步;

三、C51 Code

#include "STC89C5xRC.h"

void main(void)

{

P0 = 0xff;

P1 = 0xff;

P2 = 0xff;

P3 = 0xff;

while (1)

{

P0 = 0x0f;

P2 = 0xf0;

P3 = 0xaa;

P1 = 0x05;

}

}

四、Verilog Code

module mcu

(

input[7:0]b_MCU_P0,

input[7:0]b_MCU_P2,

input[7:2]b_MCU_P3,

input[2:0]b_MCU_P1,

input[4:1]i_SW,

inputi_MCU_ALE,

output[8:1]o_LED

);

reg[8:1]r_LED;

always @(posedge i_MCU_ALE)

begin

case (i_SW)

4‘b0001:r_LED <= b_MCU_P0;

4‘b0010:r_LED <= b_MCU_P2;

4‘b0100:r_LED <= {b_MCU_P3, 3‘b000};

4‘b1000:r_LED <= {5‘b0_0000, b_MCU_P1};

default:r_LED <= 8‘b0000_0000;

endcase

end

assign o_LED = ~r_LED;

endmodule

五、實驗現象

除了P0端口無法值無法顯示,其余正常,初步判斷應是沒加上拉電阻引起,後續加上再測試。

六、續

P0口加4.7K上拉電阻,顯示一切正常!

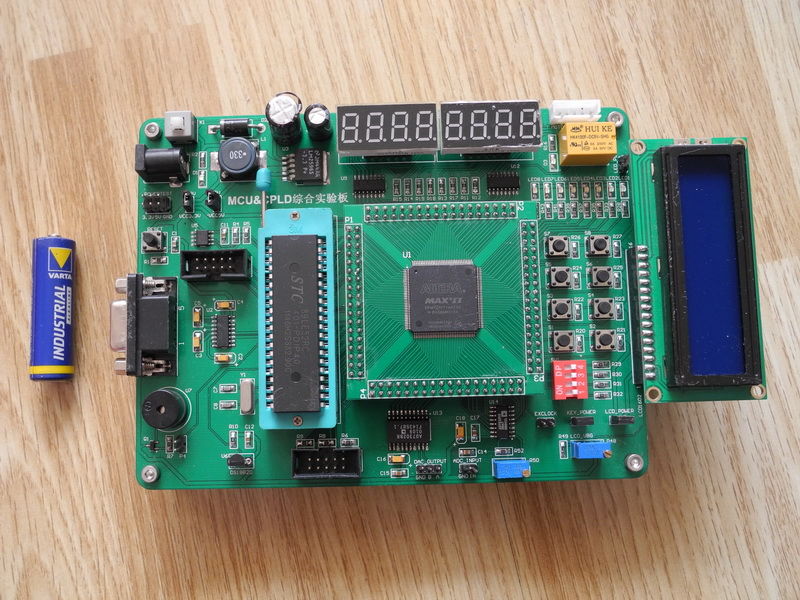

*有同學知道這塊開發板資料的(原理圖尤佳) 請聯系我:)

六、續

P0口加4.7K上拉電阻,顯示一切正常!

*有同學知道這塊開發板資料的(原理圖尤佳) 請聯系我:)

測試MCU I/O和CPLD的通信(舊博客遷移)