Linux Support for ARM LPAE 分析

https://blog.csdn.net/duanlove/article/details/16986133

介紹

早期的ARM系統僅需要MB級別的RAM,但是,隨著裝置的升級,現在更多複雜的智慧手機裝置 需要 百M甚至GB級別的RAM,而32bit的實體地址空間就顯得捉襟見肘了。

更讓人緊張的是,這些地址空間不僅僅是RAM佔用了,還有 外設、FLASH儲存器以及系統ROM也佔用了部分地址空間。

新興起的 移動虛擬化 需要更多是RAM,當然在 Guest OS級別一般來說是不需要這麼多的。 ARM LPAE 對linux系統的開發提供了這方面的支援。第一個linux上對LPAE的支援是是在 2010年十月份,釋出在LKML(

經典ARM MMU 與支援LPAE的比較

經典的ARM MMU特性如下:

32bit的實體地址空間。

2級頁錶轉換。

-

通過TTBR0標示的 使用者空間的對映; 以及TTBR1 標示的核心空間的對映。但是對於 核心空間和user空間的記憶體是嚴格限制的。

-

32bit 的頁表項( table entres: 頁表項,或者說 頁表條目)。

1級頁表八婆韓4096個頁表項(4 pages for PGD)。

-

每個頁表項可以對映為 1MB的段(section)。

-

每個頁表項可以指向 二級頁表。

-

實現已定義的 16MB supersections。

-

二級頁表包含256個條目,每個條目指向4KB的頁。 每個二級頁表1KB 。

傳統的ARM MMU 的限制

ARM PLAE的特性:

40bit的實體地址(1TB)

40bit的中間實體地址(1TB)空間(Guest 實體地址空間)

三級頁錶轉換

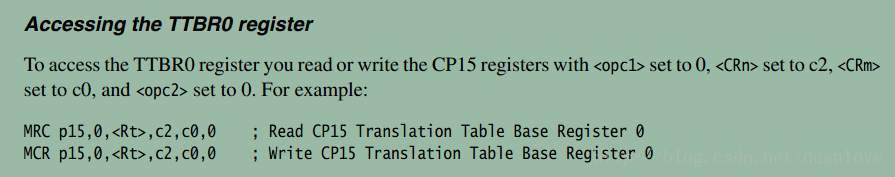

- TTBR0暫存器用作使用者空間的對映,TTBR1用作kernel空間的對映。

具備1GB的核心空間對映,不適用一級頁表。 - 每個級別有64bit的頁表項

一級頁表包含4個頁表項(stage1 轉換)

1GB的段 或者 指向二級頁表。

二級頁表包含512個條目(所有的條目總共佔4KB的儲存空間)

- 2MB的段, 或者指向三級頁表。

三級頁表包含512個條目。

- 每個條目對映4KB範圍的地址。

- 可以為連續的頁表 設定 contiguity flag(一系列連續的flag) 。

LDRD/STRD (64bit 的load/store) 指令是ARM處理器用於支援LPAE的原子性指令。即指令執行過程中是不可能中斷的。

僅僅支援簡單的頁表許可權模型。

- 沒有核心讀寫 和 使用者控制元件只讀 的許可權組合.

Domains (域)已經不復存在。(他們在ARMv7部分的linux裡已經被移除了)

另外有額外的bit位提供給OS使用.

專用的bit位提供給 使用者控制元件, 比如 只讀 和訪問標誌設定.

ASID 是TTBR0暫存器的一部分.

- 簡單的上下文切換程式碼. 不需要去處理預測的TLB, 去獲取錯誤的ASID.

- Context ID暫存器可以被專門用來除錯或者trace.

另外的許可權控制

- PXN - privilege execute never (非特權執行)

- SCTLR.WXN, SCTLR.UWXN - 防止從可以寫的地址空間執行(僅用於使用者空間的訪問)。

- APTable - 在子頁表級別裡用來限制許可權

- XNTable ,PXNTable - 在子頁表級別 複寫掉XN 和PXN bit位

用於記憶體區域屬性的新暫存器.

- MAIR0, MAIR1 - 32bit的記憶體屬性的間接暫存器.

- 可以同時配置8種記憶體型別.

微笑