verilog語法例項學習(9)

阿新 • • 發佈:2018-12-29

常用的時序電路介紹

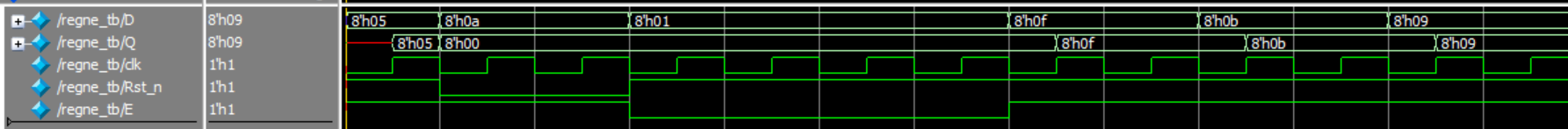

暫存器

一個觸發器可以儲存一位資料,由n個觸發器組成的電路可以儲存n位資料,我們把這一組觸發器叫做暫存器。暫存器中每個觸發器共用同一個時鐘。

下面是n位暫存器的程式碼,我們通過一個引數定義n,在例項化時傳入引數n。

module regne (D, clk,Rst_n,E,Q); parameter n=4; input [n-1:0] D; input clk; input Rst_n; //復位訊號 input E; //使能訊號 output reg [n-1:0] Q; always @(posedge clk,negedge Rst_n) if(Rst_n==0) Q <= 0; else if(E) Q <= D; endmodule

`timescale 1ns/1ns

`define clock_period 20

module regne_tb;

reg [7:0] D;

wire [7:0] Q;

reg clk;

reg Rst_n;

reg E;

regne #(.n(8)) regne(.D(D),.clk(clk),.Rst_n(Rst_n),.E(E),.Q(Q));

always # (`clock_period/2) clk = ~clk;

initial

begin

D = 4'b01010101;

clk = 1'b0;

Rst_n = 1'b1;

E = 1'b1;

#(`clock_period)

Rst_n = 1'b0;

D = 4'b10101010;

#(`clock_period*2)

E = 1'b0;

Rst_n = 1'b1;

D = 4'b00010001;

#(`clock_period*4)

E = 1'b1;

D = 4'b1111;

#(`clock_period*2)

D = 4'b10111011;

#(`clock_period*2)

D = 4'b10011001;

#(`clock_period*2)

$stop;

end

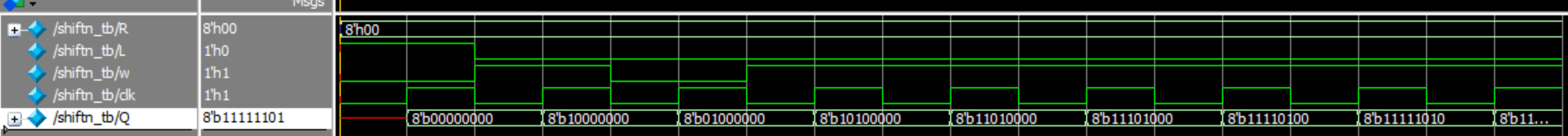

endmodule移位暫存器

把序列的輸入儲存到一個暫存器,可以選擇時機並行輸出。

/*序列輸入,並行輸出暫存器 從高位輸入,即從右向左輸入*/ module shiftn(R,L,w,clk,Q); parameter n=8; input [n-1:0] R;//初始值 input L; //load訊號 input w; //移入訊號 input clk;//時鐘訊號 output reg [n-1:0] Q; integer k; always @(posedge clk) begin if(L) Q <=R; else begin for(k=0; k<n-1; k=k+1) Q[k] <= Q[k+1]; Q[n-1] <= w; end end endmodule

`timescale 1ns/1ns

`define clock_period 20

module shiftn_tb;

reg [7:0] R;

reg L;

reg w;

reg clk;

wire [7:0] Q;

shiftn #(.n(8)) shitn0(.R(R),.L(L),.w(w),.clk(clk),.Q(Q));

initial clk = 0;

always #(`clock_period/2) clk = ~clk;

initial

begin

R = 8'b00000000;

L = 1'b1;

w = 1'b0;

#(`clock_period)

L = 1'b0;

w = 1'b1;

#(`clock_period)

w = 1'b0;

#(`clock_period)

w = 1'b1;

#(`clock_period)

w = 1'b1;

#(`clock_period)

w = 1'b1;

#(`clock_period)

w = 1'b1;

#(`clock_period)

w = 1'b1;

#(`clock_period)

w = 1'b1;

#(`clock_period)

$stop;

end

endmodule

View Code

我們也可以使用拼接符操作代替for迴圈,實現同樣的功能,而且語法更加簡單。

/*序列輸入,並行輸出暫存器 從高位輸入,即從右向左輸入*/ module shiftn(R,L,w,clk,Q); parameter n=8; input [n-1:0] R;//初始值 input L; //load訊號 input w; //移入訊號 input clk;//時鐘訊號 output reg [n-1:0] Q; always @(posedge clk) begin if(L) Q <=R; else begin Q = {w,Q[n-1:1]}; end end endmodule