TMS320F28335 CAN通訊 可以傳送,無法接收問題解決

阿新 • • 發佈:2018-12-30

其實可以傳送說明CAN已經調通,無法接收是因為被過濾了

主要涉及下面兩個暫存器

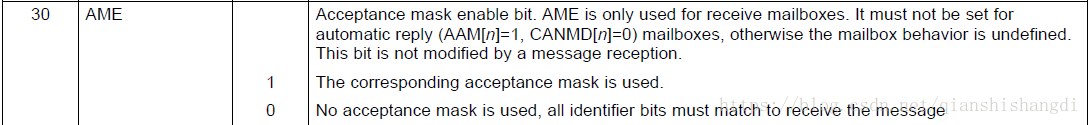

啟用mask功能

ECanaMboxes.MBOX0.MSGID.bit.AME = 1;

mask的所有位都不關心

ECanaLAMRegs.LAM0.all = 0xFFFFFFFF;

這樣就能接收到0號郵箱的所有報文啦。

示例程式碼

void CAN_Init(void)

{

// eCAN control registers require read/write access using 32-bits. Thus we

// will create a set of shadow registers for this example. These shadow