STM32學習筆記14——ADC part2

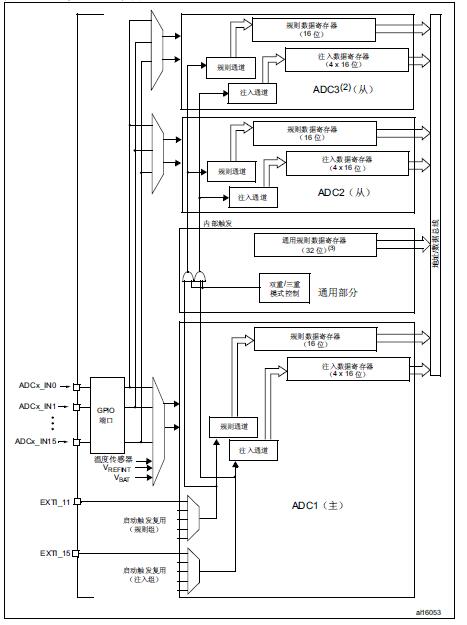

多重 ADC 模式

在具有兩個或更多 ADC 的器件中,可使用雙重(具有兩個 ADC)和三重(具有三個 ADC) ADC 模式(參見圖 41)。

在多重 ADC 模式下,通過 ADC1 主器件到 ADC2 和 ADC3 從器件的交替觸發或同時觸發來 啟動轉換,具體取決於 ADC_CCR 暫存器中的 MULTI[4:0] 位所選的模式。

注意:在多重 ADC 模式下,配置外部事件觸發轉換時,應用必須設定為僅主器件觸發而禁止從器件 觸發,以防止出現意外觸發而啟動不需要的從轉換。

可實現以下四種模式:

● 注入同時模式

● 規則同時模式

● 交替模式

● 交替觸發模式

也可按以下方式組合使用上述模式:

● 注入同時模式 + 規則同時模式

● 規則同時模式 + 交替觸發模式

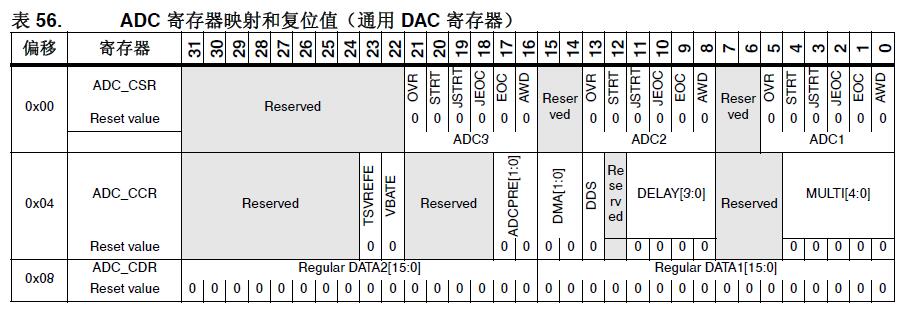

注意:在多重 ADC 模式下,可在多模式資料暫存器 (ADC_CDR) 中讀取轉換的資料。可在多模式狀 態暫存器 (ADC_CSR) 中讀取狀態位。

1. 儘管 ADC2 和 ADC3 上存在外部觸發,但它們並未顯示在此圖中。

2. 在雙重 ADC 模式下,不存在 ADC3 從器件部分。

3. 在三重 ADC 模式下,ADC 通用資料暫存器 (ADC_CDR) 包含 ADC1、ADC2 和 ADC3 的規則轉換資料。

按照所選的儲存順序使用全部 32 個暫存器位。

在雙重 ADC 模式下,ADC 通用資料暫存器 (ADC_CDR) 包含 ADC1 和 ADC2 的規則轉換資料。使用全部

32 個暫存器位。

● 多重 ADC 模式下的 DMA 請求:

在多重 ADC 模式下,可將 DMA 配置為使用三種不同的模式來傳輸轉換的資料。在所有情況下,要使用的 DMA 流均連線到 ADC:

— DMA 模式 1:每發出一個 DMA 請求(一個數據項可用),就會傳輸一個表示 ADC轉換的資料項的半字。

在雙重 ADC 模式下,發出第一個請求時傳輸 ADC1 的資料,發出第二個請求時傳輸 ADC2 的資料,依次類推。

在三重 ADC 模式下,發出第一個請求時傳輸 ADC1 的資料,發出第二個請求時傳輸ADC2 的資料,發出第三個請求時傳輸 ADC3 的資料;重複此序列。因此 DMA 首先傳輸 ADC1 的資料,隨後傳輸 ADC2 的資料,再傳輸 ADC3 的資料,依次類推。

DMA 模式 1 用於三重規則同時模式。

示例:

三重規則同時模式:生成 3 個連續的 DMA 請求(每個請求對應一個轉換資料項)

第 1 個請求:ADC_CDR[31:0] = ADC1_DR[15:0]

第 2 個請求:ADC_CDR[31:0] = ADC2_DR[15:0]

第 3 個請求:ADC_CDR[31:0] = ADC3_DR[15:0]

第 4 個請求:ADC_CDR[31:0] = ADC1_DR[15:0]

— DMA 模式 2:每傳送一個 DMA 請求(兩個資料項可用),就會以字的形式傳輸表

示兩個 ADC 轉換資料項的兩個半字。

在雙重 ADC 模式下,發出第一個請求時會傳輸 ADC2 和 ADC1 的資料(ADC2 資料佔用高位半字,ADC1 資料佔用低位半字),依此類推。

在三重 ADC 模式下,將生成三個 DMA 請求:發出第一個請求時,會傳輸 ADC2和 ADC1 的資料(ADC2 資料佔用高位半字,ADC1 資料佔用低位半字)。發出第二個請求時,會傳輸 ADC1 和 ADC3 的資料(ADC1 資料佔用高位半字,ADC3資料佔用低位半字)。發出第三個請求時,會傳輸 ADC3 和 ADC2 的資料(ADC3資料佔用高位半字,ADC2 資料佔用低位半字),依此類推。

DMA 模式 2 用於交替模式和規則同時模式(僅適用於雙重 ADC 模式)。

示例:

a) 雙重交替模式:每當有 2 個數據項可用時,就會生成一個 DMA 請求:

第 1 個請求:ADC_CDR[31:0] = ADC2_DR[15:0] | ADC1_DR[15:0]

第 2 個請求:ADC_CDR[31:0] = ADC2_DR[15:0] | ADC1_DR[15:0]

b) 三重交替模式:每當有 2 個數據項可用時,就會生成一個 DMA 請求

第 1 個請求:ADC_CDR[31:0] = ADC2_DR[15:0] | ADC1_DR[15:0]

第 2 個請求:ADC_CDR[31:0] = ADC1_DR[15:0] | ADC3_DR[15:0]

第 3 個請求:ADC_CDR[31:0] = ADC3_DR[15:0] | ADC2_DR[15:0]

第 4 個請求:ADC_CDR[31:0] = ADC2_DR[15:0] | ADC1_DR[15:0]

— DMA 模式 3:此模式與 DMA 模式 2 相似。唯一的區別是:在這種模式下,每傳送一個 DMA 請求(兩個資料項可用),就會以半字的形式傳輸表示兩個 ADC 轉換資料項的兩個位元組。此模式下的資料傳輸順序與 DMA 模式 2 相似。

DMA 模式 3 用於解析度為 6 位和 8 位時的交替模式。

示例:

a) 雙重交替模式:每當有 2 個數據項可用時,就會生成一個 DMA 請求

第 1 個請求:ADC_CDR[15:0] = ADC2_DR[7:0] | ADC1_DR[7:0]

第 2 個請求:ADC_CDR[15:0] = ADC2_DR[7:0] | ADC1_DR[7:0]

b) 三重交替模式:每當有 2 個數據項可用時,就會生成一個 DMA 請求

第 1 個請求:ADC_CDR[15:0] = ADC2_DR[7:0] | ADC1_DR7:0]

第 2 個請求:ADC_CDR[15:0] = ADC1_DR[7:0] | ADC3_DR[15:0]

第 3 個請求:ADC_CDR[15:0] = ADC3_DR[7:0] | ADC2_DR[7:0]

第 4 個請求:ADC_CDR[15:0] = ADC2_DR[7:0] | ADC1_DR7:0]

溢位檢測:如果在其中一個相關的 ADC(雙重和三重模式下的 ADC1 和 ADC2,僅有三重 模式時的 ADC3)上檢測到溢位,則不再發出 DMA 請求,以確保傳輸到 RAM 的所有資料都 有效。對於與某個 ADC 對應的 EOC 位,有時可能會因為此 ADC 的資料暫存器包含有效資料而保持置 1。

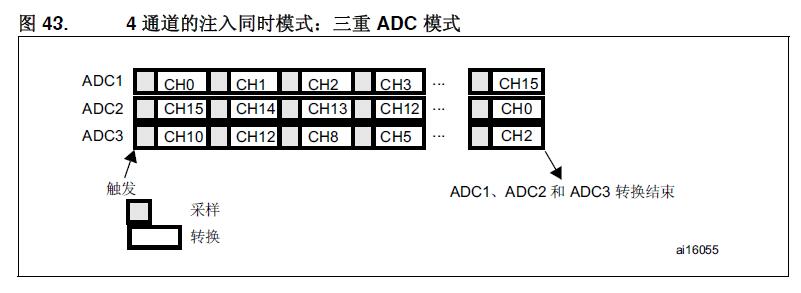

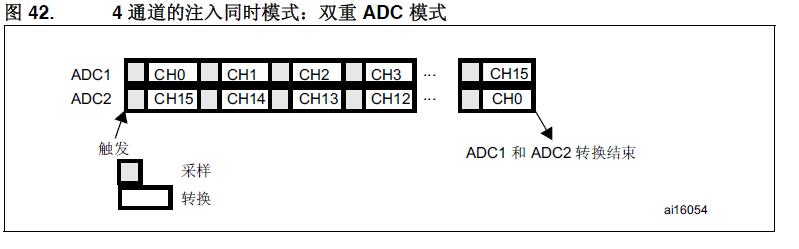

注入同時模式

此模式可轉換注入通道組。外部觸發源來自 ADC1 的注入組多路複用器(通過 ADC1_CR2 暫存器中的 JEXTSEL[3:0] 位進行選擇)。同時觸發可用於 ADC2 和 ADC3。

注意:不要在兩個/三個 ADC 上轉換同一通道(轉換同一通道時,不允許兩個/三個 ADC 取樣時間 重疊)。

在同時模式下,必須使用同一長度來轉換序列,或必須確保觸發之間的間隔長於 2 個序列 (雙重 ADC 模式)/3 個序列(三重 ADC 模式)中的較長時間。否則,當序列較長的 ADC 完 成上一次轉換時,序列較短的 ADC 可能重新開始轉換。

規則轉換可在一個或所有 ADC 上執行。這種情況下,它們彼此之間都是獨立的,而且會在 出現注入事件時中斷。它們會在注入轉換組結束時恢復轉換。

雙重 ADC 模式

在 ADC1 或 ADC2 轉換事件結束時:

● 轉換的資料會儲存在各個 ADC 介面的 ADC_JDRx 暫存器中。

● 當 ADC1/ADC2 的注入通道全部完成轉換後,會生成一個 JEOC 中斷(如果已在兩個

ADC 介面中的一個介面上使能)。

注入同時模式

此模式可轉換注入通道組。外部觸發源來自 ADC1 的注入組多路複用器(通過 ADC1_CR2 暫存器中的 JEXTSEL[3:0] 位進行選擇)。同時觸發可用於 ADC2 和 ADC3。

注意:不要在兩個/三個 ADC 上轉換同一通道(轉換同一通道時,不允許兩個/三個 ADC 取樣時間 重疊)。

在同時模式下,必須使用同一長度來轉換序列,或必須確保觸發之間的間隔長於 2 個序列 (雙重 ADC 模式)/3 個序列(三重 ADC 模式)中的較長時間。否則,當序列較長的 ADC 完 成上一次轉換時,序列較短的 ADC 可能重新開始轉換。

規則轉換可在一個或所有 ADC 上執行。這種情況下,它們彼此之間都是獨立的,而且會在 出現注入事件時中斷。它們會在注入轉換組結束時恢復轉換。

雙重 ADC 模式

在 ADC1 或 ADC2 轉換事件結束時:

● 轉換的資料會儲存在各個 ADC 介面的 ADC_JDRx 暫存器中。

● 當 ADC1/ADC2 的注入通道全部完成轉換後,會生成一個 JEOC 中斷(如果已在兩個ADC 介面中的一個介面上使能)。

注入同時模式

此模式可轉換注入通道組。外部觸發源來自 ADC1 的注入組多路複用器(通過 ADC1_CR2 暫存器中的 JEXTSEL[3:0] 位進行選擇)。同時觸發可用於 ADC2 和 ADC3。

注意:不要在兩個/三個 ADC 上轉換同一通道(轉換同一通道時,不允許兩個/三個 ADC 取樣時間 重疊)。

在同時模式下,必須使用同一長度來轉換序列,或必須確保觸發之間的間隔長於 2 個序列 (雙重 ADC 模式)/3 個序列(三重 ADC 模式)中的較長時間。否則,當序列較長的 ADC 完 成上一次轉換時,序列較短的 ADC 可能重新開始轉換。

規則轉換可在一個或所有 ADC 上執行。這種情況下,它們彼此之間都是獨立的,而且會在 出現注入事件時中斷。它們會在注入轉換組結束時恢復轉換。

雙重 ADC 模式

在 ADC1 或 ADC2 轉換事件結束時:

● 轉換的資料會儲存在各個 ADC 介面的 ADC_JDRx 暫存器中。

● 當 ADC1/ADC2 的注入通道全部完成轉換後,會生成一個 JEOC 中斷(如果已在兩個ADC 介面中的一個介面上使能)。

三重 ADC 模式

在 ADC1、ADC2 或 ADC3 轉換事件結束時:

● 轉換的資料會儲存在各個 ADC 介面的 ADC_JDRx 暫存器中。

● 當 ADC1/ADC2/ADC3 的注入通道全部完成轉換後,會生成一個 JEOC 中斷(如果已在三個 ADC 介面中的一個介面上使能)。

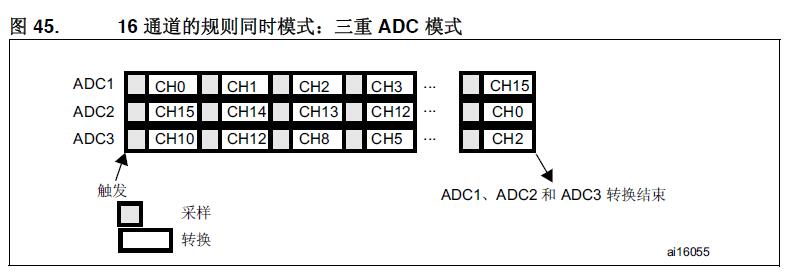

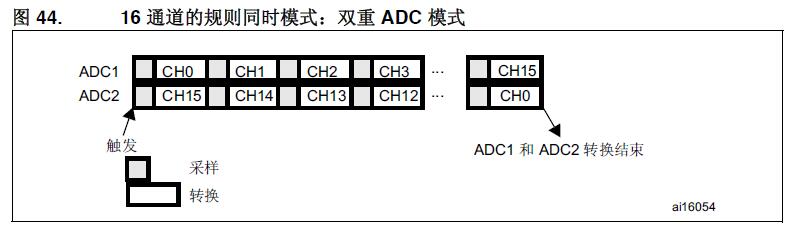

規則同時模式

此模式可用於規則通道組。外部觸發源來自 ADC1 的規則組多路複用器(通過 ADC1_CR2 暫存器中的 EXTSEL[3:0] 位進行選擇)。同時觸發可用於 ADC2 和 ADC3。

注意:不要在兩個/三個 ADC 上轉換同一通道(轉換同一通道時,不允許兩個/三個 ADC 取樣時間 重疊)。

在規則同時模式下,必須使用同一長度來轉換序列,或必須確保觸發之間的間隔長於 2 個序 列(雙重 ADC 模式)/3 個序列(三重 ADC 模式)中的較長轉換時間。否則,當序列較長的 ADC 完成上一次轉換時,序列較短的 ADC 可能重新開始轉換。

必須禁止注入轉換。

雙重 ADC 模式

在 ADC1 或 ADC2 轉換事件結束時:

● 會生成一個 32 位 DMA 傳輸請求(如果 ADC_CCR 暫存器中的 DMA[1:0] 位等於0b10)。此請求會將儲存在 ADC_CDR 32 位暫存器高位半字中的 ADC2 轉換資料傳輸到 SRAM,然後將儲存在 ADC_CCR 低位半字中的 ADC1 轉換資料傳輸到 SRAM。

● 當 ADC1/ADC2 的規則通道全部完成轉換後,會生成一個 EOC 中斷(如果已在兩個 ADC介面中的一個介面上使能)。

三重 ADC 模式

在 ADC1、ADC2 或 ADC3 轉換事件結束時:

● 會生成三個 32 位 DMA 傳輸請求(如果 ADC_CCR 暫存器中的 DMA[1:0] 位等於 0b01)。

之後會發生三次從 ADC_CDR 32 位暫存器到 SRAM 的傳輸:首先傳輸 ADC1 轉換資料,然後是 ADC2 轉換資料,最後是 ADC3 轉換資料。每次出現新的三階段轉換時都會重複這一過程。

● 當 ADC1/ADC2/ADC3 的規則通道全部完成轉換後,會生成一個 EOC 中斷(如果已在三個 ADC 介面中的一個介面上使能)。

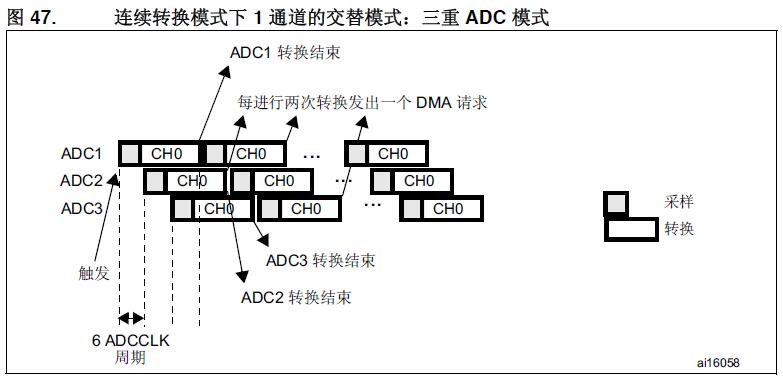

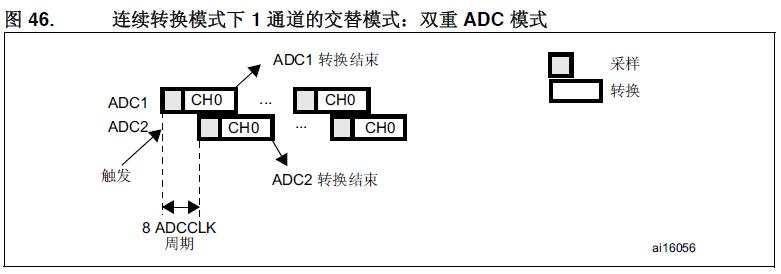

交替模式

此模式只能用於規則組(通常為一個通道)。外部觸發源來自 ADC1 的規則通道多路複用器。

雙重 ADC 模式

出現外部觸發之後:

● ADC1 立即啟動

● 經過幾個 ADC 時鐘週期延遲後 ADC2 啟動

交替模式下 2 個轉換之間的最小延遲通過 ADC_CCR 暫存器中的 DELAY 位進行配置。但 是,如果某個 ADC 的互補 ADC 仍在對其輸入進行取樣,則該 ADC 無法啟動轉換(在給定 時間內,只有一個 ADC 能夠對輸入訊號取樣)。在這種情況下,延遲時間為取樣時間 + 2 個 ADC 時鐘週期。例如,如果兩個 ADC 的 DELAY = 5 個時鐘週期,且取樣時間為 15 個時鐘 週期,則 ADC1 和 ADC2 之間的轉換延遲為 17 個時鐘週期。

如果 ADC1 和 ADC2 上的 CONT 位均置 1,則這兩個 ADC 所選規則通道會連續進行轉換。

注意:如果轉換序列中斷(例如 DMA 傳輸結束時),則必須首先通過在獨立模式下進行配置來將多 重 ADC 定序器復位(位 DUAL[4:0] = 00000),然後才可以對交替模式進行程式設計。

ADC2 生成一個 EOC 中斷之後(如果已通過 EOCIE 位使能),會生成一個 32 位 DMA 傳 輸請求(如果 ADC_CCR 暫存器中的 DMA[1:0] 位等於 0b10)。此請求首先會將儲存在 ADC_CDR 32 位暫存器高位半字中的 ADC2 轉換資料傳輸到 SRAM,然後將儲存在暫存器低位半字中的 ADC1 轉換資料傳輸到 SRAM。

三重 ADC 模式

出現外部觸發之後:

● ADC1 立即啟動

● 經過幾個 ADC 時鐘週期延遲後 ADC2 啟動

● 在 ADC2 轉換經過幾個 ADC 時鐘週期的延遲後 ADC3 啟動

交替模式下 2 個轉換之間的最小延遲通過 ADC_CCR 暫存器中的 DELAY 位進行配置。但 是,如果某個 ADC 的互補 ADC 仍在對其輸入進行取樣,則該 ADC 無法啟動轉換(在給定 時間內,只有一個 ADC 能夠對輸入訊號取樣)。在這種情況下,延遲時間為取樣時間 + 2 個 ADC 時鐘週期。例如,如果這三個 ADC 的 DELAY = 5 個時鐘週期,且取樣時間為 15 個時 鍾週期,則 ADC1、ADC2 和 ADC3 之間的轉換延遲為 17 個時鐘週期。

如果 ADC1、ADC2 和 ADC3 上的 CONT 位均置 1,則這些 ADC 所選規則通道會連續進行 轉換。

注意:如果轉換序列中斷(例如 DMA 傳輸結束時),則必須首先通過在獨立模式下進行配置來將多 重 ADC 定序器復位(位 DUAL[4:0] = 00000),然後才可以對交替模式進行程式設計。

在此模式下,每當出現 2 個可用資料項時,就會生成一個 DMA 傳輸請求(如果 ADC_CCR 暫存器中的 DMA[1:0] 位等於 0b10)。此請求首先會將儲存在 ADC_CDR 32 位暫存器低位 半字中的第一批轉換資料傳輸到 SRAM,然後將儲存在 ADC_CDR 高位半字中的第二批轉 換資料傳輸到 SRAM。具體順序如下:

● 第 1 個請求:ADC_CDR[31:0] = ADC2_DR[15:0] | ADC1_DR[15:0]

● 第 2 個請求:ADC_CDR[31:0] = ADC1_DR[15:0] | ADC3_DR[15:0]

● 第 3 個請求:ADC_CDR[31:0] = ADC3_DR[15:0] | ADC2_DR[15:0]

● 第 4 個請求:ADC_CDR[31:0] = ADC2_DR[15:0] | ADC1_DR[15:0], …

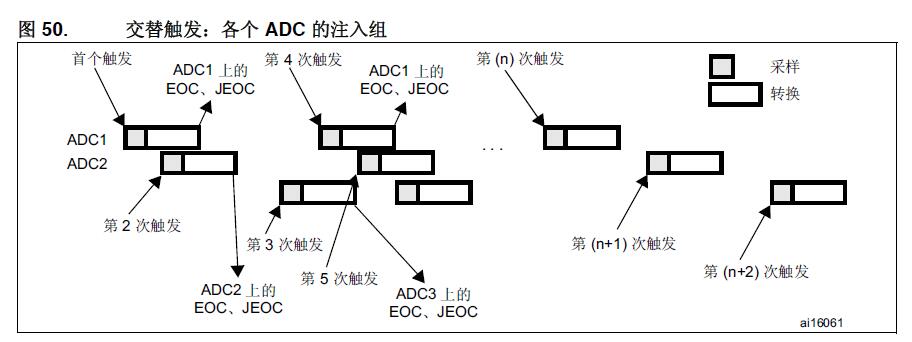

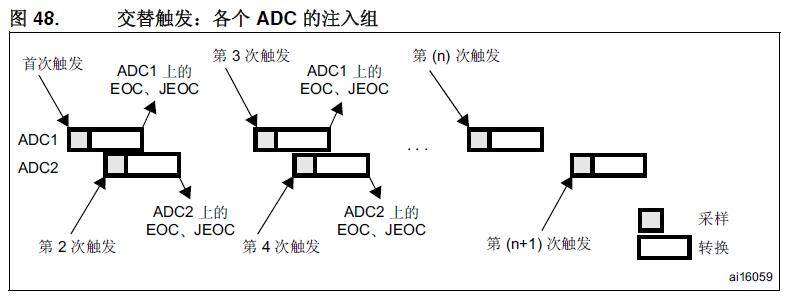

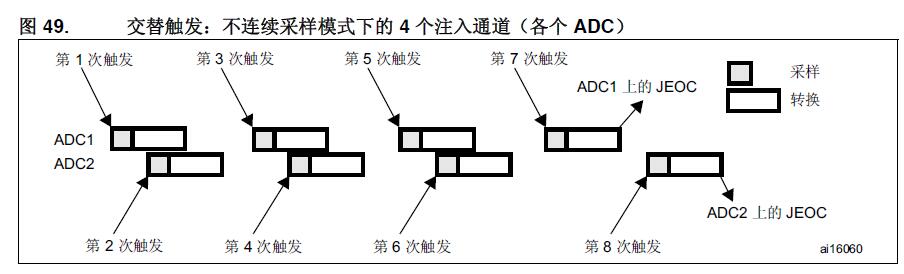

交替觸發模式

此模式只能用於注入組。外部觸發源來自 ADC1 的注入組多路複用器。

注意:規則轉換可在一個或所有 ADC 上使能。在這種情況下,規則轉換彼此之間是獨立的。當 ADC 必須執行注入轉換時,會中斷規則轉換。它會在注入轉換完成後恢復。

如果轉換序列中斷(例如 DMA 傳輸結束時),則必須首先通過在獨立模式下進行配置來將 多重 ADC 定序器復位(位 DUAL[4:0] = 00000),然後才可以對交替模式進行程式設計。

兩次觸發事件之間的時間間隔必須大於或等於 1 個 ADC 時鐘週期。同一個 ADC 上可啟動轉 換的兩個觸發事件之間的最小時間間隔與單個 ADC 模式下相同。

雙重 ADC 模式

● 發生第一次觸發時,將轉換 ADC1 中注入組的所有通道

● 發生第二次觸發時,將轉換 ADC2 中注入組的所有通道

● 以此類推

當組中的所有注入 ADC1 通道都轉換完成後,會生成一個 JEOC 中斷(如果已使能)。

當組中的所有注入 ADC2 通道都轉換完成後,會生成一個 JEOC 中斷(如果已使能)。

如果在組中的所有注入通道都完成轉換後出現另一個外部觸發,則可通過轉換組中的注入ADC1 通道來重新啟動交替觸發過程。

如果使能 ADC1 和 ADC2 的注入不連續取樣模式:

● 發生第一次觸發時,將轉換第一個注入 ADC1 通道

● 發生第二次觸發時,將轉換第一個注入 ADC2 通道

● 以此類推

當組中的所有注入 ADC1 通道都轉換完成後,會生成一個 JEOC 中斷(如果已使能)。

當組中的所有注入 ADC2 通道都轉換完成後,會生成一個 JEOC 中斷(如果已使能)。

如果注入組中的所有通道都完成轉換後出現另一個外部觸發,則會重新啟動交替觸發過程。

三重 ADC 模式

● 發生第一次觸發時,將轉換 ADC1 中注入組的所有通道。

● 發生第二次觸發時,將轉換 ADC2 中注入組的所有通道。

● 發生第三次觸發時,將轉換 ADC3 中注入組的所有通道。

● 以此類推

當組中的所有注入 ADC1 通道都轉換完成後,會生成一個 JEOC 中斷(如果已使能)。

當組中的所有注入 ADC2 通道都轉換完成後,會生成一個 JEOC 中斷(如果已使能)。

當組中的所有注入 ADC3 通道都轉換完成後,會生成一個 JEOC 中斷(如果已使能)。

如果在組中的所有注入通道都完成轉換後出現另一個外部觸發,則可通過轉換組中的注入ADC1 通道來重新啟動交替觸發過程。

混合型規則/注入同時模式

可以中斷規則組的同時轉換,然後開始注入組的同時轉換。

注意:在混合型規則/注入同時模式下,必須使用同一長度來轉換序列,或必須確保觸發之間的間隔長於 2 個序列(雙重 ADC 模式)/3 個序列(三重 ADC 模式)中的較長轉換時間。否則,當 序列較長的 ADC 完成上一次轉換時,序列較短的 ADC 可能重新開始轉換。

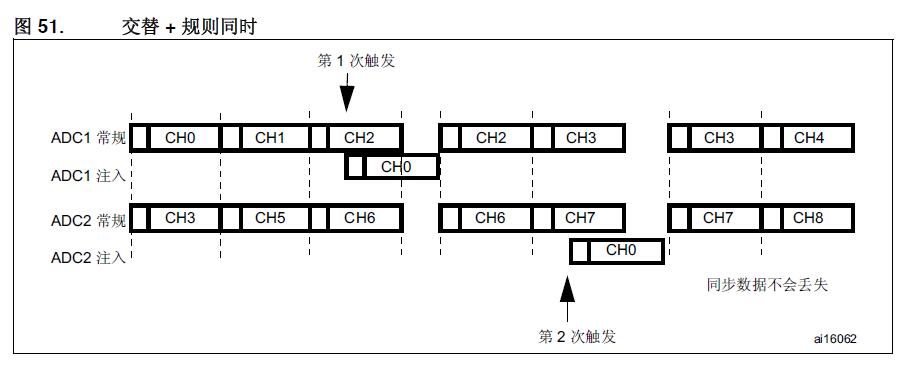

規則同時 + 交替觸發組合模式

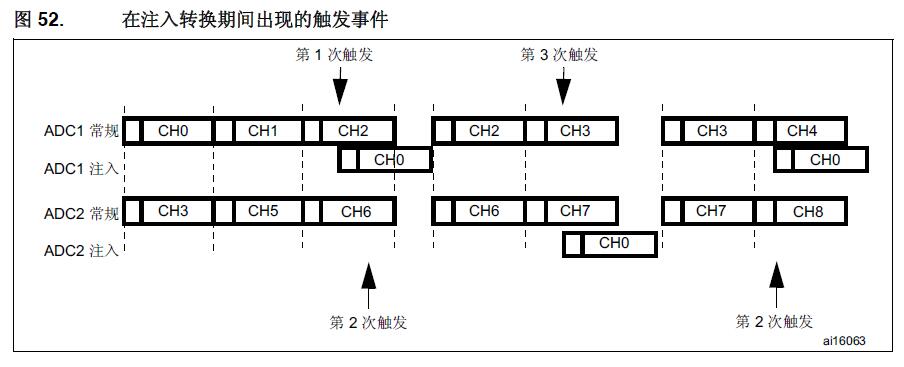

可以中斷規則組的同時轉換,然後開始注入組的交替觸發轉換。圖 51 說明了交替觸發模式 中斷同時規則轉換的行為。

注入事件後立即開始注入交替轉換。當規則轉換處於執行狀態時,為確保在注入轉換後實現同步,所有的(主/從)ADC 規則轉換均將停止,並會在注入轉換結束時得以恢復執行。

注意:在規則同時 + 交替觸發組合模式下,必須使用同一長度來轉換序列,或必須確保觸發之間的 間隔長於 2 個序列(雙重 ADC 模式)/3 個序列(三重 ADC 模式)的長轉換時間。否則,當 序列較長的 ADC 完成上一次轉換時,序列較短的 ADC 可能重新開始轉換。

如果轉換序列中斷(例如 DMA 傳輸結束時),則必須首先通過在獨立模式下進行配置來將 多重 ADC 定序器復位(位 DUAL[4:0] = 00000),然後才可以對交替模式進行程式設計。

在已導致規則轉換中斷的注入轉換期間出現的觸發將被忽略。圖 52 說明了這種情況下的行 為(第 2 次觸發被忽略)。

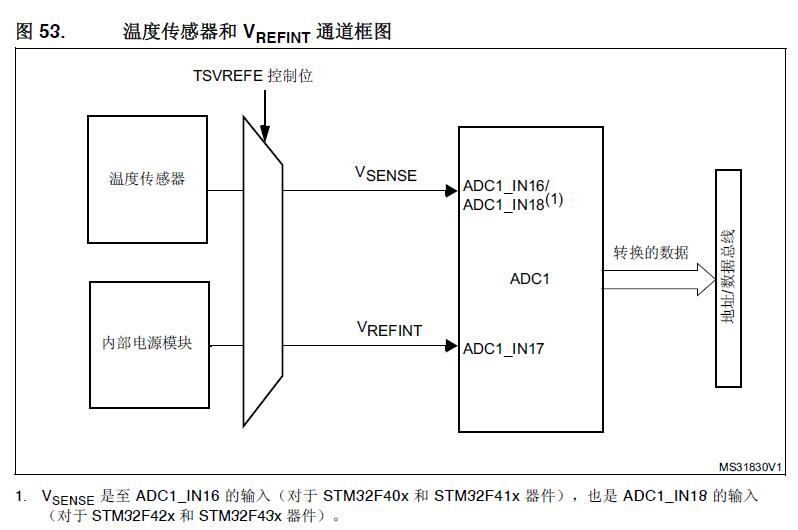

溫度感測器

溫度感測器可用於測量器件的環境溫度 (TA)。

● 對於 STM32F40x 和 STM32F41x 器件,溫度感測器內部連線到 ADC1_IN16 通道,而

ADC1 用於將感測器輸出電壓轉換為數字值。

● 對於 STM32F42x 和 STM32F43x 器件,溫度感測器內部連線到與 VBAT 共用的輸入通

道 ADC1_IN18:ADC1_IN18 用於將感測器輸出電壓或 VBAT 轉換為數字值。一次只

能選擇一個轉換(溫度感測器或 VBAT)。同時設定了溫度感測器和 VBAT 轉換時,將

只進行 VBAT 轉換。

圖 53 顯示了溫度感測器框圖。

不使用時可將感測器置於掉電模式。

注意:必須將 TSVREFE 位置 1 才能同時對兩個通道進行轉換。ADC1_IN16 或 ADC1_IN18(溫度 感測器)和 ADC1_IN17 (VREFINT)。

主要特性

● 支援的溫度範圍:—40 °C 到 125 °C

● 精度:±1.5 °C

1. VSENSE 是至 ADC1_IN16 的輸入(對於 STM32F40x 和 STM32F41x 器件),也是 ADC1_IN18 的輸入

(對於 STM32F42x 和 STM32F43x 器件)。

讀取溫度

要使用感測器,請執行以下操作:

3. 選擇 ADC1_IN16 或 ADC1_IN18 輸入通道。

4. 選擇一個取樣時間,該取樣時間要大於資料手冊中所指定的最低取樣時間。

5. 在 ADC_CCR 暫存器中將 TSVREFE 位置 1,以便將溫度感測器從掉電模式中喚醒。

6. 通過將 SWSTART 位置 1(或通過外部觸發)開始 ADC 轉換

7. 讀取 ADC 資料暫存器中生成的 VSENSE 資料

8. 使用以下公式計算溫度:

溫度(單位為 °C)= {(VSENSE — V25) / Avg_Slope} + 25

其中:

— V25 = 25 °C 時的 VSENSE 值

— Avg_Slope = 溫度與 VSENSE 曲線的平均斜率(以 mV/°C 或 μV/°C 表示)

有關 V25 和 Avg_Slope 實際值的相關資訊,請參見資料手冊中的電氣特性一節。

注意:感測器從掉電模式中喚醒需要一個啟動時間,啟動時間過後其才能正確輸出 VSENSE。ADC 在 上電後同樣需要一個啟動時間,因此,為儘可能減少延遲間,應同時將 ADON 和 TSVREFE 位置 1。

溫度感測器的輸出電壓隨溫度線性變化。由於工藝不同,該線性函式的偏移量取決於各個晶片(晶片之間的溫度變化可達 45 °C)。

內部溫度感測器更適用於對溫度變數而非絕對溫度進行測量的應用情況。如果需要讀取精確溫度,則應使用外部溫度感測器。

電池充電監視

ADC_CCR 暫存器中的 VBATE 位用於切換到電池電壓。由於 VBAT 電壓可能高於 VDDA,因 此 VBAT 引腳需要內部連線到橋接分配器,以確保 ADC 正確執行。

設定 VBATE 後,橋接器會自動使能以進行以下連線:

● 在 STM32F40xx 和 STM32F41xx 器件上將 VBAT/2 連線到 ADC1_IN18 輸入通道

● 在 STM32F42xx 和 STM32F43xx 器件上將 VBAT/4 連線到 ADC1_IN18 輸入通道

注意:VBAT 和溫度感測器連線到同一 ADC 內部通道 (ADC1_IN18)。一次只能選擇一個轉換(溫度 感測器或 VBAT)。同時使能兩個轉換時,將只進行 VBAT 轉換。

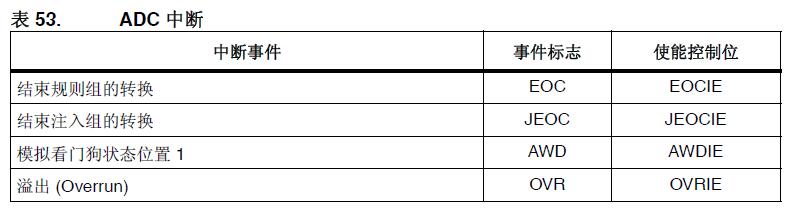

ADC 中斷

當模擬看門狗狀態位和溢位狀態位分別置 1 時,規則組和注入組在轉換結束時可能會產生中 斷。可以使用單獨的中斷使能位以實現靈活性。

ADC_SR 暫存器中存在另外兩個標誌,但這兩個標誌不存在中斷相關性:

● JSTRT(開始轉換注入組的通道)

● STRT(開始轉換規則組的通道)

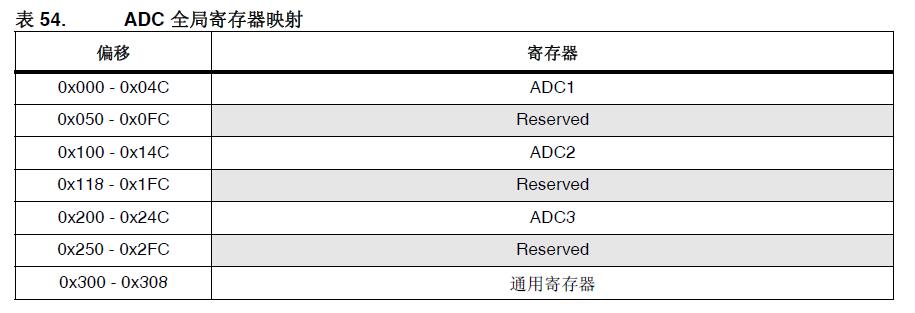

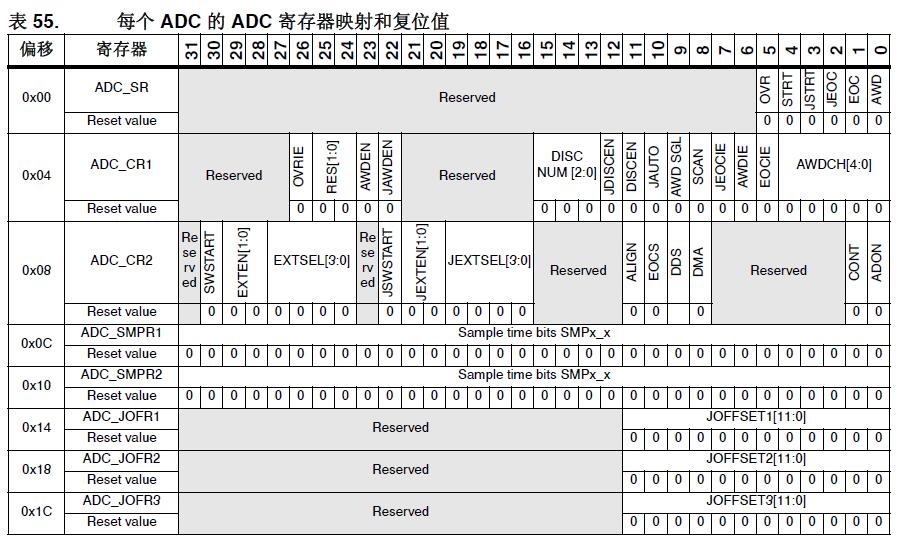

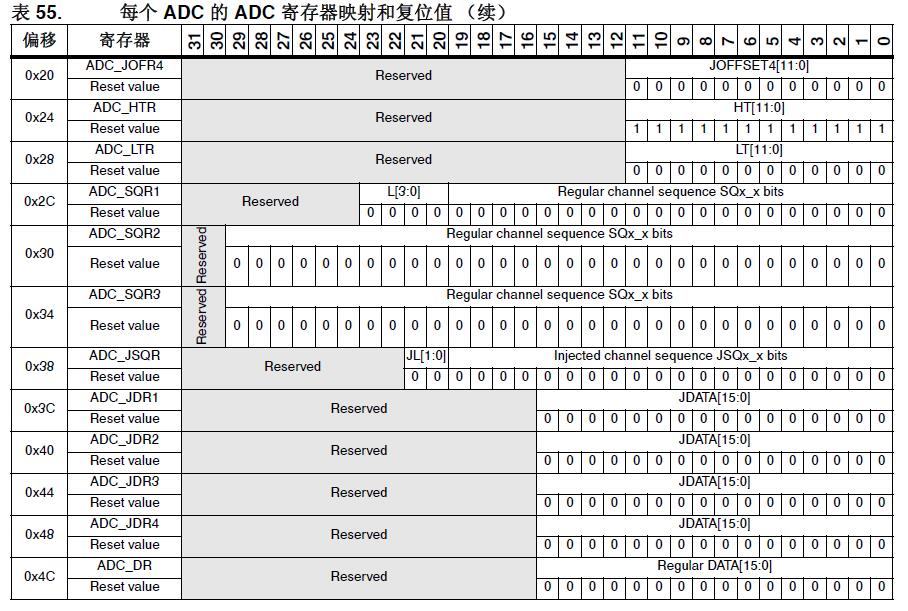

ADC暫存器對映