為什麼UART串列埠通訊要16倍過取樣資料

阿新 • • 發佈:2019-01-01

增強抗干擾是原因之一

標準UART可以選16倍取樣,也可以選64倍取樣,個人覺得應該是方便分頻設計.

標準UART的RXD前端有一個"1到0跳變檢測器",當其連續接受到8個RXD上的地電平時,該檢測器就認為RXD線出現了起始位,進入接受資料狀態.在接受狀態,接受控制器對資料位7,8,9三個脈衝取樣,並遵從三中取二的原則確定最終值.採用這一方法的根本目的還是為了增強抗干擾,提高資料傳送的可靠性,取樣訊號總是在每個接受位的中間位置,可以避開資料位兩端的邊沿失真,也可以防止接受時鐘頻率和傳送時鐘頻率不完全同步引起的誤差.

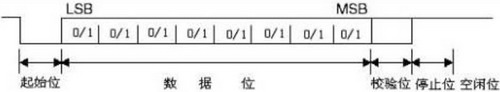

首先回顧一下非同步串列埠通訊的資料格式:

由於在空閒狀態時,傳送線為邏輯“1”狀態,而資料的傳送總是以一個起始位

關於接收器的設計最主要的一點是如何提高取樣的準確率,最好是保證取樣點處於被取樣資料的時間中間點。所以,在接收取樣時要用比資料波特率高n倍(n≥1)速率的時鐘對資料進行取樣。在本程式中用16倍波特率時鐘進行取樣。結合圖示,我們講解一下如何讓取樣時刻處於被取樣資料的時間中間點:

1. 在t1時刻若檢測到低電平,就開始對這個低電平進行連續的檢測

2. 當檢測了8個時鐘週期後,到達t2,此刻,若前面的8個週期都是低電平,則認為檢測到了起始脈衝。否則就認為是干擾,重新檢測。

3. 在檢測到起始位後,再計數16個取樣時鐘週期就到達了第一個資料位的時間中間點t3,在此刻取樣資料並進行儲存。

4. 然後再經過16個週期,就是第二個資料位的時間中間點,在此時刻進行取樣;然後,再經過16個週期,就是第三個資料位的時間中間點, 在此時刻進行取樣…..一直這樣取樣,直到把所有的資料位取樣完畢。