作業系統精髓與設計原理-計算機系統概述

本文若未註明均摘抄自《作業系統精髓與設計原理》:William Stallings著,陳向群、陳渝譯,機械工業出版社出版第六版

1 計算機系統概述

| 關鍵詞 | |||

|---|---|---|---|

| 地址暫存器 | 變址暫存器 | 區域性性 | 輔助儲存器 |

| 快取記憶體 | 輸入輸出 | 記憶體 | 段指標 |

| 快取記憶體槽 | 指令 | 多道程式設計 | 空間區域性性 |

| 中央處理單元 | 指令週期 | 處理器 | 棧 |

| 條件碼 | 指令暫存器 | 程式計數器 | 棧幀 |

| 資料暫存器 | 終端 | 可程式設計I/O | 棧指標 |

| 直接記憶體存取 | 中斷驅動I/O | 可重入過程 | 系統匯流排 |

| 命中率 | I/O模組 | 暫存器 | 時間區域性性 |

1.1 基本構成

需要權衡的瓶頸包括是記憶體讀取瓶頸,指令行並行處理瓶頸,和散熱瓶頸。而散熱瓶頸被認為是最難以跨越的。[1]

處理器的一種功能是和儲存存取交換資料,為此他通常使用CPU內部的兩個暫存器

- 儲存器地址暫存器(MAR Memory Address Register)

- 儲存器緩衝暫存器(MBR Memory Buffer Register)

同理

- 輸入輸出地址暫存器(I/O Address Register)

- 輸入輸出緩衝暫存器(I/O Buffer Register)

用於在輸入輸出模組和處理器間交換資料

1.2 處理器暫存器

- 使用者可見暫存器:可減少使用匯編語言的程式設計師對記憶體的訪問次數,對高階語言來說,由編譯器優化負責決定那些變數應該分配給暫存器,一些高階語言(如C)允許程式設計師建議編譯器把哪些變數儲存在暫存器中。

- 控制和狀態暫存器:包括IR等使用者不可見暫存器

1.2.1 使用者可見暫存器

通常包括資料暫存器,地址暫存器和條件碼暫存器

資料暫存器(Data Register):很大程度上是通用的,大多數資料操作都可以使用,除了浮點數運算使用專門的暫存器。

地址暫存器(Address Register):存放待加工使用的地址,如下面的例子:

- 變址暫存器(Index Register):通過給基址加偏移量獲得最終地址

- 段指標(Segment Pointer):儲存器被劃分成段,一個儲存器由段號和段內偏移組成,這樣的定址方式需要一個暫存器儲存段的基地址(起始地址),可能存在多個該類(段指標)暫存器。

- 棧指標(Stack Pointer):如果對使用者可見的棧進行定址,則有一個專門的暫存器指向棧頂(關鍵字:執行棧),在程式的每個過程呼叫中,處理器狀態暫存器中的資料將被轉移執行棧中,等到過程呼叫完成後再恢復回去(關鍵字:函式現場恢復),因此過程便可以自由的使用這些狀態暫存器

1.2.2 控制和狀態暫存器

有多種處理器的暫存器用於控制處理器的操作。大部分此類暫存器是使用者透明的,其中一部分可被在控制態(或稱為核心態)下執行的某些機器指令所訪問。

- 程式計數器(Program Counter):包含將取指令的地址

- 指令暫存器(Instruction Register):包含最近取的指令內容

- 程式狀態字(特殊標誌位暫存器 Program Status Word, PSW):包含狀態資訊,如中斷訪問狀態和核心/使用者態標誌。

- 條件碼(Condition code 也稱標記):為操作結果設定的位,如算數中產生正、負、零或溢位,在算數指令執行後,也會設定條件碼

1.3 指令的執行

處理器執行的程式是由一組儲存在儲存器中的指令組成。一個單一的指令需要的處理成為一個指令週期。如下圖所示,兩個步驟分別稱為取指階段和執行階段

1.3.1 取指令和執行指令

在典型的處理器中,PC(Program Counter)儲存下一次要取的指令地址,除非有其他情況,否則處理器在每次取指令後總是遞增PC,這樣下次就能取到下一條指令

graph LR

開始-->取下一條指令

取下一條指令-->執行指令

執行指令-->停止

執行指令-->取下一條指令基本指令週期

取到的指令被放置在一個被稱為IR(Intruction Register) 的處理器暫存器中,一個指令由操作碼和地址碼組成,其中操作碼將指定處理器將要執行的操作,這些操作大體可分為以下四類:

- 處理器-儲存器:資料可以從處理器傳送到儲存器,或者從儲存器傳送到處理器(快取)。

- 處理器-I/O:通過處理器和I/O模組間的資料傳送,資料可以輸出到外部裝置,或從外部裝置輸入資料

- 資料處理:處理器可以執行很多與資料相關的算數操作或邏輯操作

- 控制:某些指令可以改變執行順序,例如從149取到的某指令指示PC指標變為182,則在下一指令週期中,取指令將從182開始,而非150。

1.3.2 I/O模組

在某些情況下,允許I/O模組直接與記憶體發生資料交換,這個操作稱為直接記憶體存取(Direct Memory Access, DMA)

1.4 中斷

| 類別 | 說明 |

|---|---|

| 程式中斷 | 在某些條件下由指令執行的結果產生,如算術溢位、除數為0、試圖執行一條非法的機器指令以及訪問到使用者不允許的儲存器位置 |

| 時鐘中斷 | 有處理器內部的計時器產生,允許作業系統以一定規律執行函式 |

| I/O中斷 | 由I/O控制器產生,用於發訊號通知一個操作的正常完成或各種錯誤條件 |

| 硬體故障中斷 | 有諸如掉電或儲存器奇偶錯誤之類的故障產生 |

1.4.1 中斷和指令週期

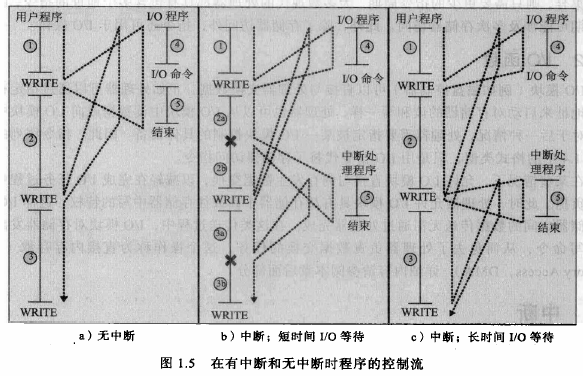

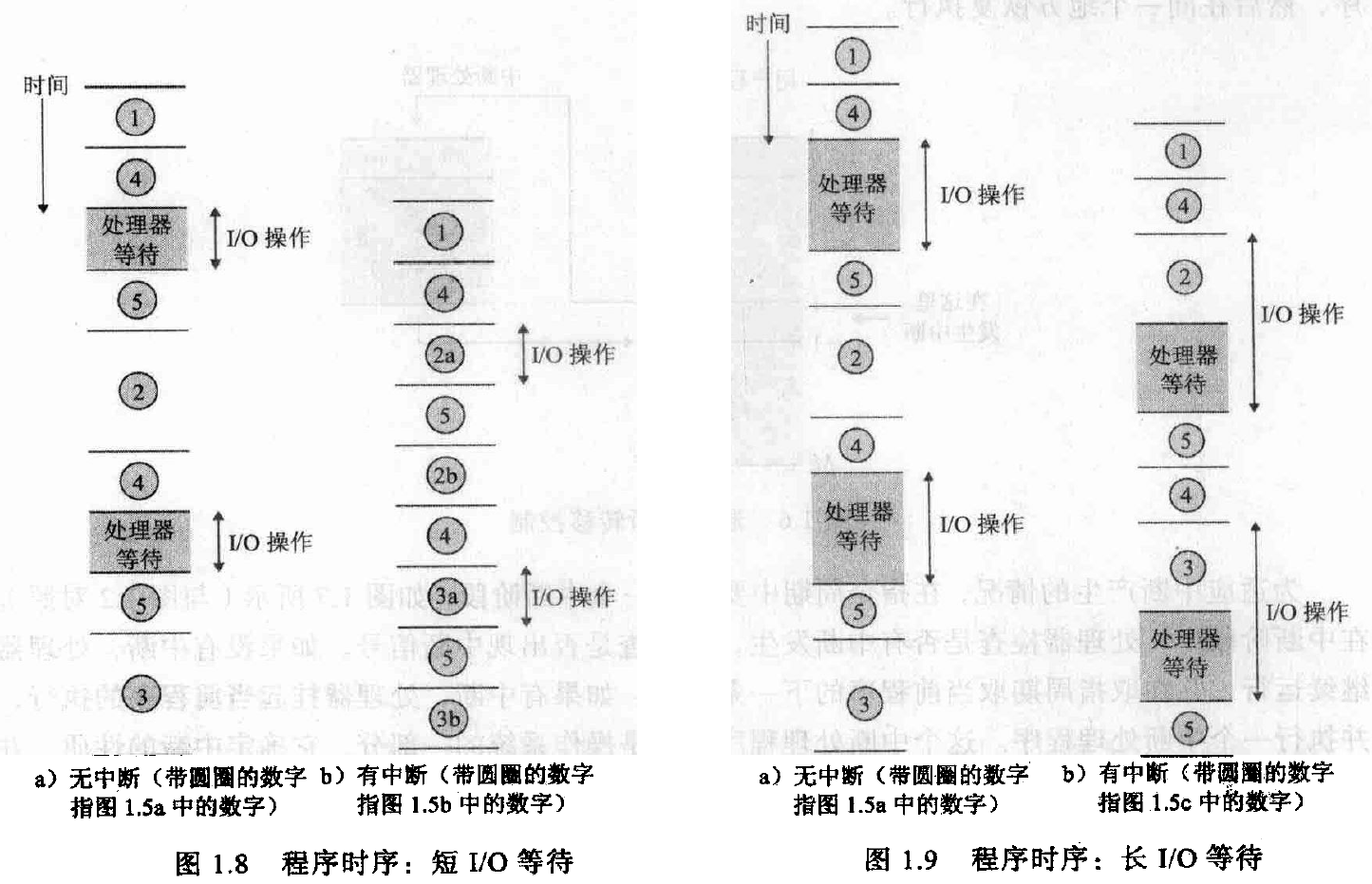

使用者程式呼叫WRITE處,設計的I/O程式僅包括準備程式碼和真正的O/I命令,在這些為數不多的幾條指令執行之後,控制返回到使用者程式繼續執行,此時外部裝置忙於從計算機儲存器接收資料並列印。而這些外部I/O操作和使用者程式中指令的繼續執行是併發的

圖1.5中用“×”表示發生中斷的點,但事實上中斷可以在主程式中的任何位置發生,而不是在一條指定的指令處

另注,如果使用者程式在由第一次呼叫產生的I/O操作完成之前就到達了第二次WRITE呼叫,則使用者程式在這一點掛起,直到前面的I/O操作完成後才繼續新的I/O操作。

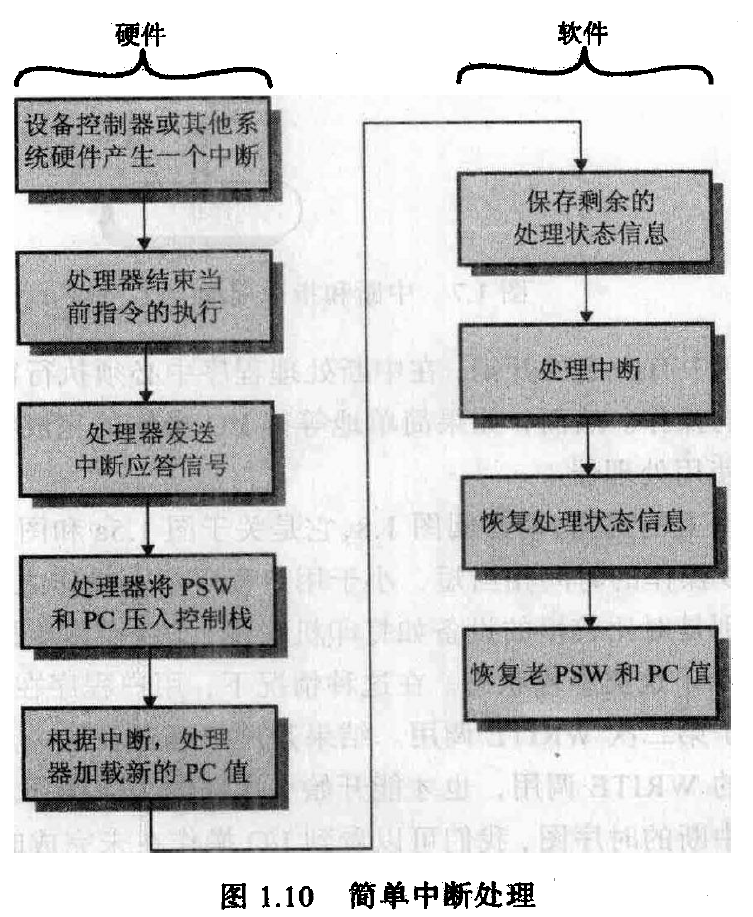

1.4.2 中斷處理

- 裝置給處理器發出一箇中斷訊號

- 處理器在響應中斷前結束當前指令的執行

- 吃力氣對終端進行測定,確定存在未響應的中斷,並給提交中斷的裝置傳送確認訊號,確認訊號允許該裝置取消它的中斷訊號。

- 處理器需要為吧控制權轉移到中斷程式做準備,首先需要儲存從中斷點恢復當前程式所需要的資訊,要求最少資訊包括程式狀態字(PSW)和儲存在程式計數器中的嚇一跳要執行的指令地址,他們被壓入系統控制棧(執行棧,見附錄1B)。在典型情況下,中斷程式一開始就在棧中儲存全部暫存器內容,其他必須儲存的狀態資訊將在第3章討論。

儲存被中斷程式的所有狀態資訊並在以後恢復這些資訊是十分重要的。

1.4.3 多箇中斷

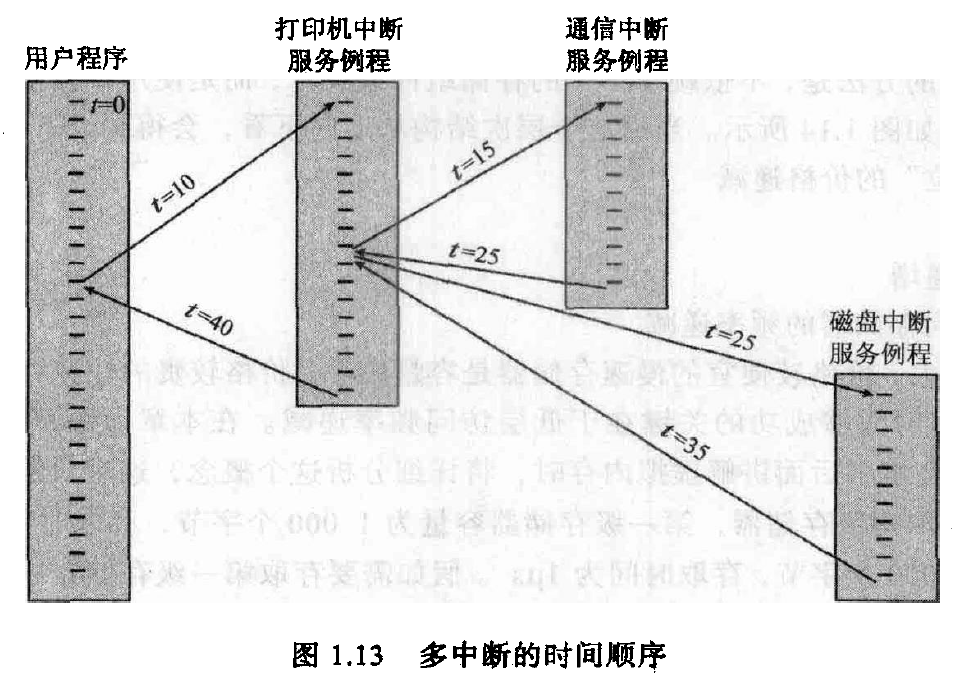

當處理多箇中斷並列的時候,比較好的方法是定義中斷優先順序,允許高優先順序的中斷打斷低優先順序的中斷處理程式的執行

1.4.4 多道程式設計

如果完成I/O操作的時間遠遠大於I/O呼叫期間使用者程式碼的執行時間,則在大部分時間處理器是空閒的,解決這個問題的方法是允許多到使用者程式同時處於活動狀態。

當一個程式被中斷是,控制權轉移給中斷處理程式,一旦中斷處理程式完成,控制權可能並不立即返回到這個使用者程式,而可能轉移到其他待執行企鵝具有更高優先順序的程式。

這種多道程式輪流執行的概念叫做多道程式設計,第二張將進一步對此進行討論。

1.5 儲存器的層次結構

計算機的儲存器設計目標可以歸納成三個目標:容量大小、速度快慢、加個高低

應當認識到,這三個目標是相互制衡的

- 儲存時間越快,每位價格越高

- 容量越大,每位加個越低

- 容量越大,速度越慢

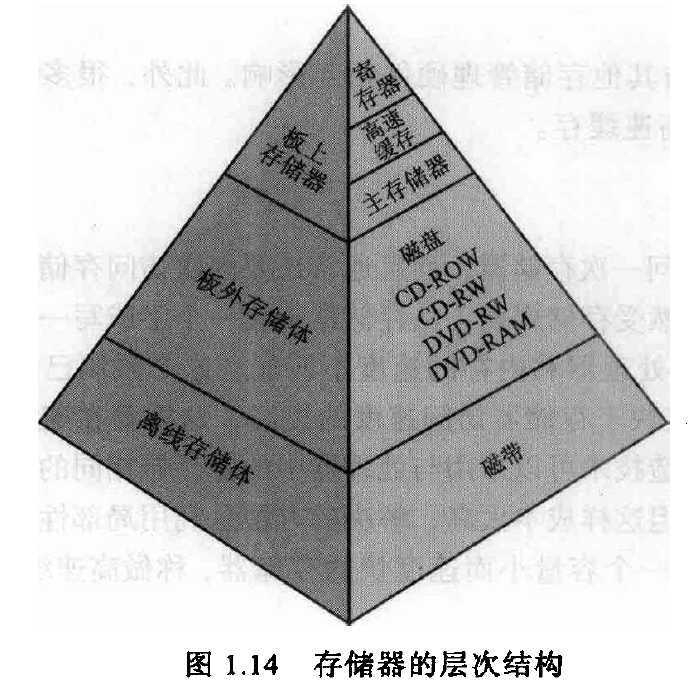

解決這和個難題的辦法是,不依賴於單一的儲存元件或技術,而是使用儲存器的層次結構。一種典型的層次結構如圖1.14所示。

這種儲存器的層次結構能夠成功的關鍵在於底層訪問頻率遞減。當地以及儲存器的存取次數所佔比例較高時,總的平均時間更接近與第一級儲存器的存取時間而不是第二級。

在程式執行期間,處理器的指令資料訪存呈現”簇”狀這也是保證處理器訪問儲存器的頻率逐層遞減的條件。典型的程式中,一旦程式進入一個迴圈或子程式執行,短時間內處理器主要訪問儲存器中固定的簇。

外部的,非易失性儲存器也稱為二級儲存器(Secondary memory)或複製儲存器(auxiliary memory),硬碟還可用作記憶體的擴充套件,即虛擬記憶體(Virtual memory),這方面內容將在第8章講述

快取記憶體通常對程式設計師透明,或者說是對處理器透明,快取記憶體用於在記憶體和處理器的暫存器之間分段移動資料,以提高資料的訪問效能,是自治的。

1.6 快取記憶體

1.6.1 動機

處理器在取指令是至少訪問一次儲存器,其速度顯著受制於儲存週期的限制,理想情況下,記憶體的構造技術可以採用與處理器中的暫存器相同的技術,但成本太高,解決辦法是利用區域性行原則,即在處理器和記憶體之間提供一個容積小而速度快的儲存器,稱作快取記憶體

1.6.2 快取記憶體原理

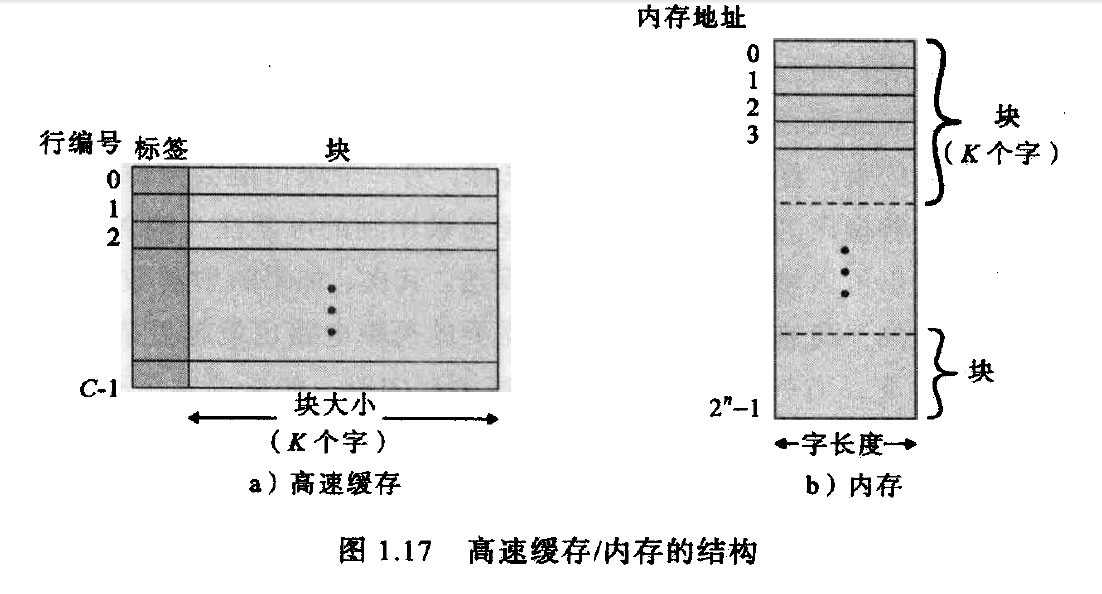

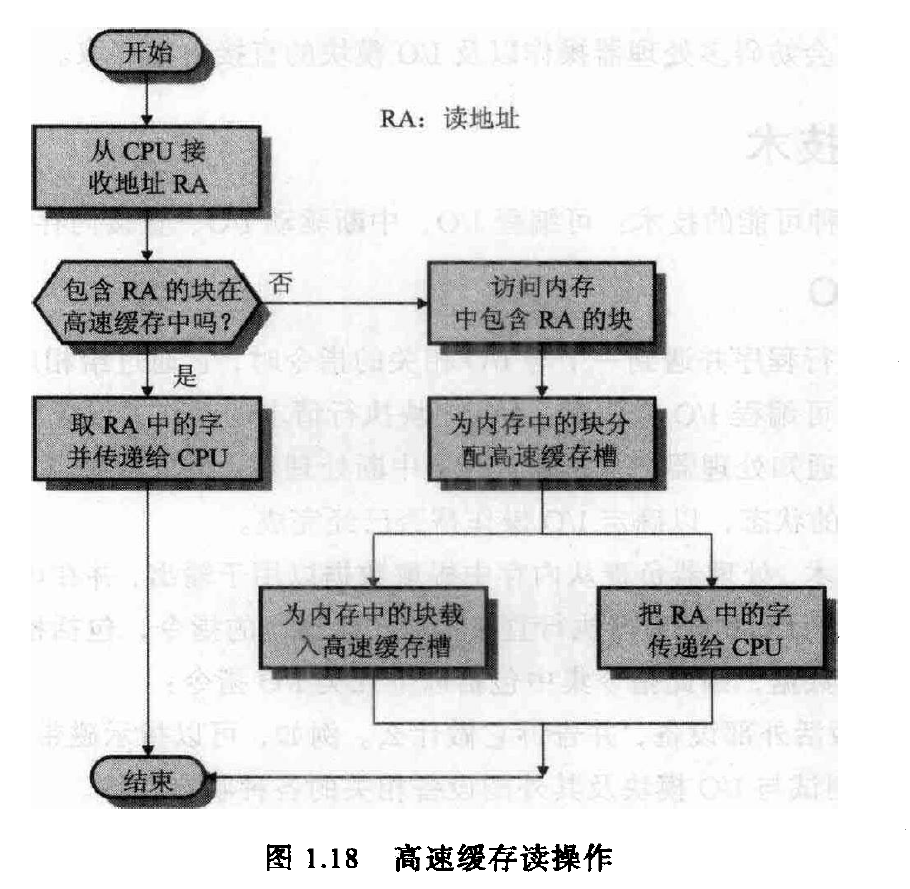

快取記憶體包含一部分記憶體資料的副本,這些副本被以包含K個字的“塊”為單位在快取記憶體和記憶體間傳輸,快取記憶體中有C個儲存槽(Slot, 也稱為Line),每個槽可以容納一個塊,由於快取記憶體的儲存槽數目遠少於儲存器中塊的數目,因此一個槽不可能唯一或永久的對應一個塊。

每個槽中都有一個標籤以表示當前儲存的是哪一個塊,標籤通常是地址中較高的若干位,表示以這些位開始的所有地址(都被包括在該塊中)。

1.6.3 快取記憶體設計

當一個新塊被讀入快取記憶體時,有對映函式確定這個塊將佔據那個快取記憶體單元,設計對映函式要考慮兩方面的約束

- 首先要儘可能減少被替換掉的塊在不久將來還會被用到的可能性,對映函式就應該變得靈活

- 其次,對映函式的複雜程度決定了確定某個指定塊是否位於快取記憶體內的功能電路將變得複雜

當一個新塊被加入到快取記憶體時,如果快取記憶體已滿,那麼替換演算法就要試圖替換在過去一段時間被使用次數最少的快取,這個策略叫做(Least-Recently-Used, LRU)演算法。

1.7 I/O通訊技術

對I/O操作有三種可能的技術:可程式設計I/O、中斷驅動I/O、直接記憶體存取(DMA)。

A1 兩級儲存器的效能特性

記憶體快取記憶體機制是計算機系統結構的一部分,他有硬體實現,通常對作業系統是不可見的。

區域性性

兩級儲存器提高效能的基礎是區域性性原理,這個原理宣告儲存器的訪問表現出簇聚性。在很長的時間內,使用的簇會發生更替,但在短時間內,處理器基本上至於儲存器中的固定的幾個簇打交道。

區域性性原理很有效,原因是:

- 除了分支和呼叫外,程式都是順序的

- 在迴圈的過程中,計算被限制在程式中很小的相鄰部分中

- 對於陣列一類的容器,連續引用==相鄰記憶體訪問

1B過程控制

控制過程中呼叫和返回最常用的技術是使用棧。

棧的實現

棧也稱作下推表或後進先出(LIFO)。一種典型的方法是,在記憶體中為棧保留一塊連續的單元,大多數時候,塊中只有一部分填充著棧元素,剩餘的部分供棧增長時使用。正確操作需要三個地址,這些地址通常儲存在處理器暫存器中

- 棧指標:永遠指向最後入棧的元素,在向棧中新增(PUSH)或刪除(POP)元素時,將+1或-1

- 棧底:保留塊中的低端

- 棧界限:保留塊中的頂端,如果棧指標超過棧界限,將發生棧溢位錯誤

過程呼叫和返回

為一次過程呼叫儲存的整個引數集合,包括返回地址,被稱為棧幀(stack frame)

可重入過程

可重入過程是指程式的程式碼的一份副本可以在同一段時間內被多個使用者共享使用。可重入過程有兩個必要特徵:

- 程式程式碼不能修改自身(執行次序無關)

- 可以被中斷(執行時間無關),由一個正在中斷的程式呼叫,再返回該過程時仍能正確執行。