GPIO 上拉下拉解釋說明

http://www.elecfans.com/pld/jiekou_zongxian_qudong/577391.html

gpio上拉下拉區別

GPIO是一顆晶片(MCU)必須具備的最基本外設功能。

GPIO通常有三種狀態:高電平、低電平和高阻態。高阻態換句話說就是斷開狀態或浮空態。因此上拉和下拉其中一個強大的理由就是為了防止輸入端懸空,使其有確定的狀態。減弱外部電流對晶片的產生的干擾。

上拉就是將不確定的訊號通過一個電阻提升為高電平,這個上拉的電阻的選擇通常有講究,通常是驅動能力和功耗的平衡,若GPIO為輸出為高電平,一般來說,上拉電阻越小,驅動能力越強,但功耗也就越大,同時還要考慮下級電路對驅動能力的要求,上拉電阻選擇的合適才能向下級電路提供足夠的電流。另外就是數位電路對高低電平都有一個門檻,以上拉電阻為例,輸出高電平自然是被拉高,但輸出低電平的時候,通常內部的開關管會被導通到地,這必須確保內部導通到地這一段之間的電阻和上拉電阻的比值足夠讓其電平處在零電平門檻之下。對頻率比較高的時候,上拉電阻和開關管漏源級之間的電容和下級電路之間的輸入電容會形成“RC延遲”,電阻越大,延遲越大。下拉電阻的選擇原理和上拉電阻是一樣的。

還有另外兩個概念:拉電流和灌電流。這兩個名詞本是為更形象的表述卻意外的讓人更加迷惑。要弄清楚這兩個概念首先必須以晶片本身為出發點,所謂的拉和灌都是相對晶片本身而言。

拉是晶片主動輸出電流,從輸出埠輸出電流 ,拉電流就是GPIO輸出高電平給負載提供的輸出電流。

灌是晶片被輸入電流,從輸出埠灌入,灌電流是輸出低電平時外部數位電路輸入的電流。

另外還有一個吸收電流的概念,吸收電流時主動吸入電流,是從輸入埠流入,即GPIO被設定為輸入狀態。 所以拉電流和灌電流通常都是指相對輸出而言。

gpio上拉好還是下拉好

首先 上下拉 是給IO一個預設的狀態 比如控制EN的話,那麼高有效的我們就下拉,低有效的話我們就上拉

而 很多IO 由於CMOS工藝問題會出現float的現象,所以不能懸空 需要PU PD。

上拉和下拉是指GPIO輸出高電位(上拉)還是低電位(下拉)。

上拉就是輸入高電平,然後接一個上拉電阻(起保護作用),知道上拉就表示該埠在預設情況下輸入為高電平。

下拉就相反了,指輸入低電平,然後接一個下拉電阻。

那麼,什麼是高電平,什麼是低電平呢?這是電路方面的知識,百度百科講的,表示不太懂。

上拉就是將不確定的訊號通過一個電阻鉗位在高電平,電阻同時起限流作用。

下拉同理。也是將不確定的訊號通過一個電阻鉗位在低電平。

不過從程式設計的角度講,

上拉就是如果沒有輸入訊號則此時I/O狀態為1,下拉相反。

具體配置為上拉還是下拉,要看電路圖。看外部有沒有上下拉電阻。

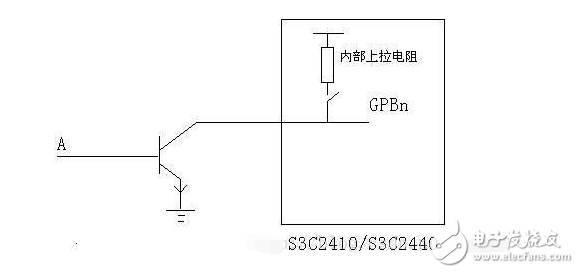

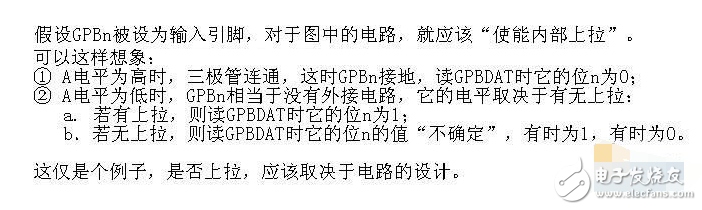

上拉暫存器是控制對應埠上拉使能的。當對應位為0時,設定對應引腳上拉使能,為1時,禁止對應引腳上拉使能。如果上拉暫存器使能,無論引腳功能暫存器如何設定(輸入,輸出,資料,中斷等),對應引腳輸出高電平。可見對應於S3C2410的GPB-BPH口內部有上拉電阻暫存器,當相應的上拉電阻使能時,對應的I/O引腳懸空時,表現出高電平。反之,表現出低電平。

上拉是一個電阻接到一個電壓,其實就是增強IO的驅動能力。下拉是一個電阻接到地,保證IO口是低電平。

主要是用在TTL電平和CMOS電平之間的相互驅動上面。TTL電平和CMOS電平的邏輯0和1的定義是不一樣的,打個比方,你的IO輸出邏輯1時電平是3.3V,而接到IO上的元件的邏輯1是5V,這時就要將這個IO接一個上拉,使該IO的邏輯1能夠和其驅動的裝置的邏輯1電平相當。具體上拉下拉電阻怎麼計算,這要看IO輸出的電流是多少,這個電流經過上下拉電阻時會產生一個壓降,一般上拉電阻接到的電源電壓減去這個壓降就是該IO可以被拉到的電平值,要求這個上拉電平值能夠達到邏輯1的下限。具體那篇文章可以在論壇裡搜尋一下。

1、一般作單鍵觸發使用時,如果IC本身沒有內接電阻,為了使單鍵維持在不被觸發的狀態或是觸發後回到原狀態,必須在IC外部另接一電阻。

2、數位電路有三種狀態:高電平、低電平、和高阻狀態,有些應用場合不希望出現高阻狀態,可以通過上拉電阻或下拉電阻的方式使處於穩定狀態,具體視設計要求而定。

3、I/O埠,有的可以設定,有的不可以設定,有的是內建,有的是需要外接,I/O埠的輸出類似與一個三極體的C,當C接通過一個電阻和電源連線在一起的時候,該電阻成為上C拉電阻,也就是說,如果該埠正常時為高電平,C通過一個電阻和地連線在一起的時候,該電阻稱為下拉電阻,使該埠平時為低電平,作用:比如,當一個接有上拉電阻的埠設為輸入狀態時,他的常態就為高電平,用於檢測低電平的輸入。

4、上拉電阻有時是用來解決匯流排驅動能力不足時提供電流的,一般說法是拉電流;下拉電阻是用來吸收電流的,也就是灌電流。比如有I2C匯流排使用會上拉一個10k的電阻。

埠選擇還應該注意埠的初始的狀態。這個狀態是系統復位時的狀態,是不受上層軟體控制的,假如選擇的埠正常是高電平有效的,那麼應該選一個系統復位時,是下拉狀態的埠。