[嵌入式]異常與中斷(上)

異常與中斷

6.1 概述

嵌入式系統中,微處理器控制I/O埠或部件的資料傳送方式有2種:程式查詢方式和中斷方式。程式查詢方式是由微處理器週期性地執行一段查詢程式來讀取I/O埠或部件中狀態暫存器的內容,並判斷其狀態,從而使微處理器與I/O埠或部件在進行資料、命令傳送時保持同步。程式查詢方式下效率非常低,因為微處理器要花費大量時間測試I/O埠或部件的狀態。並且I/O埠或部件的資料也不能得到實時地處理。

中斷方式是I/O埠或部件在完成了一個I/O操作後,產生一個訊號給微處理器,這個訊號叫做“中斷請求”,微處理器響應這個請求訊號,停止其當前的程式操作,而轉向對該I/O埠或部件進行新的讀/寫操作,特點是實時效能好。

早期的嵌入式系統只有中斷的概念,而ARM微處理器核心增加了處理器的異常模式。異常包含了中斷。

6.2 S5PV210的異常與中斷

異常是處理外部非同步事件的一種方法,當某個異常發生時,處理器將暫停正常執行的程式;在處理這個異常之前,處理器保留當前處理器狀態以便在異常處理程式結束之後恢復原來程式執行。若有兩個或更多異常同時發生,處理器將根據優先順序來處理這些異常。

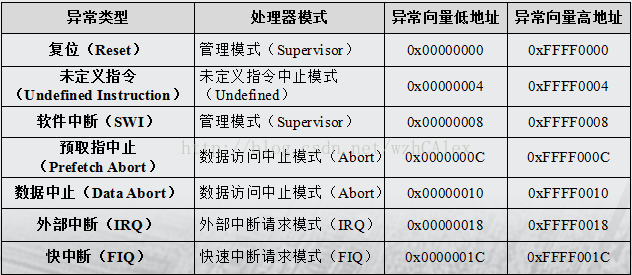

異常向量表與8種工作模式

並非一一對應。8種工作模式中的Supervisor和Abort各佔用了兩個表項,而User、System和Monitor沒有任何關聯表項,這是因為:

·User模式是程式正常執行模式,不需要進行特殊的異常處理,不是異常模式,所以它沒

有佔任何表項;

·System是特權模式,但不是異常模式,所以也不需要佔用任何表項,System與User完全

共用暫存器,同時有能力進行模式切換(修改PSR暫存器的模式位),所以它是其它特權

模式與User模式的互動橋樑;

·對於Secure Monitor模式來說,是安全模式,需要協處理器來啟動該模組,方能工作。

在上表所示的處理器異常中,和中斷有關的包括軟中斷異常、外部中斷異常與快速中斷異常。

6.3 SWI軟中斷異常

軟中斷是軟體實現的中斷,也就是程式執行時其他程式對它的中斷。軟中斷與硬中斷的區別有:

·軟中斷髮生時間由程式控制,而硬中斷髮生時間隨機;

·軟中斷是由程式呼叫發生的,而硬中斷是由外設引發的。

SWI指令

SWI指令用於產生軟中斷,從使用者模式變換到管理模式,CPSR儲存到管理模式的SPSR中。

指令格式如下:

SWI{cond} immed_24 ;immed_24為軟中斷號(服務型別)

使用SWI指令時,通常使用兩種方法進行傳遞引數:

·指令中24位立即數指定使用者請求的服務型別,引數通過通用暫存器傳遞。

mov r0,#34 ;設定子功能號為34

SWI 12 ;呼叫12號軟中斷

·指令中的24位立即數被忽略,使用者請求的服務型別有暫存器R0值決定,引數通過其他

的通用暫存器傳遞。

mov r0,#12 ;呼叫12號軟中斷

mov r1,#34 ;設定子功能號為34

SWI 0

SWI異常中斷處理程式中,取出SWI立即數的步驟為:

·首先確定引起軟中斷的SWI指令是ARM指令還是Thumb指令,這可通過對SPSR訪問得

到;

·然後取得該SWI指令的地址,這可通過訪問LR暫存器得到;

·接著讀出指令,分解出立即數。

T_bit EQU 0X20

SWI_Handler

STMFD SP!,{R0-R3,R12,LR} ;現場保護

MOV R1, SP ;得到引數指標

MRS R0,SPSR ;讀取SPSR

STMFD SP!,{R0} ;儲存SPSR

TST R0,#T_bit

LDRNEH R0,[LR,#-2] ;若是Thumb指令,讀取指令碼(16位)

BICNE R0,#0XFF00 :取得Thumb指令的8位立即數

LDREQ R0,[LR,#-4] ;若是ARM指令,讀取指令碼(32位)

BICEQ R0,#0XFF000000 ;取得ARM指令的24位立即數

; R0儲存SWI號,而R1儲存堆疊內暫存器指標

BL C_SWI_Handler ; 呼叫中斷處理函式

MSR spsr_cf, r0 ;恢復spsr

LDMFD SP!,{R0-R3,R12,PC}^ ;SWI異常中斷返回

雖然第一級SWI處理函式(完成中斷向量號的提取)必須用匯編語言完成,但具體的中斷處理函式可以使用C語言來完成。例如上面所呼叫的C_SWI_Handler控制代碼。

void C_SWI_Handler( int swi_num, int *regs )

{

switch(swi_num )

{

case 0:

regs[0] = regs[0] * regs[1];

break;

case 1:

regs[0] = regs[0] + regs[1];

break;

case 2:

regs[0] = (regs[0] * regs[1]) + (regs[2] * regs[3]);

break;

}

}

可以在彙編程式或者C程式中觸發SWI中斷,呼叫前設定所有必須的值併發出相關的SWI。例如:

MOV R0, #34

SWI 0x0

6.4 IRQ中斷與FIQ中斷

ARM微處理器有IRQ中斷和FIQ中斷兩種硬體中斷,其響應的優先順序不同。但處理步驟類似,包括:

·初始化微處理器中斷有關的暫存器,開放中斷。

·I/O埠或部件完成資料操作後產生中斷請求訊號。

·當中斷請求訊號有效時,微處理器可能處在不可中斷狀態。等微處理器允許中斷時儲存當

前狀態,停止它現行的操作並開始進行中斷源的識別。

·在識別出優先順序最高的中斷源後,微處理器轉到對應的中斷服務例程入口,並應答中斷,

I/O埠或部件收到應答訊號後,撤消其中斷請求。

·微處理器讀入或寫出資料,當中斷服務例程結束後,返回到原來的被中斷程式處繼續執行。

中斷源識別

嵌入式系統中,需要採用中斷控制方式的I/O埠或部件有許多,而通常微處理器能夠提供的中斷請求訊號線是有限的,如ARM Cortex核提供給外部的中斷請求訊號線僅有IRQ和FIQ兩根。因此,當有中斷產生時,微處理器就必須通過一定的方式識別出是哪個中斷源發來的請求訊號,以便轉向其對應的中斷服務程式例程,這就是中斷源的識別。

中斷優先順序仲裁

若嵌入式系統中由多箇中斷源,則這些中斷源必須要進行中斷優先順序的排列。所謂優先順序,指的以下兩層含義:

·若有2個及2個以上的中斷源同時提出中斷請求,微處理器先響應哪個中斷源,後響應哪

箇中斷源。

·若1箇中斷源提出中斷請求,並得到響應後,又有1箇中斷源提出中斷請求,後來的中斷

源能否中斷前一箇中斷源的中斷服務程式。

中斷控制器

S5PV210的中斷控制器由四個向量中斷控制器(VIC)組成,可以支援多達93箇中斷源以菊花鏈方式連線一起。

·支援93個向量IRQ中斷;

·固定的硬體中斷優先順序;

·可程式設計中斷優先順序;

·支援硬體中斷優先順序遮蔽;

·可程式設計中斷優先順序遮蔽;

·產生IRQ與FIQ;

·產生軟體中斷;

·測試暫存器;

·原中斷狀態;

·中斷請求狀態;

·支援對限制訪問特權模式。

6.5 中斷相關暫存器

中斷狀態暫存器VICnIRQSTATUS

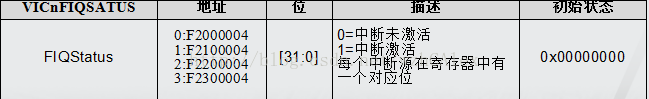

快中斷狀態暫存器VICnFIQSTATUS

中斷源未決暫存器VICnRAWINTR

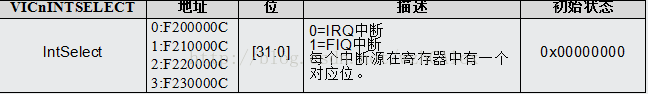

中斷選擇暫存器VICnINTSELECT

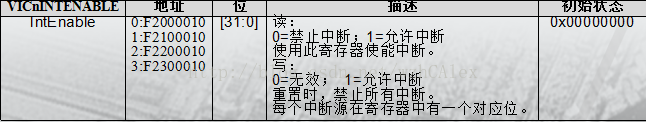

中斷使能暫存器VICnINTENABLE

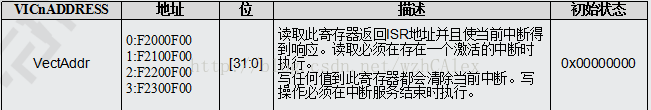

向量地址暫存器VICnADDRESS

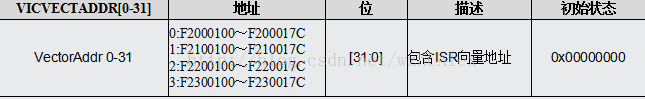

向量地址暫存器組VICnVECTADDR[0~31]

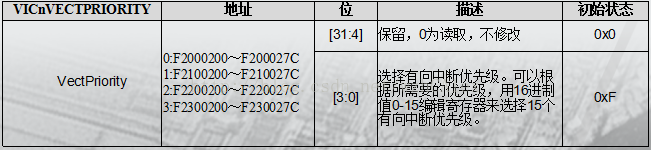

向量優先順序暫存器VICnVECTPRIORITY