FPGA硬體構成詳解

OFweek電子工程網訊 我的許多朋友都是經驗豐富的嵌入式設計工程師,但他們都是微控制器(MCU)背景,因此對於FPGA是什麼以及FPGA能做什麼只有一個模糊的概念。如果問急了,他們會說“你可以通過配置FPGA讓它做不同的事情”諸如此類的話,但他們真的不是很清楚FPGA裡面有什麼,或者如何在設計中使用FPGA。

事實上,MCU對有些任務來說是很適合的,但對其它一些任務來說可能做的並不好。舉例來說,當需要並行執行大量計算任務時,FPGA可能會讓你喜出望外。在本文中我們將討論FPGA的硬體屬性。

簡單的FPGA構造

在積體電路領域人們經常會聽到構造(fabric)這個術語,它指的是FPGA器件的底層基礎結構。(作為一個興趣點,單詞“構造”來自中世紀英語fabryke,意思是“建造的某些東西”)。下面讓我們從FPGA中的核心可程式設計構造開始吧……

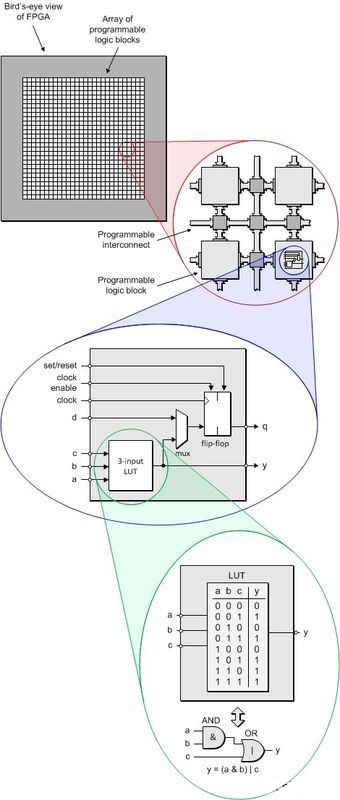

如果我們仔細觀察FPGA封裝的內部,我們將看到矽片(技術術語裸片)。可程式設計構造表現為可程式設計邏輯塊陣列,如下圖所示。如果我們用放大鏡“放大檢視”,我們可以看到這種構造由沉浸於可程式設計互連“海洋”中的許多邏輯“島”(可程式設計邏輯塊)組成。

圖1:簡單的FPGA構造。

基本FPGA可程式設計構造的一般性表示。

是啊,我確實是用自己的雙手親自創作的這幅圖片,我因此感到非常自豪呢,非常感謝你加以關注。如果我們進一步放大,我們可以看到,每個可程式設計模組都包含有許多數字功能。在這個例子中,我們可以見到一個三輸入的查詢表(LUT)、一個複用器和一個觸發器,但重要的是我們要認識到,這些功能的數量和型別對不同系列的FPGA來說是會變化的。

觸發器可以被配置(程式設計)為暫存器或鎖存器;複用器可以被配置為選擇一個到邏輯塊的輸入或LUT的輸出;LUT可以被配置為代表任何所要求的邏輯功能。

更詳細地瞭解LUT

上面所示的簡單例子包含一個三輸入的查詢表(LUT)。在實際應用中,即使最簡單的FPGA都會使用四輸入LUT,而一些更大更復雜的器件甚至會宣稱使用六、七或八輸入的LUT,但為了簡單起見,我們還是討論三輸入版本。

我們會在以後的文章中討論各種型別的FPGA實現技術。現在我們只需要知道,FPGA內部的可程式設計單元可以用反熔絲、快閃記憶體單元或SRAM記憶體單元來實現。先讓我們看一個用反熔絲技術建立的FPGA吧。這是一種一次性可程式設計(OTP)技術,這意味著一旦你程式設計了這個FPGA,它將永遠保持這個狀態而不再改變。

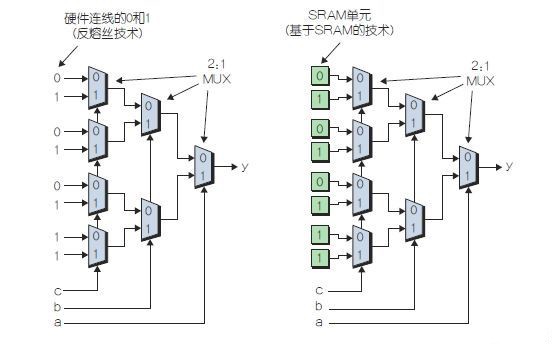

形象化介紹這種技術的最簡單方法是用下圖所示級聯的2:1複用器(MUX)。對基於反熔絲技術的FPGA來說,程式設計器件相當於通過“硬體連線”將第一組複用器的輸入連線到實現目標邏輯功能所需的正確0或1值。下圖中所示的值反映的實際結果是,我們使用這個LUT實現了前面那張圖隱含的公式y=(a & b)|c。在實際應用中,複用器可以用場效電晶體的分支“樹”來實現,但我們在這裡真的不用擔心最底層的實現細節。

圖2:輸入值經“硬體連線的”反熔絲型LUT(左),輸入從SRAM單元饋入的SRAM型LUT(右)

另外一種非常常見的FPGA實現技術是使用SRAM配置單元。同樣,我們會在以後的文章中討論更多的細節。這裡我們所要知道的僅是當電路板第一次上電時,基於SRAM的FPGA會載入配置資訊(我們可以把這個過程想像為器件的程式設計)。作為這種配置的一部分,用作LUT複用器輸入的SRAM單元會被載入進上圖所示的目標0或1值。

我沒有顯示0和1被載入進SRAM單元的那種機制,因為我不想讓問題變得複雜。出於這次討論的目的,我們真的無需擔心這種“魔術”是如何發生的。我在這裡唯一要提的事(給你考慮的空間)是—使用一種被稱為部分再配置的技術—FPGA的一部分可以發起對另一部分進行再配置(當然反過來也行)。對於具有微控制器和/或軟體背景的讀者來說,我們可以將這種技術想象為相當於自我修改程式碼的硬體。這意味著這種技術是非常非常強大的,但也會帶來很難隔離和除錯的問題。

通用的輸入和輸出

FPGA器件還包含有通用的輸入/輸出(GPIO)引腳和焊盤(圖1中沒有顯示)。通過配置單元,FPGA器件內的互連部分可以被程式設計為這樣:將器件的主輸入連線到一個或多個可程式設計邏輯塊的輸入。任何邏輯塊的輸出也可以用來驅動任何其它邏輯塊的輸入和/或FPGA器件的主輸出。另外,GPIO引腳可以被配置為支援種類廣泛的I/O標準,包括電壓、終端阻抗、擺率等。

世界上第一塊FPGA與本文中討論的架構非常類似。這塊FPGA就是賽靈思公司在1985年推出的XC2064(是用2um工藝節點製造的),它包含有8×8=64的邏輯塊陣列,每個邏輯塊包含一個四輸入LUT和其它一些簡單功能。從那以後,FPGA發展勢不可擋,正像我們看到的那樣……

更為複雜的FPGA架構

正如我們在前面說的那樣,賽靈思公司在1985年推出的第一塊FPGA—XC2064包含8×8=64的邏輯塊陣列,每個邏輯塊包含一個四輸入查詢表及其它一些簡單功能。由於它們的容量非常有限,因此早期的FPGA只用來執行一些相對簡單的任務,比如集中一些膠合邏輯,或實現基本的狀態機。然而隨著時間的推移,事情開始改變……

隨著時間的推移和工藝節點的進步,FPGA的容量和效能不斷得到提高,功耗卻不斷的下降。直到大約2006年以前廣泛使用的一直是四輸入查詢表。事實上,在寫這篇文章之時,較小的FPGA系列器件仍在使用四輸入的查詢表,但一些高階器件可能使用六、七或八輸入的查詢表。這些大傢伙可能被用作一個大的查詢表,或分裂成許多更小的功能,比如兩個四輸入的查詢表或一個三輸入一個五輸入的查詢表。在實際的高階器件中,這種可程式設計構造可以描述相當於百萬級(有時甚至千萬級)的原始邏輯閘。

如果某個邏輯功能(比方說計數器)是用FPGA的可程式設計構造實現的,那麼這個功能可以被說成“軟功能”。相比之下,如果某個功能是直接用晶片實現的,則被說成“硬功能”。(隨著這些功能變得越來越大越來越複雜,我們一般稱它們為核心)。軟核心的優勢在於,你可以讓它們做你想讓它們做的任何事。硬核心的優勢是它們佔用較少的矽片面積,具有較高的效能,並且功耗較低。最優的解決方案是混合使用軟核心(用可程式設計構造實現)和硬核心(直接用矽片實現)。這樣,除了基於查詢表的可程式設計構造外,今天的FPGA可以利用以下介紹的各種硬核心進行效能增強:

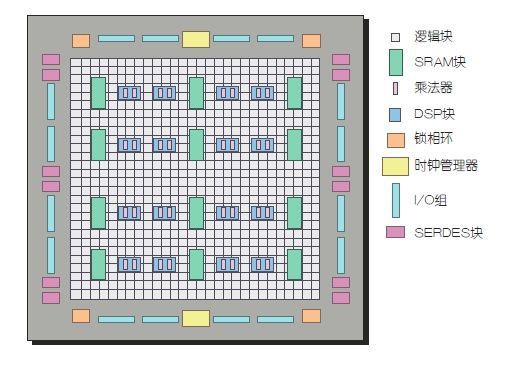

圖3:更復雜的FPGA架構。

舉例來說,該器件可能包含數千個加法器、乘法器和(DSP)功能;數兆位的片上記憶體,大量的高速序列互連(SERDES)收發器模組,以及眾多的其它功能。

帶嵌入式處理器的FPGA

這是真正讓人興奮的事情……你可以用FPGA中的普通可程式設計構造做的事情之一是,使用其中的一部分實現一個或多個軟處理器核心。當然,你可以實現不同規模的處理器。舉例來說,你可以建立一個或多個8位的處理器,加上一個或多個16位或32位的軟處理器—所有處理器都在同一器件中。

如果FPGA供應商希望提供一個佔用較少矽片面積、消耗較低功率但效能更高的處理器,解決方案是將它實現為硬核心。一個非常令人興奮的開發成果是Altera和賽靈思等公司最近推出的SoC FPGA。考慮下面所示這個例子:

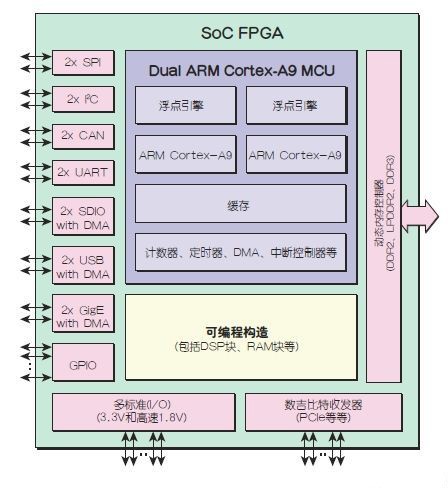

圖4:一種新的SoC FPGA

這個漂亮的小東西整合了一個完全以硬核心方式實現的雙路ARM Cortex-A9微控制器子系統(執行時鐘高達1GHz,包含浮點引擎,片上快取,計數器,定時器等),以及種類廣泛的硬核心介面功能(SPI,I2C,CAN等),還有一個硬核心的動態記憶體控制器,所有這些元件都利用大量傳統的可程式設計構造和大量的通用輸入輸出(GPIO)引腳進行了效能增強。(即將在16nm節點推出的一款SoC FPGA據稱包含四核心的64位ARM Cortex-A53處理器,雙核心32位ARM Cortex-R5實時處理器,以及一個ARM Mali-400MP圖形處理器。這些可不是你祖母時候的FPGA哦!)

傳統的嵌入式系統架構師可能將其中一個器件放置在電路板上,並將它用作傳統的高效能雙核心ARM Cortex-A9微控制器。當電路板上電時,硬微控制器核心立即啟動,並在任何可程式設計構造完成配置之前就可用了。這樣可以節省時間和精力,並讓軟體開發人員和硬體設計師同時開始開發。

一種情形是軟體開發人員捕獲他們的程式碼,在SoC FPGA的Cortex-A9處理器上執行這些程式碼,然後通過分析識別任何可能嚴重影響效能併成為瓶頸的功能。這些功能隨後可能就轉交給硬體設計工程師用可程式設計構造來實現,它們(這些功能,不是設計工程師)將使用較低的時鐘頻率提供明顯更高的效能,而且功耗更低。

前面我們說過,硬核心實現的功能(圖4所示的ARM Cortex-A9就是一種硬核心)與等效的軟核心相比具有更高的效能和更低的功耗。但現在我們又說如果在硬核心處理器上執行的軟體功能是個瓶頸,我們可以用可程式設計構造來實現,這樣它就能……你理解的沒錯,提供更高的效能和更低的功耗。