MTK平臺SPI匯流排的引數意義,重點講解的是speed和mode兩個引數的講解

解釋MTK平臺SPI匯流排引數的含義

檔案kernel-3.10/drivers/misc/mediatek/spi/mt6795/spi.c是MTK的spi控制器的驅動,具體引數的設定是在chip_config檔案中。

chip_config就是從裝置spi_device。對應的時間就是:設定的數值×9.6ns。如low_time = 10*9.6ns =96ns.,

修改:mt_spi_setup的函式中的chip_config變數的內容

chip_config->setuptime = 7,//15,cs cs 建立時間 看上圖 7*9.6ns=67.2ns chip_config->holdtime = 7,//15, cs cs 保持時間 看上圖 chip_config->high_time = 16,//6 sck clk 高電平時間 看上圖 chip_config->low_time = 17,//6 sck clk 低電平時間 看上圖 chip_config->cs_idletime = 3,//20, cs 休眠時間 看上圖 chip_config->cpol = 0, // cpol:時鐘極性選擇,為0時SPI匯流排空閒為低電平,為1時SPI匯流排空閒為高電平 chip_config->cpha = 0, // cpha: 時鐘相位選擇,為0時在SCK第一個跳變沿取樣,為1時在SCK第二個跳變沿取樣 chip_config->rx_mlsb = 1, // rx_mlsb & tx_mlsb:傳輸資料時,先從低bit傳送還是高bit傳送,1時代表先從低bit傳送 chip_config->tx_mlsb = 1, chip_config->tx_endian = 0, // 傳輸資料時,以大端模式傳輸或者小端模式傳輸,只對DMA傳輸有效,0時,代表小端模式傳輸; fifo mode為小端模式。 chip_config->rx_endian = 0, chip_config->com_mod = DMA_TRANSFER, // DMA或者fifo 傳輸

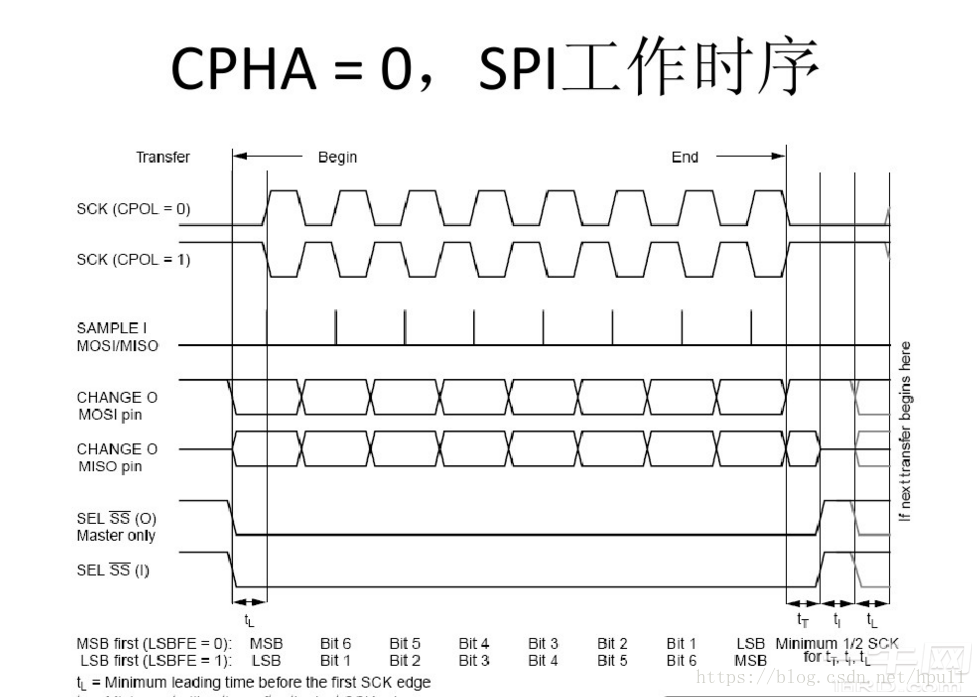

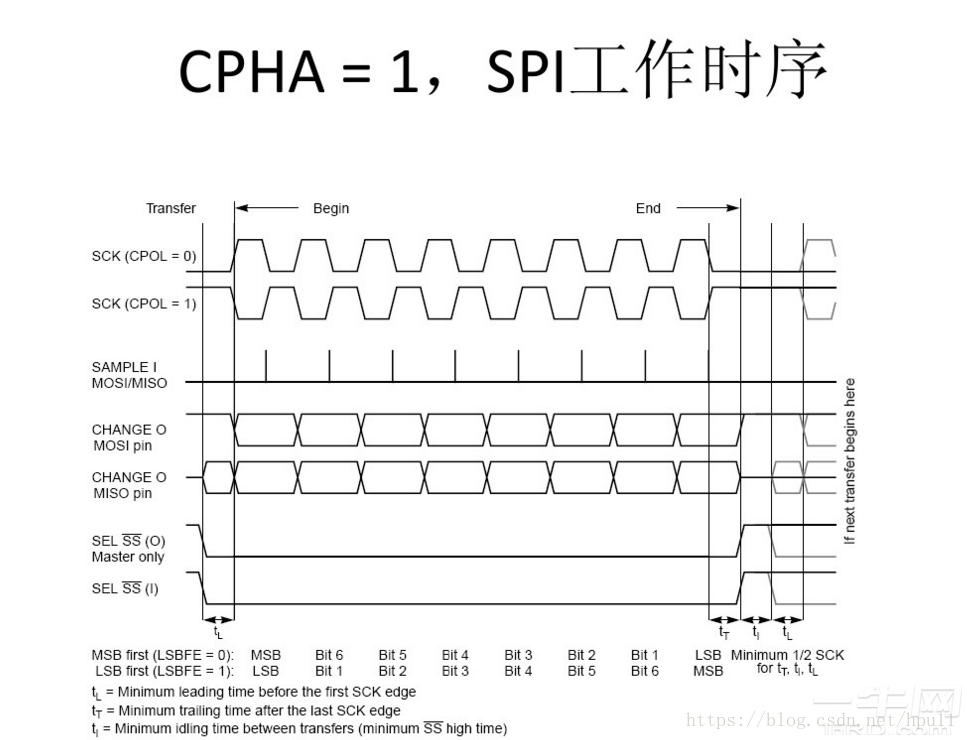

時鐘極性和相位看下圖

工作方式1:

當CPHA=0、CPOL=0時SPI匯流排工作在方式1。MISO引腳上的資料在第一個SPSCK沿跳變之前已經上線了,而 為了保證正確傳輸,MOSI引腳的MSB位必須與SPSCK的第一個邊沿同步,在SPI傳輸過程中,首先將資料上線,然後在同步時鐘訊號的上升沿 時,SPI的接收方捕捉位訊號,在時鐘訊號的一個週期結束時(下降沿),下一位資料訊號上線,再重複上述過程,直到一個位元組的8位訊號傳輸結束。

工作方式2:

當CPHA=0、CPOL=1時SPI匯流排工作在方式2。與前者唯一不同之處只是在同步時鐘訊號的下降沿時捕捉位訊號,上升沿時下一位資料上線。

工作方式3:

當CPHA=1、CPOL=0時SPI匯流排工作在方式3。MISO引腳和MOSI引腳上的資料的MSB位必須與SPSCK的 第一個邊沿同步,在SPI傳輸過程中,在同步時鐘訊號週期開始時(上升沿)資料上線,然後在同步時鐘訊號的下降沿時,SPI的接收方捕捉位訊號,在時鐘信 號的一個週期結束時(上升沿),下一位資料訊號上線,再重複上述過程,直到一個位元組的8位訊號傳輸結束。

工作方式4:

當CPHA=1、CPOL=1時SPI匯流排工作在方式4。與前者唯一不同之處只是在同步時鐘訊號的上升沿時捕捉位訊號,下降沿時下一位資料上線。