【電路】JTAG下載器研究

這是一款Xilinx FPGA的下載器。

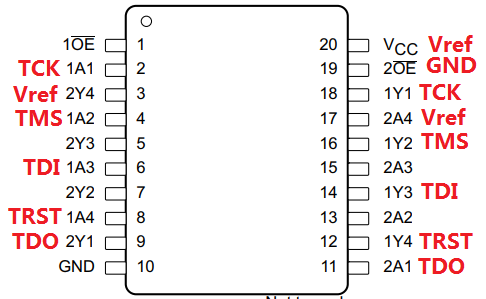

左側USB介面經過Cypress的usb控制器CY7C68013A-100AXC做介面轉換,然後跟Lattice的LFXP2-17E-6FTN256I通訊,這個小FPGA用來實現jtag協議,最後經過SN74LVC244A buffer後輸出到jtag介面。

Vref來自目標單板的jtag供電;

2OE接地,所以2A->2Y通道是預設開啟的。Vref供電經過2A4送入FPGA,一旦檢測到有電,將下載器的綠燈點亮;

1OE受FPGA控制,有個20k上拉,檢測到Vref後1OE會開啟一段時間,通過jtag查詢鏈路是否有器件;

輸出訊號TCK/TMS/TDI/TRST,在左側有20k上拉到+3.3V,在右側也有20k上拉到Vref,然後經過33歐電阻,再掛上ESD管;

假如Vref=+2.5v(非3.3v),

那麼1A側的輸入電平是3.3v的,1Y側的輸出電平是2.5v的;而2A側的輸入電平是2.5V,2Y側的輸入電平也是2.5v到FPGA。

實測是可以工作的,符合FPGA側bank電壓3.3v的LVCMOS輸入標準。

例如2A4的Vref輸入2.5v,測2Y4上的電壓2.5v,VIH>2v,正確識別高電平。

相關推薦

【電路】JTAG下載器研究

這是一款Xilinx FPGA的下載器。 左側USB介面經過Cypress的usb控制器CY7C68013A-100AXC做介面轉換,然後跟Lattice的LFXP2-17E-6FTN256I通訊,這個小FPGA用來實現jtag協議,最後經過SN74LVC244A

【Ubuntu】任務管理器loadruner

grep rexec ref con included init.d 返回 find ubun linux1 準備工作 可以通過兩種方法驗證服務器上是否配置了rstatd守護程序: ①使用rup命令,它用於報告計算機的各種統計信息,其中就包括rstatd的

【轉】如何下載安裝python

content python com 麻煩 32位 cmd 建議 zip 存儲 【轉】原文地址:http://jingyan.baidu.com/article/25648fc19f61829191fd00d4.html 1. 在python的官網下載python版本,

【電路】4線智能調速風扇

pc機 nbsp 電路 logs cnblogs .cn 引入 http image PC機內4線風扇,參考型號 貓頭鷹NF-A6x25 PWM 4根線分別是:PWM - 測速 - 12V+ - 地線(pin1) PWM拉高/懸空會全速轉,拉低停止,給占空比控速。

【十】叠代器、生成器、裝飾器和標準庫

ber 遍歷 mmu 取出 out most 例如 list char 一:叠代器 在python中,很多對象可以直接通過for語句來直接遍歷,例如:list、string、dict等等,這些被稱為可叠代對象 叠代器是一個可以I記住遍歷的位置的對象。 在python中,支持

【轉】JQuery選擇器

log fieldset radi query 選擇器 序號 html 數組 cnblogs 原址:http://www.cnblogs.com/onlys/articles/jQuery.html jQuery 的選擇器可謂之強大無比,這裏簡單地總結一下

【ElementUI】日期選擇器時間選擇範圍限制

del this 以及 ui框架 .get led () 設置 ons ElementUI是餓了麽推出的一套基於vue2.x的一個ui框架。官方文檔也很詳細,這裏做一個element-ui日期插件的補充。 官方文檔中使用picker-options屬性來限制可選擇的

【24】Python裝飾器筆記

put 訪問 img elif 分享 sse pass 源代碼 local 裝飾器定義:本職是函數,(裝飾其他函數)就是為其他函數添加附加功能。原則:1.不能修改被裝飾的函數的源代碼2.不能修改被裝飾函數的調用的方式 先來一個直觀感受 import time def tim

【轉載】Python裝飾器-----Toby Qin

callable cache __init__ spec Go 自帶 pos 發揮 date Python中的裝飾器是你進入Python大門的一道坎,不管你跨不跨過去它都在那裏。 為什麽需要裝飾器 我們假設你的程序實現了say_hello()和say_goodbye()兩個

【閱讀】烏合之眾——大眾心理研究

不同 有意 遺傳 徹底 社會 得出 差異 作用 取代 一直挺喜歡心裏學的,就買了這本《烏合之眾-大眾心理研究》。 遺傳賦予個體以及種族共同的特征,當一定數量的個體為了某項行動聚集起來,就會在這個種族特征外,出現某種新的心裏特征,這兩者的差異是相當巨大的。群體總是無

【Java】Java計時器(秒表)

sna win8 pbo tcl constant 源代碼 AS add 開始時間 https://blog.csdn.net/c_jian/article/details/50506759 應用名稱:Java計時器 用到的知識:Java GUI編程 開發環境:win8+e

【轉】WEB服務器與應用服務器的區別

由於 .net 然而 cluster scala apache servlet 位置 如何使用 https://blog.csdn.net/liupeng900605/article/details/7661406 一.簡述 WEB服務器與應用服務器的區別: 1

Tomcat學習筆記【1】--- WEB服務器、JavaEE、Tomcat背景

javascrip http .cn 目的 java log 進行 瀏覽器 靜態資源 本文主要講學習Tomcat需要知道的基礎知識。 一 Web服務器 Web服務器可以解析HTTP協議。當Web服務器接收到一個HTTP請求,會返回一個HTTP響應,例如送回一個HTML頁面。

【JVM】垃圾收集器

七、垃圾收集器 JDK7/8後,HotSpot虛擬機器所有收集器及組合(連線),如下圖: 圖中展示了7種不同分代的收集器: Serial、ParNew、Parallel Scavenge、Serial Old、Parallel Old、CMS、G1; 它們所處區域

【轉】Mac下載MySQL5.7及詳細安裝流程

來自 https://www.cnblogs.com/myxq666/p/7787744.html 一.在瀏覽器當中輸入以下地址 https://dev.mysql.com/downloads/mysql/ 二.進入以下介

【更新】免費下載百度文庫文件

如題 from Pleiades_Antares 線上下載地址: 免費下載文件地址,無需下載相應軟體! 冰點下載器 最新版本下載 無需積分就可以自由下載百度、豆丁、丁香、MBALib、道客巴巴、Book118等文庫文件,無需註冊和登入。下載的文件最終生成高清晰度的pdf格式文件。 支援

【ElementUI】日期選擇器時間選擇範圍限制,只能選今天之前的時間,或者是隻能選今天之後的時間。今天是否可以選

<el-date-picker v-model="value1" type="date" placeholder="選擇日期" :picker-options="pickerOptions0"> </el-date-picke

【ICS2015】簡易排程器之CPU_state

https://nju-ics.gitbooks.io/ics2015-programming-assignment/1.3.1.html 雖然明確提示,要使用匿名union,但是具體該怎麼表示,還是費了一番神。最開始寫出來是這樣的: typedef struct { unio

【python】@property裝飾器

Python內建的@property裝飾器可以把類的方法偽裝成屬性呼叫的方式。也就是本來是Foo.func()的呼叫方法,變成Foo.func的方式。在很多場合下,這是一種非常有用的機制。 class People: def __init__(self, name, age):

【ROS】rospy 釋出器和訂閱器(Publisher and Subscriber)

rospy L1: Publisher and Subscriber 參考(http://wiki.ros.org/rospy_tutorials/Tutorials/WritingPublisherSubscriber) 1 準備開發環境 1.1 建立功能包beginner_tutor