ZYNQ學習之pl和ps介面

1、PL和PS的介面型別總共有兩種:

(1)功能介面:AXI、EMIO、中斷、DMA流控制、時鐘除錯介面。

(2)配置介面:PCAP、SEU、配置狀態訊號和Program/Done/Init訊號。這些訊號連線到PL內配置模組的固定邏輯上,給PS提供對PL的控制能力。

2、AXI匯流排:AXI (Advanced eXtensible Interface)本是由ARM公司提出的一種匯流排協議。用於PL和PS之間的通訊。

匯流排:是一組傳輸通道,是各種邏輯器件構成的傳輸資料的通道,一般由由資料線、地址線、控制線等構成。

介面:是一種連線標準,又常常被稱之為物理介面。

協議:就是傳輸資料的規則

(1)AXI匯流排:在ZYNQ中有支援三種AXI匯流排

AXI4:(For high-performance memory-mapped requirements.)主要面向高效能地址對映通訊的需求,是面向地址對映的介面,允許最大256輪的資料突發傳輸;

AXI4-Lite:(For simple, low-throughput memory-mapped communication )是一個輕量級的地址對映單次傳輸介面,佔用很少的邏輯單元。

AXI4-Stream:(For high-speed streaming data.)面向高速流資料傳輸;去掉了地址項,允許無限制的資料突發傳輸規模。

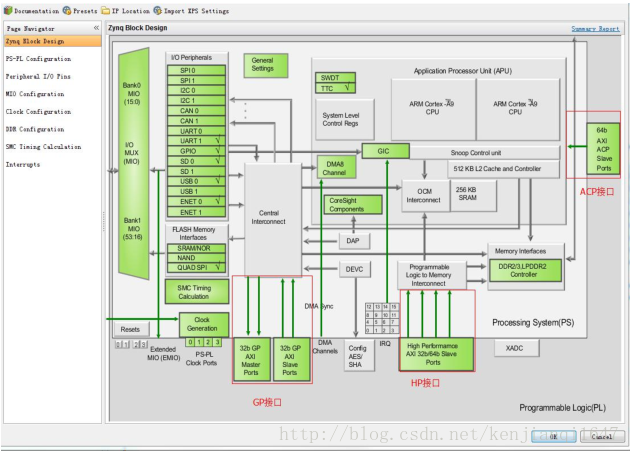

(2)zynq的AXI介面共有9個,包括如下型別:

1)AXI_ACP介面:加速器一致性介面,用來管理DMA之類不帶緩衝的AXI外設,PS端是Slave介面。

通過該介面PL端可以直接訪問PS部分cache,故PL邏輯可以直接從cache中拿到CPU的計算結果,同時也可以進一步第一時間將計算的邏輯加速運算的結果送至CPU。

2)AXI_HP介面:高效能/頻寬的AXI3.0標準介面,共有4個,PL模組作為主裝置連線。。主要用於PL訪問PS上的儲存器(DDR和On-Chip RAM)。

AXI-HP介面主要是為了PL訪問PS上的儲存器(DDR和on-chip RAM)而設計的高速資料通路。AXI-HP埠分為兩部分一部分直接和PL相連,另一部分連線到AXI interconnect。例如視訊處理時,高清的影象有FPGA直接採集處理,然後通過AXI-HP介面將資料傳輸到DDR中,供APU完成進一步影象處理。

3)AXI_GP介面:通用AXI介面,共有4個,包括兩個32位主裝置介面和兩個32位從裝置介面。

(3)AXI協議

AXI匯流排協議的兩端可以分為分為主(master)、從(slave)兩端,他們之間一般需要通過一個AXI Interconnect相連線,作用是提供將一個或多個AXI主裝置連線到一個或多個AXI從裝置的一種交換機制。AXI Interconnect的主要作用是,當存在多個主機以及從機器時,AXIInterconnect負責將它們聯絡並管理起來。由於AXI支援亂序傳送,亂序傳送需要主機的ID訊號支撐,而不同的主機發送的ID可能相同,而AXI Interconnect解決了這一問題,他會對不同主機的ID訊號進行處理讓ID變得唯一。

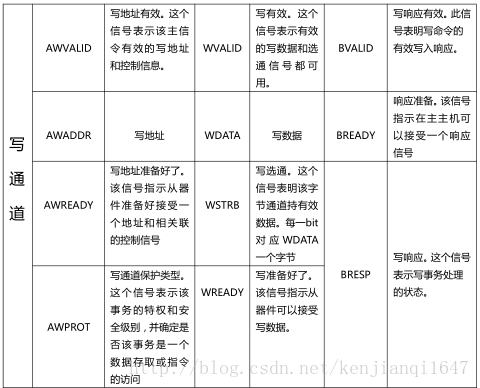

(4)AXI協議之握手協議

AXI4 所採用的是一種 READY,VALID 握手通訊機制,簡單來說主從雙方進行資料通訊前,有一個握手的過程。傳輸源產生 VLAID 訊號來指明何時資料或控制資訊有效。而目地源產生 READY 訊號來指明已經準備好接受資料或控制資訊。傳輸發生在 VALID和 READY 訊號同時為高的時候。VALID 和 READY 訊號的出現有三種關係。

1) VALID 先變高 READY 後變高

2) READY 先變高 VALID 後變高

3) VALID 和 READY 訊號同時變高

3、 AXI4-Lite 詳解

(1)先要自定義一個AXI-Lite的IP,新建工程之後,選擇,選單欄->Tools->Creat and Package IP。

(2)next - 選擇Create AXI4 Peripheral,然後Next - 預設,選擇Next - 這裡介面型別選擇Lite,選擇Next - 選擇Edit IP,點選Finish - 此後,Vivado會新建一個工程,專門編輯該IP,通過該工程,我們就可以看到Vivado為我們生成的AXI-Lite的操作原始碼。

(3)程式碼分析: