計組—快取Cache

快取

通過大量統計發現了一個訪問規律:程式對儲存空間90%的訪問侷限於儲存空間的10%的區域中,另外10%的訪問則分佈在儲存空間的90%區域中。(即:儲存器10%的儲存空間是高頻訪問區,90%的儲存空間是低頻訪問區)

計算機程式對儲存器的訪問有兩種侷限性規律:

1.時間侷限性:

如果一個儲存單元被訪問,則可能這個儲存單元很快再次被訪問。

2.空間侷限性:

如果一個儲存單元被訪問,則它臨近的儲存單元可能很快被訪問。

cache的功能

早期的計算機只有主存及外存,沒有cache,因為cpu速度不斷提高,為了滿足cpu和儲存器之間的速度差異,採用了cache技術。

cache是介於cpu和主存之間的小容量儲存器,存取速度比主存快。能高速的向cpu提供指令和資料,加快程式的執行速度,它的內容為主存一部分內容的副本。當儲存器接到有關讀取指令時,現在cache中查詢此資訊是否存在,若有則不經主存直接從cache中取出,否則直接從主存取出,同時寫入cache,以備再次使用。

cache目的是為了解決cpu和主存速度不匹配的技術。cache用來存放程式中當前最活躍的程式和資料。

總的原則:儘量使計算機的存取速度接近cache,容量為記憶體大小。

cache的基本原理

cpu與cache之間的資料交換是以字位單位。而cache與主存之間的資料交換是以塊為單位,一個塊由若干定長字組成。如下圖

當cpu讀取主存中一個字時,便發出此字的地址到cache和主存,此時cache控制邏輯依據地址判斷此字當前是否在cache中,若是,此字立即傳送給cpu;若非,則用主存讀取週期把此字從主存讀出送到cpu,與此同時,把含有這個字的整個資料庫從主存讀出送到cache中。

cache的命中率

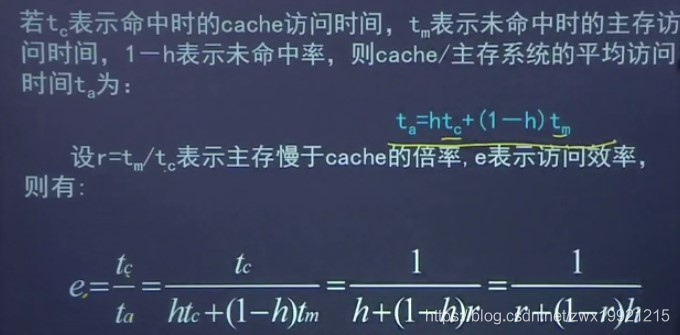

增加cache的目的。就是在效能上使主存的平均讀出時間儘可能接近cache的讀出時間。因此,cache的命中率應儘量接近於1(100%)。由於程式訪問的侷限性,這是可能的。在一個程式執行期間,設Nc表示cache完成存取的總次數,Nm表示主存完成存取的總次數,h定義為命中率,則有

主存與cache的地址對映

cache的容量很小,他儲存的內容只是主存內容的一個子集,且cache與主存的資料交換是以塊為單位。

cpu指令對對儲存器進行讀寫時,指令中的地址是記憶體系統中儲存器的地址即大地址

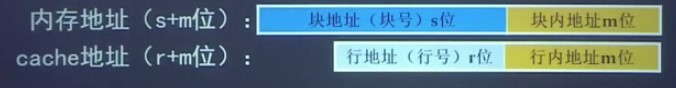

cache的資料塊稱為行(L),設cache共有2^r行,則行地址(行號)有r

主存的資料塊稱為塊(B),設主存有2^s塊,則塊地址(塊號)有s位;

注:行的容量=塊的容量

每個塊(行)由若干連續的字(W)組成,字時cpu訪問儲存器的單位。

若一個塊(行)有2^m個字,即1塊(行)=2^m字,則塊(行)內字地址有m位。

所以,cache的地址位數 = r + m (位),即行地址+字地址

記憶體地址= s + m(位),即塊地址+字地址

顯然:由於記憶體容量大於cache容量,即記憶體塊地址大於cache行地址,所以記憶體地址要大於cache地址

主存中的一個塊的地址(塊號)與塊的內容一起存於cache的行中,其中塊地址存於cache行的標記部分中

地址對映即是應用某種方法把主存地址定位到cache中;當cpu訪問儲存器時,它所給的一個字的記憶體地址會自動變成cache的地址,由於這個變換過程是用硬體實現的,因此地址變換過程速度非常快,軟體人員絲毫感覺不到cache的存在。這種特性稱為cache的透明性。

地址對映方式有全相聯方式、直接方式和組相聯方式三種 。

1.全相聯方式

主存中的一個塊的地址(塊號)與塊的內容一起存於cache的行中,其中塊地址存於cache行的標記部分中。全相聯對映方式是指主存的一個塊直接拷貝到cache中的任意一行上,非常靈活。

優點:衝突概率小,cache的利用高。

缺點:比較器電路難於實現,適合小容量cache採用。(因為在定位cache行的時候需要將塊地址與cache中的每一行的行號即標記位進行比較,找出命中的那一行,然後對命中的行進行字地址的查詢,如果找到則直接取出,否則就直接去主存讀取)

全相聯對映主存地址的劃分:主存總容量64k=2^6*2^10=2^16=65536,共有256=2^8個塊,所以每個塊大小為65536/256=256=2^8即每個塊大小為2^8,即主存地址=塊號地址8位和快內字地址8位組成,共16位;

即全相聯對映方式中主存地址中對應的塊號對應於cache中的標記位.

2.直接對映方式

一個主存的塊只能拷貝到cache中一個特定行位置上去(通過函式對映)

cache的行號 i 與主存的塊號 j 有如下的函式關係(取餘數):

i=j mod m (m為cache中的總行數)

優點:硬體簡單,成本低

缺點:每個主存塊只有一個固定的行位置可存放,容易產生衝突。因此適合大容量cache採用

直接對映主存地址的劃分:

說明:主存容量為64K=2^16即記憶體總共16位地址,低8位塊內字地址,高8位塊號(其中高8位塊號中,低3位為cache行號,高5位位標記位)

查詢過程:首先通過行號定位cache中的行位置,然後進行標記位的比較,最後通過字地址查詢值

3.組相聯對映方式

這種方式是前兩種方式的折中方案。它將m行cache分成u組,每組v行,主存塊存放到哪個組是固定的(直接對映方式),至於存到該組的哪一行是靈活的(全相聯對映方式 ),即有如下函式關係:(m 為cache總行數,j 為記憶體塊號,q為cache組號)

m = u * v

q= j mod u

(每組幾行就叫幾路組相聯,例如4組,每組兩行則叫2路組相聯)

組相聯對映主存地址的劃分:

說明:記憶體總共16位,其中低8位為字地址,高8位為快號(其中高8位塊號中,低2位cache組號,高6位為標記位)

查詢過程:首先通過組號定位到cache所屬組,然後比較對應的標記位,最後通過字地址查詢值

替換策略

cache工作原理要求它儘量儲存最新資料,必然存在將有用的資訊從主存調進cache中,這樣就產生替換。

對於直接對映cache來說,只要把此特定位置上的原主存塊替換即可;對於全相聯和組相聯cache,就要從允許存放新主存塊的若干特定行中選取一行換出。常用的替換演算法有如下4中。

cache的寫操作策略

1.寫回法(write back,回寫法)

當cpu寫cache命中時,只修改cache的內容,而不立即寫入主存,只有當此行(塊)被替換時才寫回主存。這種方法減少了訪問主存的次數,但是存在不一致性的隱患。實現這種方法時,每個cache行必須配置一個修改位,以反映此行是否被cpu修改過。

2.全寫法(write through,寫直達法)

當寫cache命中時,cache與主存同時發生寫修改,因而較好的維護了cache與主存的內容一致性。

當寫cache未命中時,直接向主存進行寫入。cache中每行無需設定一個修改位以及相應的判斷邏輯。此時是否修將改過的主存塊調入cache,有兩種方法:一種是調入cache,並分配一行;另一種是不調入cache。

缺點是降低了cache的功效。

3.寫一次法

基於寫回法並結合全寫法的寫策略,寫命中與寫未命中的處理方法與寫回法基本相同,只是第一次寫命中時要同時寫入主存,這便於維護系統全部cache的一致性。