Xilinx IP核使用(一)--FIFO

今天在將SRIO的資料存入FIFO後,然後把FIFO中的資料不斷送入FFT進行運算時,對於幾個控制訊號總產生問題。所以單獨對FIFO進行了模擬。原來感覺FIFO的幾個引數埠一目瞭然啊,還需要什麼深入瞭解嗎,在實驗發生問題才知道當時的想法多麼幼稚啊。

下面對xilixn FIFO核進行下簡單說明,配上模擬時序圖和原始碼,描述的還是比較清晰的。希望對和我一樣剛接觸FPGA不久的同學能有一點點幫助^_^

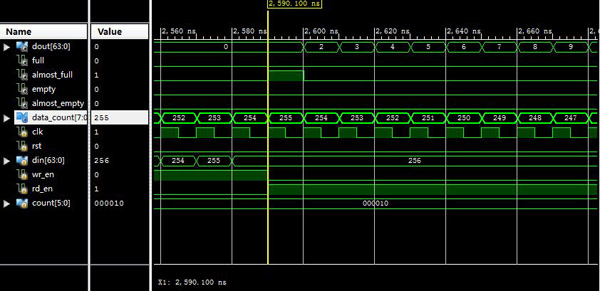

這個模擬的功能是要實現向FIFO256存入1到256個數,再將1-256讀出。注意這裡選的是FULL FLAGS RESET VALUE OF 1

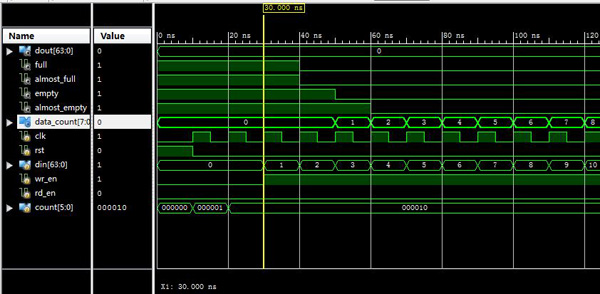

這是我想當然的模擬結果:這裡可以看到資料1丟失了,第一個讀出的資料是2。再看圖1的data_count,這裡先說下data_count的含義,當前時鐘進行寫操作,則下一時鐘data_count加1,當前時鐘進行讀操作,則下一時鐘data_count減1。因此由圖隱約可以知道為什麼資料1丟失了。

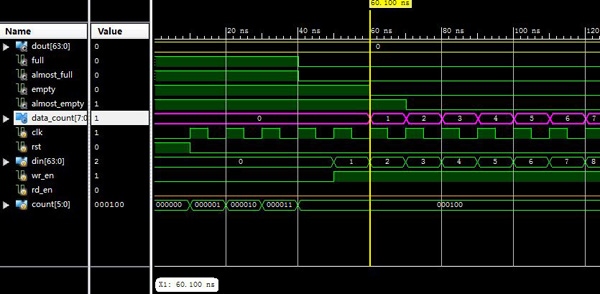

查看了下XILIXN FIFO的官方文件,說在進行寫復位後,要延遲3個時鐘週期才能進行寫操作。因此我在寫復位以後,通過count引入了3個時鐘的延遲,如下圖,發現數據沒有發生的丟失的情況了。

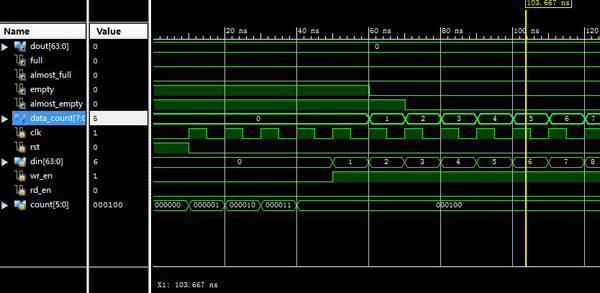

FIFO核非常好用,在讀操作的時候,我們可以通過data_count來知道還有多少個數據將要讀出,這對於後面的FFT引數控制很關鍵。當我加上FFT模組時,又出問題了,上面寫復位的FULL高電平對訊號的控制產生了的影響,即資料並沒有傳入FIFO,FULL就已經拉高了。重新回到FIFO文件,看到了答案FULL FLAGS RESET VALUE OF 0,在選了這個選項後,非同步寫復位將用最少的時間來完成。話不多說看模擬圖一目瞭然。

來源:兔美醬的部落格

相關推薦

Xilinx IP核使用(一)--FIFO

今天在將SRIO的資料存入FIFO後,然後把FIFO中的資料不斷送入FFT進行運算時,對於幾個控制訊號總產生問題。所以單獨對FIFO進行了模擬。原來感覺FIFO的幾個引數埠一目瞭然啊,還需要什麼深入瞭解嗎,在實驗發生問題才知道當時的想法多麼幼稚啊。 下面對xilixn

xilinx DMA IP核(一) —— 文檔閱讀

p s 傳輸 rect 圖片 -a wid width 清除 延遲 本筆記不記錄DMA的Scatter/Gather特性。DMA上有三種總線:AXI4-LIte(對寄存器進行配置),AXI4-Memory Map(用於與內存交互)和AXI4 Stream(用於與外設交互

使用Xilinx FIFO IP核的總結(一)

FIFO IP核的總結(一) 第一次使用Vivado中的FIFO generator,同步FIFO的常用埠也就10個左右: CLK

鎖相環PLL(一)Xilinx PLL IP核使用方法

新建IP核檔案 如圖所示,在“Design à Implementation”下的任意空白處單擊滑鼠右鍵,彈出選單中選擇“New Source …”。 在彈出的“New Source Wizard à Select Source Type”下,如圖所示,選擇檔案

IP核之初——FIFO

規範 初學者 傳輸 分享 png 初學 架構 人的 內部 本文設計思路源自明德揚至簡設計法。在之前的幾篇博文中,由於設計比較簡單,所有的功能都是用verilogHDL代碼編寫實現的。我們要學會站在巨人的肩膀上,這時候就該IP核登場了! 說白了,IP核就是別人做好了的

Xilinx DDR3 IP核使用問題匯總(持續更新)和感悟

amp per uid gravity 流程 vhdl ade 官方 vhd 一度因為DDR3的IP核使用而發狂。 後來因為解決問題,得一感悟。後面此貼會完整講述ddr3 ip的使用。(XILINX K7) 感悟:對於有供應商支持的產品,遇到問題找官方的流程。按照官方的指導

IP核之初——FIFO添加以太網MAC頭部

準備 說明 bar 成了 別人 實現 mac地址 第一個 scale 說白了,IP核就是別人做好了的硬件模塊,提供完整的用戶接口和說明文檔,更復雜的還有示例工程,你只要能用好這個IP核,設計已經完成一半了。說起來容易,從冗長的英文文檔和網上各個非標準教程中汲取所需,並靈活運

Xilinx Vivado的使用詳細介紹(5):調用用戶自定義封裝的IP核

cond 5.4 vba adding 計算機 property with 我們 class Zedboard OLED Display Controller IP v1 介紹

Xilinx 濾波器IP核輸出有效位擷取問題

Xilinx是按照如下公式給出輸出位寬的: outputwidth = coefwidth + inputwidth + ceil(log2(tap)) 其中,outputwidth即為輸出位寬,coefwidth為抽頭係數位寬,inputwidth為輸入位寬,tap為濾波器階數,ceil為

Xilinx Vertex5 DDR2 SDRAM IP核模擬教程

在專案中使用Xilinx DDR2 SDRAM IP核之前,首先對該IP核進行模擬以瞭解IP核的時序和工作方式。 本人最近在使用Vertex5 版本的ddr2 SDRAM核,並使用ISE14.7版本生成;模擬工具使用modelsim SE.雖說官方有文件告訴我

ISE中FIFO IP核的Standard FIFO和First-word-Fall-Through模式的模擬比較

ISE下的FIFO IP核有Standard FIFO和First-word-Fall-Through兩種模式,相對於標準模式FWFT(First-word-Fall-Through)可以不需要讀命令,自動的將最新資料放在dout上。 接下來分別對兩種模式下的FIFO進行模擬,testbench如

Xilinx Vivado的使用詳細介紹(3):使用IP核

ilinx Vivado的使用詳細介紹(3):使用IP核 Author:zhangxianhe IP核(IP Core) Vivado中有很多IP核可以直接使用,例如數學運算(乘法器、除法器、浮點運算器等)、訊號處理(FFT、DFT、DDS等)。IP核類似程式設計中的函式庫(例如C語言中的printf()

Xilinx Vivado的使用詳細介紹(5):呼叫使用者自定義封裝的IP核

Zedboard OLED Display Controller IP v1 介紹

轉載xilinx-DDR3 ip 核:DDR3除錯總結

DDR3除錯總結 以前同是DDR3的無知少年,由於專案需求、工作需要,有幸深入研究DDR3,中間也確實歷經各種盲目階段,查詢資料、建立工程、除錯錯誤等等,如今對此不敢說是精通,也只能說是基本入門,寫此文章的目的也無非是想讓那些和當初的我一樣的初學者少走些彎

鎖相環PLL:Xilinx PLL IP核使用方法

轉自:https://blog.csdn.net/qq_30866297/article/details/52355245 1. 時鐘與振盪電路 在晶片中,最重要的是時鐘。那時鐘是怎麼來的呢?時鐘可以看成周期性的0與1訊號變化,而這種週期性的變化可以看成振盪。因此,振盪電路成為了時鐘的來源。

vivado 一步一步生成自己的自定義IP核

基於AXI-Lite的使用者自定義IP核設計 這裡以使用者自定義led_ip為例: 1.建立工程 和設計一過程一樣 這樣我們就進入了主介面 2.建立IP Tools –》Create and Package IP 來到IP建立歡迎介面:Next 接下來

xilinx cordic IP核的用法- arctan的演算法

本文介紹如何使用xilinx的CORDIC核計算一個arctan的值。 此方法對於梯度運算有著重要的意義。 原理略 環境:xilinx ISE 14.7 cordic 4.0 ISim 首先是IP核的選項設定,如圖: 標註1:選擇函式的型別,我們選擇計算arc

AXI4-Stream協議的訊號以及Xilinx提供的從AXI到AXI-Stream轉換的IP核區別

AXI4-Stream協議是一種用來連線需要交換資料的兩個部件的標準介面,它可以用於連線一個產生資料的主機和一個接受資料的從機。當然它也可以用於連線多個主機和從機。該協議支援多種資料流使用相同共享匯流排集合,允許構建類似於路由、寬窄匯流排、窄寬匯流排等更為普遍的互聯。比較重

xilinx cordic ip核的使用

16‘h00C0 -> 0000 0000 1100 0000,按照datasheet的phase資料格式:000,0 0000 1100 0000,也就是十進位制的0.0234375。而這個數的角度值為:0.0234375 * 180° = 4.21875°,也就是每個clk步進4.21875°。

使用xilinx ip core FIFO First- World First-Through (FWFT)模式的注意事項

也許很多人知道xilinx ip core 中的fifo可以配成standard 模式和FWFT模式,並知道兩者的區別是:standard模式下,當rd為高時,fifo會延時一個時鐘輸出資料(時序邏輯);而在FWFT模式下,當rd為高時,fifo不需要延時一個時鐘,而是直