LVDS/DVI/HDMI Interface

數字視訊訊號

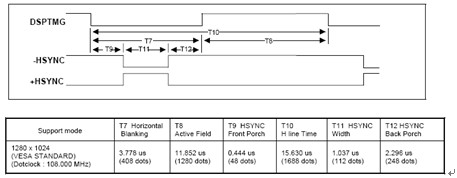

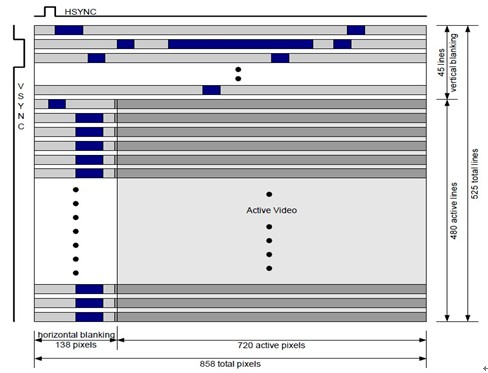

以SXGA為例,其時序如下:

垂直:

水平:

圖中DSPTMG為使能訊號,VSYNC為場同步訊號,HSYNC為行同步訊號。在行場的消隱期(T1與T7),DSPTMG為低電平,在此期間無有效視訊資料。

注意一個重要引數:對於這個時序的SXGA點頻是108MHz

1066×1688×60=107.964480MHz

1 Open LVDS Display Interface(OpenLDI)

LVDS,即Low Voltage Differential Signaling,是一種低壓差分訊號技術介面,每一條通道輸出的都是一對差分訊號。它為克服以TTL電平方式傳輸寬頻高位元速率資料時功耗大、EMI電磁干擾大等缺點而研製的一種數字視訊訊號傳輸方式。LVDS是利用電壓差(典型值為350 mV)進行編碼資訊。

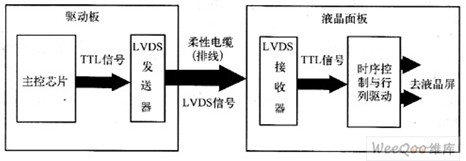

1.LVDS的電路組成

LVDS傳送器將驅動板主控晶片輸出的並行RGB資料訊號和控制訊號轉換成低電壓序列LVDS訊號,然後通過驅動板與液晶面板之間的柔性電纜(排線)將訊號傳送到液晶面板側的LVDS接收器,LVDS接收器再將序列訊號轉換為TTL電平的並行訊號,送往液晶屏時序控制與行列驅動電路。

圖1.1 LVDS介面電路的組成示意圖

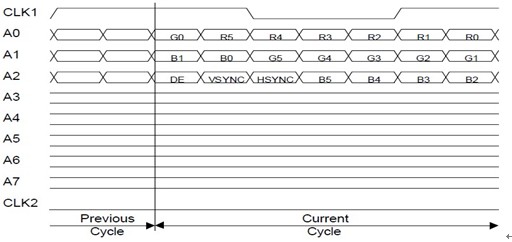

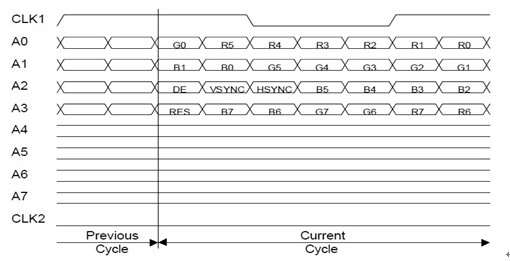

2.採用LVDS規範傳輸資料的時序圖

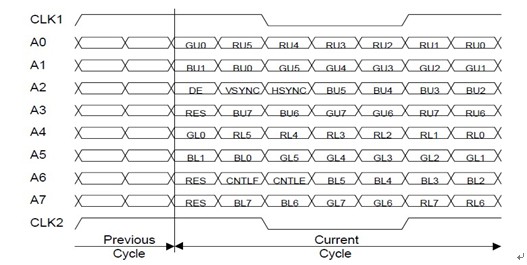

圖1.2 18位單畫素傳輸、非直流平衡模式

圖1.3 24位單畫素傳輸、非直流平衡模式

由圖1.2可以看出,非直流平衡模式18位單畫素傳輸共用了4個通道(1個時鐘訊號、3個數據信號),在一個時鐘週期內傳送了21bit,資料訊號包括3×6位的RGB訊號、使能訊號DE、行場訊號。其中使能訊號DE很重要,實際上使能訊號為低電平時就是行場的消隱期,有些接收端可不接收行場控制訊號只接受使能訊號即可,也正是因此;1.3圖,非直流平衡24位單畫素傳輸共用了5個通道,其中RES為預留位。

LDI突破了TTL瓶頸,頻寬得到了提升。但隨著1080p的視訊訊號成為主流,8位顏色要求大約3Gbps的頻寬,這大大超過了4通道LVDS介面能力。所以LVDS有了雙畫素傳輸模式。

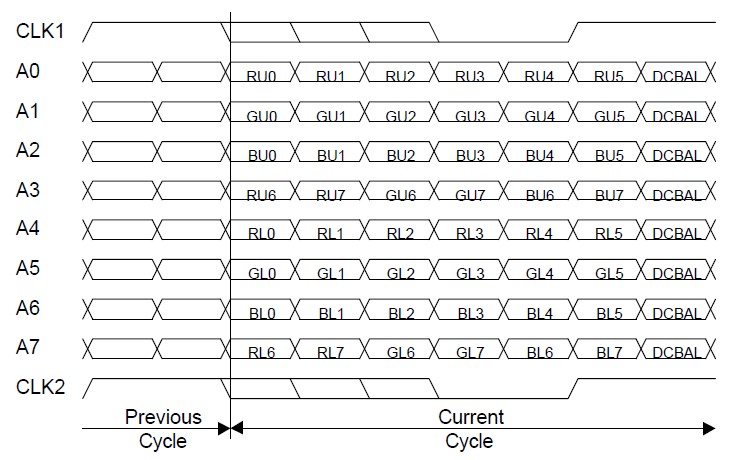

圖1.4 24位雙畫素傳輸、非直流平衡模式

由圖1.4可以看出,非直流平衡模式24位雙畫素傳輸共用了10個通道(2個時鐘訊號、8個數據信號),在一個時鐘週期內傳送了56bit,資料訊號包括6×8位的RGB訊號(兩個畫素)、使能訊號DE、控制訊號CNTLF和CNTLE、行場控制訊號以及兩個預留位RES。與圖1.3相比,點頻降低了一半,也就是位寬是原來的2倍。IC對較寬資料位處理時具有更大的取樣餘量,以及更大的電壓和溫度容限。此外,訊號頻率低,噪聲頻率也低,功耗也小。

另外LVDS也可以工作在直流平衡模式,直流平衡位的目的是最大限度地減少訊號線的短期和長期的直流偏置。DCBAL是直流平衡位。

圖1.5 24位雙畫素傳輸、直流平衡模式

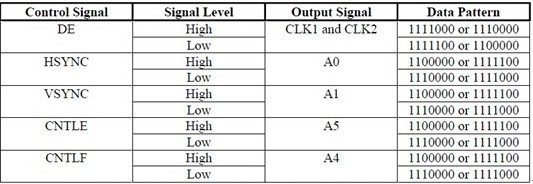

圖1.6直流平衡模式下24位雙畫素傳輸的資料格式

2 DVI(Digital Video Interface)介面

1.DVI簡介

DVI即數字視訊介面,是一種高速傳輸數字訊號的技術,DVI視訊傳輸避免了模擬視訊訊號傳輸過程中傳送端(一般為顯示卡)的數模轉換和接收端(一般為LCD顯示器)的模數轉換過程,同時也避免了模擬訊號傳輸過程中的噪聲干擾的問題,因此影象無損失。

DVI介面在傳輸數字訊號時又分為單鏈路(Single Link)和雙鏈路(Dual Link)兩種方式。根據DVI標準,一條TMDS通道可以達到165MHz的工作頻率和10-bit介面,也就是可以提供1.65Gbps的頻寬,即每秒可傳送1.65億點畫素。

單鏈路DVI介面的傳輸速率只有雙鏈路的一半,最大的解析度和重新整理率只能支援到1920x1200,60hz。至於雙鏈路的DVI介面,支援到2560x1600,60Hz模式,也可以支援1920x1080,120Hz的模式。液晶顯示器要達到3D效果必須擁有120Hz的重新整理率,所以3D方案中,使用DVI的話,必須要使用雙連線的DVI介面的DVI線。總的來說,如果是1920x1200內的解析度,單雙連線兩者輸出的畫質是一樣的。

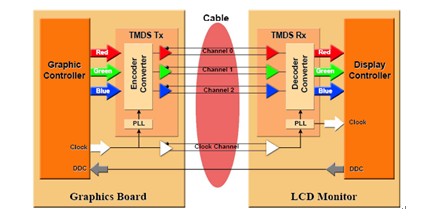

對於單鏈路的DVI介面,共有4個通道,通道0-2對應RGB三個分量,行場同步訊號及一些可選的控制訊號分別分配在在這三個通道上,第4個通道為時鐘通道。DVI的核心技術是TMDS(Transition Minimization Differential Signal)技術,這裡以8bit的R分量的傳輸為例簡單做一個簡單說明:並行的8bit的R分量傳輸時需要轉化為序列資料,為了可靠傳輸,不能簡單地進行了並轉串,而是以TMDS編碼演算法進行並轉串,TMDS演算法使轉換後的序列訊號的變換最小(Transition Minimization)以及序列碼流直流分量的平衡(DC Balancing)。序列訊號是以差分形式傳輸的(Differential Signal)。在接收端,通過TMDS接收器可以解碼出R、G、B、Hs、Vs、PixelClock等訊號。

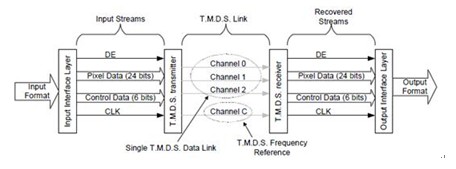

圖2.3 單鏈路DVI介面

2. TMDS協議

圖2.4 TMDS連線結構

資料流中包含了畫素和控制資料。DE有效期間,成為畫素資料有效期間,就是說這段時間傳送的是有效畫素資料。DE無效期間,成為傳送空間隙期間,這段時間傳送的資料不包括有效畫素資料,僅僅是控制訊號。

傳送端有3個一模一樣的編碼器,每個編碼器的輸入是2個控制訊號和8bit的畫素資料。依照DE的狀態,編碼器將按照兩個控制訊號的狀態或8bit畫素資料產生10bit的TMDS字元。每個解碼器輸出是一個連續的序列TMDS字元流。

TMDS資料通道傳送的是一個連續的10bit TMDS字元流,在空期間,傳送4個有顯著特徵的字元,它們直接對應編碼器的2個控制訊號的4個可能的狀態。在資料有效期間,10bit的字元包含8bit的畫素資料,編碼的字元提供近似的DC平衡,並最少化資料流的跳變次數,對有效畫素資料的編碼處理可以認為有兩個階段:第一個階段是依據輸入的8bit畫素資料產生跳變最少的9bit程式碼字;第二階段是產生一個10bit的程式碼字,表示是否對輸入程式碼進行反轉。最終的TMDS字元,將維持傳送字元總體的DC平衡。

3. 單/雙鏈路TMDS

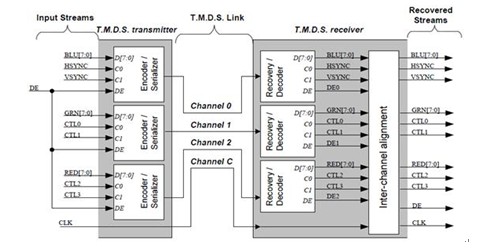

圖2.5 單鏈路TMDS通道對映

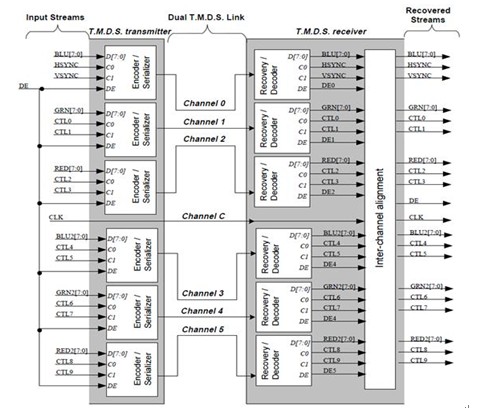

圖2.6 雙鏈路TMDS通道對映

無論是單鏈路還是雙鏈路TMDS都是先將輸入訊號在傳送端編碼器編碼,然後把並行資料轉換為序列資料,由資料通道傳送至接收端恢復為並行資料,最後進行解碼。

單鏈路TMDS傳送器由三個相同的編碼器組成,如圖2.5,2個控制訊號和8bit畫素資料對映到每個編碼器,除了行同步HS和場同步VS外,其它控制訊號的作用並沒有定義,在傳送器的輸入端,控制訊號CTL1、CLT2、CTL3必須保持邏輯低電平,推薦CTL0也保持邏輯低電平。

雙鏈路傳送器增加了三個資料通道,如圖2.6,雙鏈路配置在第一個鏈路上傳送每行的奇畫素,在第二個鏈路上傳送每行的偶畫素,每一行的第一個畫素是奇數畫素,即為畫素1。

3 HDMI 介面(High Definition Multimedia Interface)

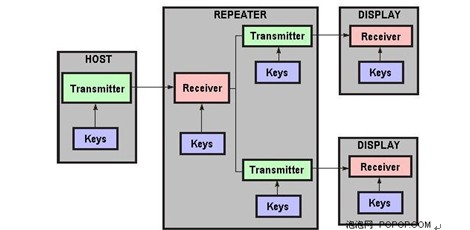

HDMI即高清晰度多媒體介面,源於DVI介面,同樣以TMDS訊號傳輸技術為核心,這也就是為何HDMI介面和DVI介面能夠通過轉接頭相互轉換的原因。HDMI是一種數字化視訊/音訊介面技術,是適合影像傳輸的專用型數字化介面,其可同時傳送音訊和影音訊號,最高資料傳輸速度為5Gbps。同時無需在訊號傳送前進行數/模或者模/數轉換。HDMI可搭配寬頻數字內容保護(HDCP)(DVI也支援該協議),以防止具有著作權的影音內容遭到未經授權的複製。HDMI所具備的額外空間可應用在日後升級的音視訊格式中。而因為一個1080p的視訊和一個8聲道的音訊訊號需求少於4Gbps,因此HDMI還有很大餘量。這允許它可以用一個電纜分別連線DVD播放器,接收器。

圖3.1 HDCP是一種雙向內容保護機制

1 HDMI原理

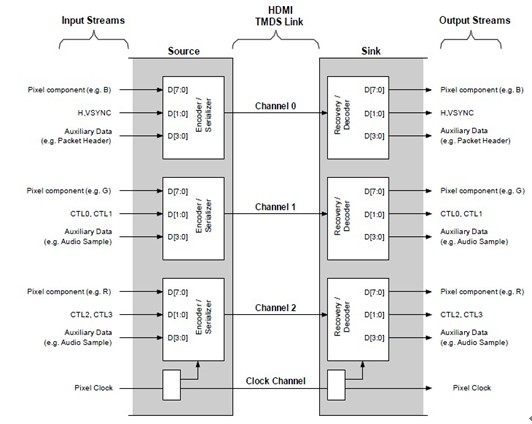

一般情況下,HDMI連線由一對訊號源和接受器組成,有時候一個系統中也可以包含多個HDMI輸入或者輸出裝置。每個HDMI訊號輸入介面都可以依據標準接收聯結器的資訊,同樣訊號輸出介面也會攜帶所有的訊號資訊。HDMI資料線和接收器包括三個不同的TMDS資料資訊通道和一個時鐘通道,這些通道支援視訊、音訊資料和附加資訊,視訊、音訊資料和附加資訊通過三個通道傳送到接收器上,而視訊的畫素時鐘則通過TMDS時鐘通道傳送,接收器接受這個頻率引數之後,再還原另外三個資料資訊通道傳遞過來的資訊。

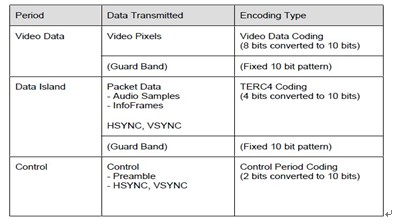

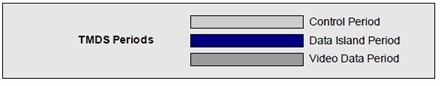

HDMI輸入的源編碼格式包括視訊畫素資料、控制資料和資料包。其中資料包中包含有音訊資料和輔助資訊資料,同時HDMI為了獲得聲音資料和控制資料的高可靠性,資料包中還包括一個BCH錯誤糾正碼。HDMI的資料資訊的處理可以有多種不同的方式,但最終都是在每一個TMDS通道中包含2位的控制資料、8位的視訊資料和4位的資料包。HDMI的資料傳輸過程可以分成三個部分:視訊資料傳輸期、資料包傳輸期和控制資料傳輸期。

圖3.2 HDMI資料傳輸示意圖

圖3.3 HDMI對資料的編碼

視訊資料傳輸期,HDMI資料線上傳送視訊畫素訊號,視訊訊號經過編碼,生成3路(即3個TMDS資料資訊通道,每路8位RGB)共24位的視訊資料流,輸入到HDMI發射器中。24位畫素的視訊訊號通過TMDS通道傳輸,將每通道8位的訊號編碼轉換為10位,在每個10位畫素時鐘週期傳送一個最小化的訊號序列,視訊訊號被調製為TMDS資料訊號傳送出去,最後到接受器中接收。

資料包傳輸期,TMDS通道上將出現音訊資料和輔助資料,這些資料每4位被一組,構成一個上面提到的4位資料包,資料包和視訊資料一樣,被調製為10位一組的的TMDS訊號後發出。視訊資料傳輸期和資料包傳輸期均開始於一個Guard Band保護頻帶,Guard Band由2個特殊的字元組成,這樣設計的目的在於在明確限定控制資料傳輸期之後的跳轉是視訊資料傳輸期。

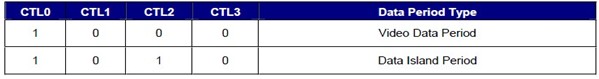

控制資料傳輸期,在上面任意兩個資料傳輸週期之間,每一個TMDS通道包含2位的控制資料,這一共6位的控制資料分別為HSYNC(行同步)、VSYNC(場同步)、CTL0、CTL1、CTL2和CTL3。每個TMDS通道包含2位的控制資料,採用從2位到10位的的編碼方法,在每個控制週期最後的階段,CTL0、CTL1、CTL2和CTL3組成的檔案頭,說明下一個週期是視訊資料傳輸期還是資料包傳輸期。

圖3.4 CTL0、CTL1、CTL2和CTL3組成的檔案頭

資料包和控制資料的傳輸是在視訊資料傳輸的消隱期,這意味著在傳輸音訊資料和其他輔助資料的時候,並不會佔據視訊資料傳輸的頻寬,並且也不要一個單獨的通道來傳輸音訊資料和其他輔助資料。這也就是為什麼相比DVI,HDMI可以同時傳輸視訊訊號和音訊訊號的原因。

相關推薦

LVDS/DVI/HDMI Interface

數字視訊訊號以SXGA為例,其時序如下: 垂直: 水平: 圖中DSPTMG為使能訊號,VSYNC為場同步訊號,HSYNC為行同步訊號。在行場的消隱期(T1與T7),DSPTMG為低電平,在此期間無有效視訊資料。 注意一個重要引數:對於這個時序的SXGA點頻是1

圍觀迅為IMX6開發板QT下LVDS和HDMI如何雙屏異顯的

graphics item 環境 width 開始 blog 雙屏 dmi ats 首先將迅為-IMX6開發板分別連接9.7寸屏和HDMI顯示器 然後使用MfgTool工具燒寫QT系統 然後撥碼開關設置成從emmc啟動 在uboot命令行下設置開發板為9.7寸屏顯示(這樣也

iTOP-iMX6開發板Android系統下LVDS和HDMI雙屏異顯方法

迅為iMX6 開發板 android 系統下 LVDS 和 HDMI 雙屏異顯的使用過程。 使用“Mfgtools-Rel-1.1.0_180403_MX6Q_UPDATER”版本的燒寫工具,把系統燒寫進開發板。系統啟動之後,把“.mp4”格式的視訊檔案放到“/sdcard”目錄下,如下圖所示。

視訊介面CVBS/Component/BNC/VGA/DVI/HDMI/SDI/DP/Type-C

視訊介面隨著新技術的不斷出現層出不窮,本文綜合CSDN上關於視訊介面介紹較為詳細的如下兩篇文章的內容,對市面上曾經以及目前常用的視訊介面進行詳細的介紹。 常見視訊介面(HDMI/VGA/SDI/CmaeraLink)介紹 VGA/DVI/HDMI/DP/Type-C等常用顯示介面對比介紹

淺談高清顯示接口RGB、LVDS、MIPI、eDP、HDMI、mini-LVDS、V-By-One(轉載)

morn 設備 宋體 解決 產品 key one txt targe 淺談高清顯示接口RGB、LVDS、MIPI、eDP、HDMI、mini-LVDS、V-By-One 標簽: hdmi轉edp rgb轉edp lvds轉edp lvds轉v-by-one

HDMI/DVI 顯示器熱插拔與檢測原理(HPD)

分享一下我老師大神的人工智慧教程!零基礎,通俗易懂!http://blog.csdn.net/jiangjunshow 也歡迎大家轉載本篇文章。分享知識,造福人民,實現我們中華民族偉大復興!

伺服器無法開機---VGA,HDMI,DVI,DP區別

可能出現的問題 1)主機中是否有硬碟 2)是否安裝伺服器Linux系統的iso與普通主機的iso不同 答:經查詢資料後發現,iso桌面版即可,沒有區別 3)聯機線或介面問題 答:發現VGA介面有問題,換成了DVI接線 【知識點】VGA、HDMI、DVI、DP區別 1.優先順序 D

【Tel18218088355的專欄】專業從事視訊類轉換IC,含:RGB,LVDS,MIPI,EDP,HDMI,VGA,CVBS,USB,GPS,UART,BT656\601\1120,V By-one,Type-C,串列埠,電源,ISP等

專業從事視訊類轉換IC,含:RGB,LVDS,MIPI,EDP,HDMI,VGA,CVBS,USB,GPS,UART,BT656\601\1120,V By-one,Type-C,串列埠,電源,ISP等...

HDMI,VGA,DVI,DP,MINI DP,AV等影音裝置介面規格

影音裝置的發展近些年很迅速,高清播放機,網路播放機,藍光播放機,3D播放機等等層出不窮。不管影音裝置的功能怎麼變化,它的根本目的還是更好的為人服務,滿足人的需求。新的功能,新的介面會在影音產品的功能不能滿足人們的娛樂生活時應運而生。如同老式“蓮花頭”不能滿足1080P的高清娛樂標準時,新一代的HDMI介

VGA HDMI DVI DP介面是什麼之顯示器顯示不清晰我該怎麼辦

VGA介面 先說VGA介面(簡述屬於淘汰邊緣產品對於2017年來說重點是VGA傳輸模擬訊號) VGA介面共有15針,分成3排,每排5個孔,是顯示卡上應用 VGA介面是大家所熟知的一個視訊模擬傳輸介面,從上世紀80年代被推出以來,已經發展了20多年了,很多領域已經相當成熟 最為廣泛的介面型別,絕大

Error while adding new interface: failed to open /dev/vboxnetctl: No such file or directory

com add err erro lin .com aso tps color Try this : sudo modprobe vboxnetadp ref: https://github.com/gasolin/foxbox/issues/32Erro

【轉】 Difference between defining static routes with next-hop address or exit interface

can tab setting color different using tin leading form For a long time I was confused about this. It was not clear to me what is the diff

java native interface JNI 調用Java方法

程序 color void size nature llb 方法調用 margin 處理 在上一篇文章中介紹了JNI。以及java調用JNI。這篇講一下 JNI調用java方法。 通過使用合適的JNI函數,你能夠創建Java對象,get、set 靜態(s

抽象類(abstract class)和接口(interface)有什麽異同?

否則 繼承 默認 strong 什麽 成員 -s 實例 abstract 相同點: 1.抽象類和接口都不能被實例化,但可以定義抽象類和接口類型的引用。 2.一個類如果繼承了抽象類和接口,必須要對其中的抽象方法全部實現。(接口中方法默認的是public abstract修飾的

interface

public 修飾 ace 類方法 fault 實現 xtend acea sta 允許在接口中定義默認方法,默認方法必須以default來修飾,該方法不能用static修飾。用接口的實現類的實例來調用默認方法 允許在接口中定義類方法,類方法必須用static修飾,該方法不

golang - interface的作用

log cal cep cnblogs () lang highlight truct plist 多態。struct 可以賦值給 interface。interface 可以轉換成子接口,或者 struct。 請看go中的一段的源代碼: listener, _ := n

更換oracle 集群網卡(Changing a Network Interface)

post data crs 52.0 network ifconf down oracle 更換 ?? 更換oracle 集群網卡(Changing a Network Interface) 假設換網卡前後 網卡名。ip,網關,子網掩碼都不變的話,集群層面不許要做額外

HDMI調試經驗分享(一)—— 基於KC705的example實現

alt 如果 追蹤 分享 生成 必須 還需要 pro 註意 在KC705的平臺上,實現HDMI的example有兩個,xapp1287,xapp1291。其中1291偏復雜。 因為我沒有HDCP的license,使用xapp1287的tcl生成

qt5 + vs2015自定義控件錯誤:undefend interface

自定義 widget 報錯 文件路徑 集成 wid 所在 結果 nbsp 控件中編譯時因為是把所有的單個控件集成到一個lib中,所以會引用#include<QDesignerCustomWidgetInterface>以及#include<QDesigne

<Java><Multi-thread><Lock interface>

基於 cnblogs 性能 線程 當前 try nbsp 應用場景 unit Overview 介紹java的lock interface. Motivation java擁有像synchronized這樣的內置鎖,那為什麽還需要lock這樣的外置鎖呢? 首先,性能不