FPGA 學習筆記 (十) PLL核的定製

通常我們板子上所帶的系統時鐘是50Mhz,如果我們需要更高的頻率就需要使用pll核,通過鎖相環將頻率倍頻到更高的頻率。

我們採用將系統時鐘50Mhz倍頻到100Mz來講解:

1)選擇tools→MegaWizard Plug-In Manager

2)選擇“Creat a new custom megafunction variation”,然後Next。

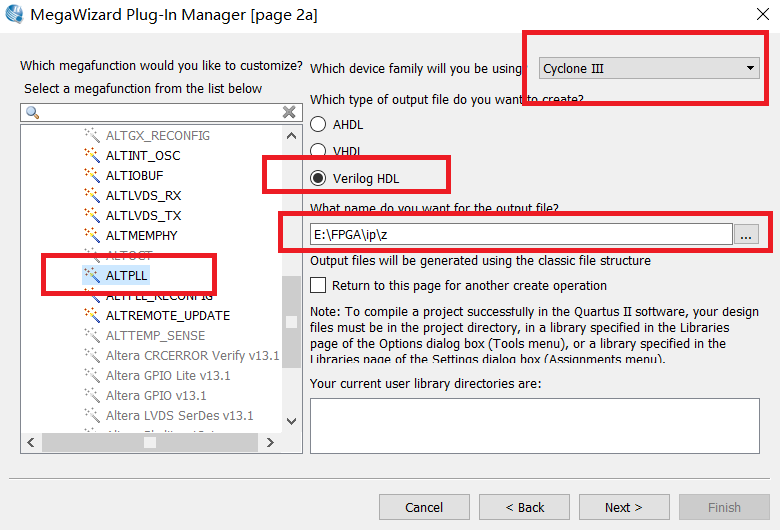

3)接著選擇我們所需要的IP核,如圖所示進行設定。

● 選擇IP核為“I/O ALTPLL”。

● 器件系列為“Cyclone IV E”。

● 選擇語言為“Verilog”。

●輸入工程所在的路徑,並且在最後面加上一個名稱,然後點選Next。

4) 接著來到了PLL的引數配置頁面,做如圖所示的設定。然後點選Next進入下一個頁面。

● 選擇器件的速度等級“8”。

● 選擇輸入系統時鐘“50MHz”。

5) Input/lock頁面中,如圖3.14所示進行設定,接著點選Next進入下一個頁面。

● 引出該PLL硬核的’areset’訊號,這是該PLL硬核的非同步復位訊號,高電平有效。

● 引出該PLL硬核的’locked’訊號,該訊號用於指示PLL是否完成內部初始化,已經可以正常輸出了高電平有效。

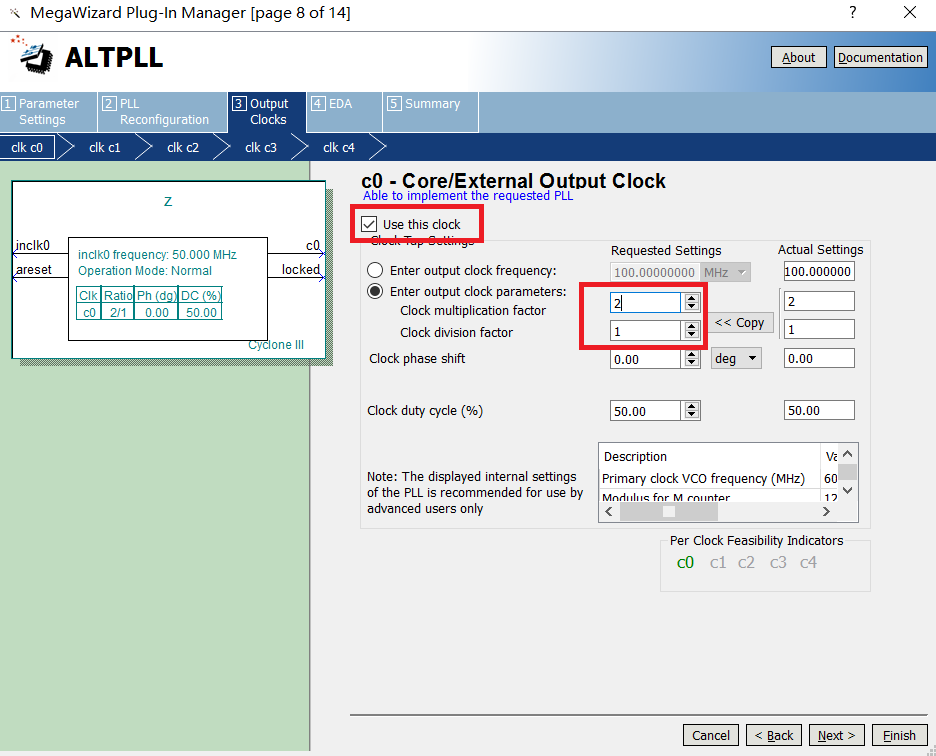

6) 這裡有5個可選的時鐘輸出通道,通常我們只用第一個通道其他不用 設定。

● 勾選“Use this clock”,表示使用該時鐘輸出訊號。

● 輸入乘法因子為2,除法因子為1。相移為0,佔空比為50%。

7) 配置完成後,最後在Summary頁面,如圖3.16所示,不勾選任何檔案。點選Finish完成PLL的配置。

8)在相關問價夾中生成的檔案如下,可直接複製如下檔案到工程中使用。

若需要定製其他頻率的pll核,不用再按照如上步驟新建pll,可在原有pll核中修改:

開啟syspll檔案找到defparam部分

clko_divide_by 為除法因子

clko_multiply_by 為乘法因子

input_frequency 表示時鐘週期為20000ps 即20ns或50MHZ

最後選擇相關器件。