基於FPGA的UART介面協議設計

一、PC終端概述

PC終端,Personal Computer 智慧終端,通俗的講,就是利用電腦GUI介面控制我們的外部硬體電路。

因此設計到了PC與外部硬體電路的通訊介面。對於臺式電腦、個人筆記本,最常用的介面就是USB介面、串列埠、並口、PS2介面、網口。在我們電子設計中的PC終端軟體的通訊,應用最多的就是串列埠、其次是USB介面、再就是網口。(對於現在大部分筆記本沒有了串列埠,我們可以用USB專串列埠線來代替。)這三種介面速度和性質不同,各有千秋:

(1)電子產品中,很多低速的資料採集,一些點陣系統的配置,GPRS模組的除錯等,都用串列埠來實現跟PC的通訊。甚至一些微控制器(巨集晶STC)的配置都用串列埠實現通訊。串列埠最高可以達到128000bps的速率,在低速場合下,完全能夠實現與PC的通訊,來滿足我們各種要求,來實現對資料的實時處理。

(2)設計到高速的資料傳輸、視訊影象傳輸等的,一般用USB介面來交換資料。比方說我們的硬碟、U盤、各種硬體下載器(USB BLUSTERO(∩_∩)O哈哈~)、以及實時影象採集、視訊採集等,都是用USB介面來實現的。目前USB已經發展到了USB 3.0,但還是以USB 2.0為主,最高能夠達到480Mbps(60MB/s)高速,足夠的頻寬滿足我們對高速、海量資料的採集處理。

(3)最後就是網口的通訊,一般網口用來上網傳輸資料,但是也可以用來硬體和PC之間的資料傳輸。一般網路,千兆的能力,NetFPGA,用FPGA實現的通訊協議,早已不是夢想。近年來流行的網路攝像頭,就是通過網路來傳輸(當然也有通過WiFi飛);現在超市、廣場的超大真彩點陣是資料傳輸,由於資料量之大,一般採用網路傳輸,來達到顯示的實時性。

最後,我們的PC終端軟體,就是通過C++、MFC、C#等語言編寫軟體,對這些介面的驅動,來對資料的採集處理,從而達到使用者預期的要求。本章中主要講解FPGA硬體平臺的UART、USB通訊介面的軟硬體設計,並且對Bingo的程式碼設計稍作分析,希望對你有用。

UART:Universal Asynchronous Receiver/Transmitter,通用非同步接收/傳送裝置,所謂非同步,就是說傳送和接受不能同時進行,是單工的。對於UART的verilog設計,簡單的說就是需要“波特率發生器”與“資料傳輸時序”兩個模組,如下:

(1)波特率

在UART通訊協議中很重要的一個定義,就是“波特率”,即傳輸資料時的速率。波特率一般有以下這些:

(2)資料傳輸時序

對於UART資料傳輸的協議,如下所示。其中奇偶校驗位與停止位不是必須的。而“起始位、資料位、停止位”則是必須的。一般資料位為8 bits。

|

位 |

定義 |

|

起始位 |

先發出一個邏輯”0”的訊號,表示傳輸字元的開始。 |

|

資料位 |

緊接著起始位之後。資料位的個數可以是4、5、6、7、8等,構成一個字元。通常採用ASCII碼。從最低位開始傳送,靠時鐘定位。 |

|

奇偶校驗位 |

資料位加上這一位後,使得“1”的位數應為偶數(偶校驗)或奇數(奇校驗),以此來校驗資料傳送的正確性。 |

|

停止位 |

它是一個字元資料的結束標誌。可以是1位、1.5位、2位的高電平。 |

|

空閒位 |

處於邏輯“1”狀態,表示當前線路上沒有資料傳送。 |

具體的時序圖如下所示。A-b為起始位,b-c為資料位,c-d為停止位。

UART是計算機中序列通訊埠的關鍵部分。在計算機中,UART相連於產生相容RS232規範訊號的電路。RS232標準定義邏輯“1”訊號相對於地為-3到-15伏,而邏輯“0”相對於地為3到15伏。所以,當一個微控制器中的UART相連於PC時,它需要一個RS232驅動器來轉換電平。

如下圖所示,UART硬體電路灰常的簡單,只需要一塊電平轉換晶片即可。電平轉換晶片一般用Max3232、Max232,SP3232等,其中Maxim公司的電平轉換晶片比較常用。跟PC和處理器相連線的,只要相應的TXD、RXD兩根訊號線即可。

基於FPGA的UART設計,其實在微控制器中沒有這麼一說。微控制器中早已有了UART的IP,我們只要呼叫函式即可,但FPGA中,純硬體設計電路上,我們想要使用串列埠來除錯,那我們就必須瞭解徹底UART通訊協議,必須自己動手寫UART的硬核。利用硬體描述語言,相當的方便。

UART驅動程式碼的編寫,算是比較簡單的設計了。Bingo當年用VHDL編寫串列埠通訊,後來學了Verilog,重新來過,最後修改串列埠,改善得到穩定的版本,經過多次測試,上萬資料傳輸未出現過錯誤,已應用於多個專案中,在此獻醜,希望對你有用。

以下是相關的下載資訊:

(1)串列埠除錯助手

(2)uart_io_test工程

(3)uart_fifo_design工程

對於基於FPGA的Verilog設計UART通訊介面的程式碼分析,如下所示:

(1)波特率發生器

如果您看過前面章節,那您是否還記得“第九章 為所欲為——教你什麼才是真正的任意分頻”?此處我們為了達到標準的頻率,最大極限的不想出現任何誤差,Bingo利用自己設計的“相位控制分頻原理”,來完成此模組的設計。具體的分頻原理請看第九章,此處不再做累贅的闡述,謝謝。

關於本模組的主要程式碼,如下:

/*************************************************

* Module Name : clk_generator.v

* Engineer : Crazy Bingo

* Target Device : EP2C8Q208C8

* Tool versions : Quartus II 11.0

* Create Date : 2011/01/27

* Revision : v1.0

* Description :

**************************************************/

module clk_generator

(

input clk,

input rst_n,

output clk_bps,

output clk_smp

);

//------------------------------------------

/************clk_smp = 16*clk_bps************

Freq_Word1 <= 32'd25770; Freq_Word1 <= 32'd412317; //300 bps

Freq_Word1 <= 32'd51540; Freq_Word2 <= 32'd824634; //600 bps

Freq_Word1 <= 32'd103079; Freq_Word2 <= 32'd1649267; //1200 bps

Freq_Word1 <= 32'd206158; Freq_Word2 <= 32'd3298535; //2400 bps

Freq_Word1 <= 32'd412317; Freq_Word2 <= 32'd6597070; //4800 bps

Freq_Word1 <= 32'd824634; Freq_Word2 <= 32'd13194140; //9600 bps

Freq_Word1 <= 32'd1649267; Freq_Word2 <= 32'd26388279; //19200 bps

Freq_Word1 <= 32'd3298535; Freq_Word2 <= 32'd52776558; //38400 bps

Freq_Word1 <= 32'd3693672; Freq_Word2 <= 32'd59098750; //43000 bps

Freq_Word1 <= 32'd4810363; Freq_Word2 <= 32'd76965814; //56000 bps

Freq_Word1 <= 32'd4947802; Freq_Word2 <= 32'd79164837; //57600 bps

Freq_Word1 <= 32'd9895605; Freq_Word2 <= 32'd158329674; //115200bps

Freq_Word1 <= 32'd10995116; Freq_Word2 <= 32'd175921860; //128000bps

Freq_Word1 <= 32'd21990233; Freq_Word2 <= 32'd351843721; //256000bps

*****************************************************/

//only want to generate beautiful clk for bsp and sample

reg [31:0] bps_cnt1;

reg [31:0] bps_cnt2;

[email protected](posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

bps_cnt1 <= 0;

bps_cnt2 <= 0;

end

else

begin

bps_cnt1 <= bps_cnt1 + 32'd9895605;

//Bps=115200bps

bps_cnt2 <= bps_cnt2 + 32'd158329674;

//Bps=115200bps*16

end

end

//------------------------------------------

//clk_bps sync bps generater

reg clk_bps_r0,clk_bps_r1,clk_bps_r2;

[email protected](posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

clk_bps_r0 <= 0;

clk_bps_r1 <= 0;

clk_bps_r2 <= 0;

end

else

begin

if(bps_cnt1 < 32'h7FFF_FFFF)

clk_bps_r0 <= 0;

else

clk_bps_r0 <= 1;

clk_bps_r1 <= clk_bps_r0;

clk_bps_r2 <= clk_bps_r1;

end

end

assign clk_bps = ~clk_bps_r2 & clk_bps_r1;

//------------------------------------------

//clk_smp sync receive bps generator

reg clk_smp_r0,clk_smp_r1,clk_smp_r2;

[email protected](posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

clk_smp_r0 <= 0;

clk_smp_r1 <= 0;

clk_smp_r2 <= 0;

end

else

begin

if(bps_cnt2 < 32'h7FFF_FFFF)

clk_smp_r0 <= 0;

else

clk_smp_r0 <= 1;

clk_smp_r1 <= clk_smp_r0;

clk_smp_r2 <= clk_smp_r1;

end

end

assign clk_smp = ~clk_smp_r2 & clk_smp_r1;

endmodule

程式碼中Bingo設定了多個選項的bps,根據您的需要,可以直接修改程式碼,來達到自己的要求。本模組的功能主要功能是生成兩個時鐘:

a) clk_bps : UART TXD訊號線資料傳送的波特率

b) clk_smp: UART RXD訊號線資料接受的取樣速率,以對已波特率的16倍速度取樣,捕獲資料的中點,在資料最穩態讀取資料,達到最大限制的穩定。

(2)TXD傳送模組

這部分程式碼比較簡單,因為FPGA是主控,只要根據固定的時序給資料即可。Bingo設計了一個狀態機來完成時序,狀態機程式碼如下:

[email protected](posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

txd_state <= T_IDLE;

txd_flag_r <= 0;

txd <= 1'b1;

end

else

begin

case(txd_state)

T_IDLE:

begin

txd <= 1;

txd_flag_r <= 0;

if(txd_en == 1)

txd_state <= T_SEND;

else

txd_state <= T_IDLE;

end

T_SEND:

begin

if(clk_bps == 1)

begin

if(txd_cnt < 4'd9)

txd_cnt <= txd_cnt + 1'b1;

else

begin

txd_cnt <= 0;

txd_state <= T_IDLE;

txd_flag_r <= 1;

end

case(txd_cnt)

4'd0: txd <= 0;

4'd1: txd <= txd_data[0];

4'd2: txd <= txd_data[1];

4'd3: txd <= txd_data[2];

4'd4: txd <= txd_data[3];

4'd5: txd <= txd_data[4];

4'd6: txd <= txd_data[5];

4'd7: txd <= txd_data[6];

4'd8: txd <= txd_data[7];

4'd9: txd <= 1;

endcase

end

end

endcase

end

End

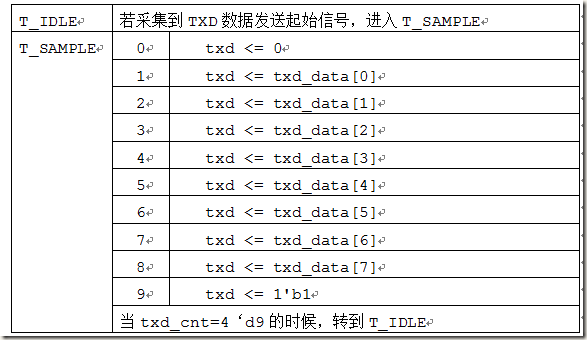

資料傳送的狀態機設計如下:

同時,為了軟體除錯,資料識別等的方便,Bingo在此模組設定了資料傳送標誌位。此部分主要參考了Bingo“第七章 你想幹嘛——邊沿檢測技術”的方法,此處不再做累贅闡述,若有不懂請看上文。此部分程式碼如下:

//-------------------------------------

//Capture the falling of data transfer over

reg txd_flag_r0,txd_flag_r1;

[email protected](posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

txd_flag_r0 <= 0;

txd_flag_r1 <= 0;

end

else

begin

txd_flag_r0 <= txd_flag_r;

txd_flag_r1 <= txd_flag_r0;

end

end

assign txd_flag = txd_flag_r1 & ~txd_flag_r0;

(3)RXD傳送模組

由於接收資料的時候,主控是PC,從機是FPGA,因此FPGA需要取樣資料。以上波特率發生器中講到過,取樣時鐘clk_bps = 16*clk_bps。FPGA硬體描述,通過計數,當取樣到RXD資料起始位訊號有效時,0-7-15開始計數,,其中7為資料的中點,最穩定的時刻。因此在此時取樣資料,能夠達到最穩定的效果。Bingo設計程式碼如下:

[email protected](posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

smp_cnt <= 0;

rxd_cnt <= 0;

rxd_data <= 0;

rxd_state <= R_IDLE;

end

else if(clk_smp == 1)

begin

case(rxd_state)

R_IDLE:

begin

rxd_cnt <= 0;

if(rxd_sync == 1'b0)

begin

smp_cnt <= smp_cnt + 1'b1;

if(smp_cnt == 4'd7) //8 clk_smp enable

rxd_state <= R_SAMPLE;

end

else

smp_cnt <= 0;

end

R_SAMPLE:

begin

smp_cnt <= smp_cnt +1'b1;

if(smp_cnt == 4'd7)

begin

rxd_cnt <= rxd_cnt +1'b1;

if(rxd_cnt == 4'd7)

rxd_state <= R_IDLE;

case(rxd_cnt)

3'd0: rxd_data[0] <= rxd_sync;

3'd1: rxd_data[1] <= rxd_sync;

3'd2: rxd_data[2] <= rxd_sync;

3'd3: rxd_data[3] <= rxd_sync;

3'd4: rxd_data[4] <= rxd_sync;

3'd5: rxd_data[5] <= rxd_sync;

3'd6: rxd_data[6] <= rxd_sync;

3'd7: rxd_data[7] <= rxd_sync;

endcase

end

end

endcase

end

end

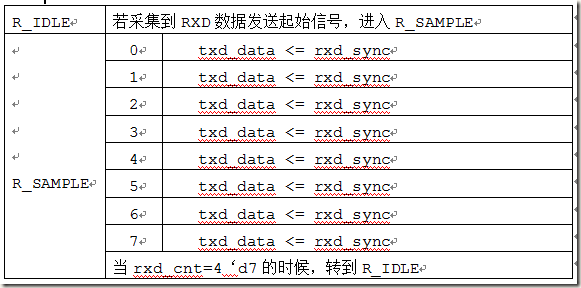

同樣,傳送部分狀態機如下如下所示:

4、USB程式碼測試圖:

三、USB通訊介面設計

1、USB通訊協議

USB : Universal Serial BUS(通用序列匯流排)的縮寫,而其中文簡稱為“通串線,是一個外部匯流排標準,用於規範電腦與外部裝置的連線和通訊。是應用在PC領域的介面技術。USB介面支援裝置的即插即用和熱插拔功能。USB是在1994年底由英特爾、康柏、IBM、Microsoft等多家公司聯合提出的。

USB發展經過了以下幾個階段:

(1)USB1.0:1.5Mbps(192KB/s) 低速(Low-Speed) 500mA……1996年1月

(2)USB1.1:12Mbps(1.5MB/s) 全速(Full-Speed) 500mA……1998年9月

相關推薦

基於FPGA的UART介面協議設計

一、PC終端概述 PC終端,Personal Computer 智慧終端,通俗的講,就是利用電腦GUI介面控制我們的外部硬體電路。 因此設計到了PC與外部硬體電路的通訊介面。對於臺式電腦、個人筆記本,最常用的介面就是USB介面、串列埠、並口、PS2介面、網口。在我們電

趣談網路協議---基於JSON的RESTful介面協議:我不關心過程,請給我結果

SOAP 過於複雜,設計是面向動作的,往往因為架構問題導致併發量上不去。 RESTful 是一種架構模式,主要面向資源,提供無狀態服務,有利於橫向擴充套件應對高併發。 傳輸協議問題 傳輸協議問題—基於 HTTP。 對於 SOAP,建立一個訂單,用 POST 動作

WEB使用OAuth2協議實現開放介面的設計方案

術語 developer:開發者,第三方應用的開發者。 openPlat:開放平臺,發放App Key(相當於第三方應用的ID)、App Secret(私鑰,驗證ID是否唯一有效,需要妥善保管)。 Authorization Server:授權服務端,發放Code、

基於WEB的網路遠端作業處理系統之使用者介面的設計與實現,java設計與開發

**基於WEB的網路遠端作業處理系統之使用者介面的設計與實現,java設計與開發** 基於WEB的網路遠端作業處理系統之使用者介面的設計與實現mysql資料庫建立語句 基於WEB的網路遠端作業處理系統之使用者介面的設計與實現oracle資料庫建立語句 基於WEB的網路遠端

基於OLSR路由協議的Wireless Mesh Network實驗設計

何淵淘,劉燕美 (鄭州航空工業管理學院,河南 鄭州 450000) 摘要:WMN(Wireless Mesh Network)即無線網狀物,該網路在無線媒介上以多跳的方式構成通訊系統。無線網狀網是無線網路的發展重心,但由於無線網路本身的各種標準和實現處於快速發

基於Java的REST架構風格及介面安全性設計的討論

1.REST即表現層狀態傳遞(Representational [,rɛprɪzɛn'teʃnl] State Transfer,簡稱REST)。 (1)REST名詞解釋: 通俗來講就是資源在網路中以某種表現形式進行狀態轉移。分解開來: Resource:所指的不只

談談網路程式設計中應用層(基於TCP/UDP)的協議設計

對於初涉網路程式設計的開發人員來說,在通訊協議的設計上一般會有所困惑。一般的網路程式設計書籍上也較少涉及這方面的內容。估計是覺得太簡單了。這塊確實是不難,但如果不瞭解,又很容易出簍子或者繞彎路。下面我就來談談基於TCP/UDP的協議設計。 1、基於TCP的協議

基於TCP/IP協議的socket通訊server

while resource err close 通訊 ice inpu utils 緩沖 思路: socket必須要隨項目啟動時啟動,所以需用Spring自帶的監聽器,需要保持長連接,要用死循環,所以必須另外起線程,不能阻礙主線程運行 1.在項目的web.xml中配置li

# 2017-2018-1 20155318 《信息安全系統設計基礎》 實驗五 通訊協議設計

應用程序 .cn 代碼 下使用 申請 只讀 genrsa 關閉 accept 2017-2018-1 20155318 《信息安全系統設計基礎》 實驗五 通訊協議設計 Linux下OpenSSL的安裝與測試 任務要求:在Ubuntu中完成 http://www.cnblo

2017-2018-1 20155317《信息安全系統設計基礎》 實驗五 通訊協議設計

pthread set 申請 gac process 在一起 href main fun 2017-2018-1 20155317《信息安全系統設計基礎》 實驗五 通訊協議設計 實驗要求 任務 安裝OpenSSL環境,並編寫測試代碼驗證無誤研究OpenSSL算法,測試

2017-2018-1 20155234 實驗五 通訊協議設計

src 通訊 ubuntu ref 作業 服務器 html clas logs 實驗任務 任務一 在Ubuntu中完成 http://www.cnblogs.com/rocedu/p/5087623.html 中的作業 提交運行結果截圖 截圖如下 任務二 在Ubuntu中

20155325 2017-2018 1 《信息安全系統設計基礎》實驗五 通訊協議設計

inux tps rime 影響 收信 alt 完整 man 輸出 實驗五 通訊協議設計-1 實驗要求 在Ubuntu中完成 http://www.cnblogs.com/rocedu/p/5087623.html 中的作業 提交運行結果截圖 實驗截圖 碼雲鏈接 link

2017-2018-1 20155215 實驗五 通訊協議設計

完成 版本 html onf ron 分享圖片 apache day es2017 1 在Ubuntu中完成 http://www.cnblogs.com/rocedu/p/5087623.html 中的作業 提交運行結果截圖 Linux下OpenSSL的安裝與使用

2017-2018-1 201553334 實驗五 通訊協議設計

down 新增 ubun 防護 工作 通訊 ref 自我 roc 2017-2018-1 201553334 實驗五 通訊協議設計 1、在Ubuntu中完成 http://www.cnblogs.com/rocedu/p/5087623.html 中的作業 提交運行結果截圖

2017-2018-1 20155330 實驗五 通信協議設計

套接字 ext pub 輸出 連接 用戶 程序 %d 輔助 2017-2018-1 20155330 實驗五 通信協議設計 任務一 在Ubuntu中完成 http://www.cnblogs.com/rocedu/p/5087623.html 中的作業 實驗步驟 安裝Op

2017-2018-1 20155338 信息安全系統設計基礎》實驗五 通信協議設計

ges check free http void 行數 創建 /usr 使用 2017-2018-1 20155338 信息安全系統設計基礎》實驗五 通信協議設計 實驗要求: 任務一:Linux下OpenSSL的安裝與使用 在Ubuntu中完成(http://www.cnb

2017-2018-1 20155304 實驗五 通訊協議設計

img tex eof lin 單獨 serve free 密碼安全 echo 2017-2018-1 20155304 實驗五 通訊協議設計 實驗步驟 實驗五 通訊協議設計-1 在Ubuntu中完成 http://www.cnblogs.com/rocedu/p/5087

JAVA面向物件程式設計之購物車介面的設計與功能的實現

1、小組成員及分工 小組成員 負責工作 蘭澤祥 負責總體介面、Git程式碼庫 吳修恩 負責MVC模式、類名包名的規範化 2、Git 倉庫地址 倉庫地址:https://gitee

基於QT介面的嵌入式wifi操作

硬體:Tiny4412開發板,360wifi二代 軟體:開發板移植Qt5.7,wifi驅動及wifi操作指令集(iw,wpa_supplicant) 簡介: 使用system系統操作命令將原先命令列對wifi的操作隱藏在程式中進行,程式使用pushboutton掃描周圍wifi,將wif

基於wpf的相關設計問題-Command的使用

這篇來討論Command基於ViewModel的基本使用. 以prism內建Command Demo為例子,效果圖如下 View相對應的ViewModel 1.OrderEditorView的Model就是OrdersEditorPresentationModel了 2.