計算機系統要素:第一章 布林邏輯

為了讓自己未來好複習,從而寫下”計算機系統要素:從零開始構建計算機”讀書筆記——2017.7.12。

第一章 布林邏輯

1.布林代數

布林代數處理布林型(也稱為二進位制型)數值,比較典型的有 true/false、1/0、YES/NO、on/off.

常見的布林運算:AND、OR、NOT.

本書中有個重要的結論:

AND/or/not運算元都可以只用Nand或Nor函式來構建,既然每個布林函式都能夠通過規範化表示法由AND、OR、NOT構成,那麼每個布林函式也能僅使用Nand函式來構成。(一句話:如果實現了Nand門,就可以用Nand門直接構建其他門。)

ps: 規範化:布林表示式f(x,y)=x+y

| x | y | f(x,y) |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

只關注 輸出為1:

則規範化表示為: f(x,y)=x ̅y+xy ̅+xy

2.布林邏輯的應用

因為計算機硬體基於二進位制資料的表示和處理,所以布林函式在硬體體系結構中結構的描述、構建和優化過程中扮演這十分重要的角色。

3.實際專案

用Nand門構建第一章出現的所有閘電路:

有幾點:

a.HDL語言

以構建本書Xor為例:

CHIP Xor {

IN a, b;

OUT out;

// BUILTIN Xor;

PARTS://描述了所有底層電路的名稱和拓撲結構

Not(in 需要注意的幾點是:

1,HDL語言所涉及的所有關鍵詞都區分大小寫,包括上面所出現的CHIP, PARTS和晶片名等等。

2,所有句子後面都需要加分號。

3,IN和OUT聲明瞭該CHIP的輸入和輸出。

4,在out表示式中,“=”符號是向右賦值的,“out”是輸入管教通過運算輸出的值比如上面的“Not(in=a,out=nota)” in=a,為輸入,經過NOT運算輸出到out,out向右賦值到nota;。

5.在呼叫其他函式時要注意它的呼叫格式比如Not(in=,out=)

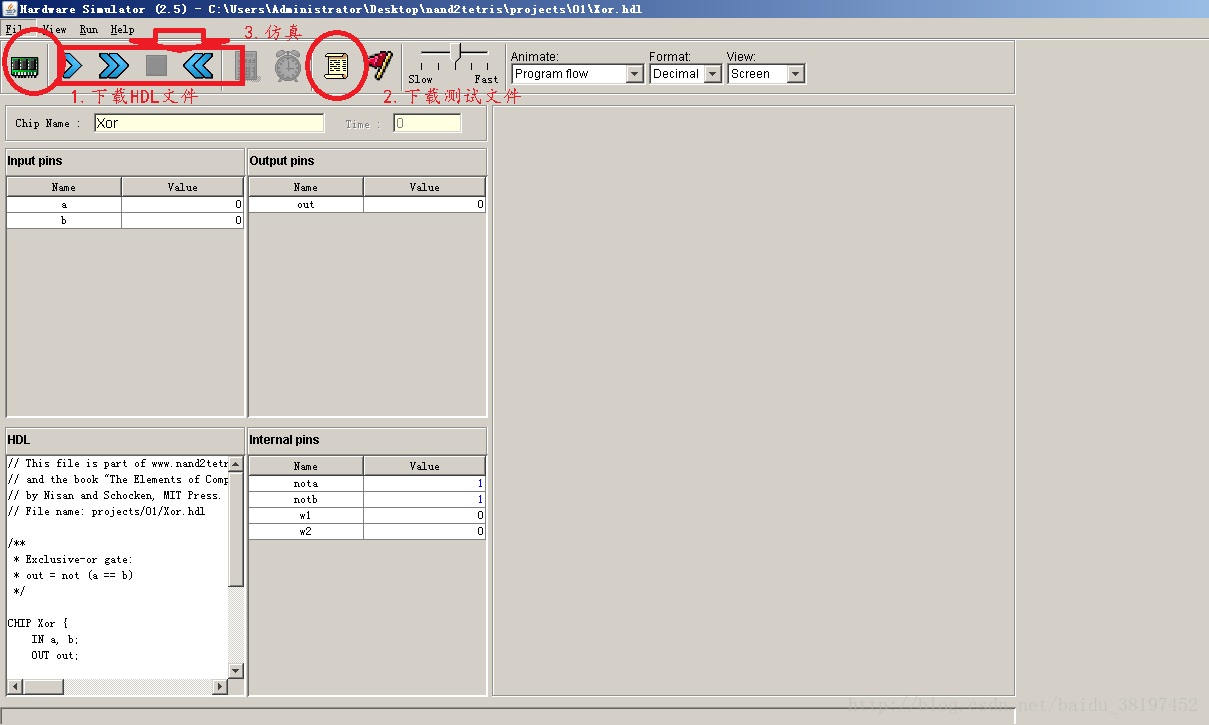

b.硬體模擬軟體

開始專案:

1.NOT門

CHIP Not {

IN in;

OUT out;

PARTS:

Nand(a=in,b=in,out=out);

}

2.And門

CHIP And {

IN a, b;

OUT out;

PARTS:

Nand(a=a,b=b,out=w1);

Nand(a=w1,b=w1,out=out);//呼叫not也可以

}

3.Or門

CHIP Or {

IN a, b;

OUT out;

PARTS:

Nand(a=a,b=a,out=w1);

Nand(a=b,b=b,out=w2);

Nand(a=w1,b=w2,out=out);

}

4.Xor

CHIP Xor {

IN a, b;

OUT out;

PARTS:

Not(in=a,out=na);

Not(in=b,out=nb);

And(a=a,b=nb,out=w1);

And(a=na,b=b,out=w2);

Or(a=w1,b=w2,out=out);

}

5.mux

* if sel == 0 out = a

* otherwise out =b

CHIP Mux {

IN a, b, sel;

OUT out;

PARTS:

Not(in=sel,out=nsel);

And(a=a,b=nsel,out=w1);

And(a=b,b=sel,out=w2);

Or(a=w1,b=w2,out=out);

}

6.DMUX

* {a,b} = {in,0} if sel == 0

* {0,in} if sel == 1

CHIP DMux {

IN in, sel;

OUT a, b;

PARTS:

Not(in=sel,out=nsel);

And(a=in,b=nsel,out=a);

And(a=in,b=sel,out=b);

}

7.NOT16

CHIP Not16 {

IN in[16];

OUT out[16];

PARTS:

Not(in=in[0],out=out[0]);

Not(in=in[1],out=out[1]);

Not(in=in[2],out=out[2]);

Not(in=in[3],out=out[3]);

Not(in=in[4],out=out[4]);

Not(in=in[5],out=out[5]);

Not(in=in[6],out=out[6]);

Not(in=in[7],out=out[7]);

Not(in=in[8],out=out[8]);

Not(in=in[9],out=out[9]);

Not(in=in[10],out=out[10]);

Not(in=in[11],out=out[11]);

Not(in=in[12],out=out[12]);

Not(in=in[13],out=out[13]);

Not(in=in[14],out=out[14]);

Not(in=in[15],out=out[15]);

}

8.AND16

CHIP And16 {

IN a[16], b[16];

OUT out[16];

PARTS:

And(a=a[0],b=b[0],out=out[0]);

And(a=a[1],b=b[1],out=out[1]);

And(a=a[2],b=b[2],out=out[2]);

And(a=a[3],b=b[3],out=out[3]);

And(a=a[4],b=b[4],out=out[4]);

And(a=a[5],b=b[5],out=out[5]);

And(a=a[6],b=b[6],out=out[6]);

And(a=a[7],b=b[7],out=out[7]);

And(a=a[8],b=b[8],out=out[8]);

And(a=a[9],b=b[9],out=out[9]);

And(a=a[10],b=b[10],out=out[10]);

And(a=a[11],b=b[11],out=out[11]);

And(a=a[12],b=b[12],out=out[12]);

And(a=a[13],b=b[13],out=out[13]);

And(a=a[14],b=b[14],out=out[14]);

And(a=a[15],b=b[15],out=out[15]);

}

9.OR16

CHIP Or16 {

IN a[16], b[16];

OUT out[16];

PARTS:

Or(a=a[0],b=b[0],out=out[0]);

Or(a=a[1],b=b[1],out=out[1]);

Or(a=a[2],b=b[2],out=out[2]);

Or(a=a[3],b=b[3],out=out[3]);

Or(a=a[4],b=b[4],out=out[4]);

Or(a=a[5],b=b[5],out=out[5]);

Or(a=a[6],b=b[6],out=out[6]);

Or(a=a[7],b=b[7],out=out[7]);

Or(a=a[8],b=b[8],out=out[8]);

Or(a=a[9],b=b[9],out=out[9]);

Or(a=a[10],b=b[10],out=out[10]);

Or(a=a[11],b=b[11],out=out[11]);

Or(a=a[12],b=b[12],out=out[12]);

Or(a=a[13],b=b[13],out=out[13]);

Or(a=a[14],b=b[14],out=out[14]);

Or(a=a[15],b=b[15],out=out[15]);

}

10.MUX16

CHIP Mux16 {

IN a[16], b[16], sel;

OUT out[16];

PARTS:

Mux(a=a[0],b=b[0],sel=sel,out=out[0]);

Mux(a=a[1],b=b[1],sel=sel,out=out[1]);

Mux(a=a[2],b=b[2],sel=sel,out=out[2]);

Mux(a=a[3],b=b[3],sel=sel,out=out[3]);

Mux(a=a[4],b=b[4],sel=sel,out=out[4]);

Mux(a=a[5],b=b[5],sel=sel,out=out[5]);

Mux(a=a[6],b=b[6],sel=sel,out=out[6]);

Mux(a=a[7],b=b[7],sel=sel,out=out[7]);

Mux(a=a[8],b=b[8],sel=sel,out=out[8]);

Mux(a=a[9],b=b[9],sel=sel,out=out[9]);

Mux(a=a[10],b=b[10],sel=sel,out=out[10]);

Mux(a=a[11],b=b[11],sel=sel,out=out[11]);

Mux(a=a[12],b=b[12],sel=sel,out=out[12]);

Mux(a=a[13],b=b[13],sel=sel,out=out[13]);

Mux(a=a[14],b=b[14],sel=sel,out=out[14]);

Mux(a=a[15],b=b[15],sel=sel,out=out[15]);

}

11.OR8WAY

CHIP Or8Way {

IN in[8];

OUT out;

PARTS:

Or(a=in[0],b=in[1],out=w1);

Or(a=in[2],b=in[3],out=w2);

Or(a=in[4],b=in[5],out=w3);

Or(a=in[6],b=in[7],out=w4);

Or(a=w1,b=w2,out=w5);

Or(a=w3,b=w4,out=w6);

Or(a=w5,b=w6,out=out);

}

12.MUX4WAY16

CHIP Mux4Way16 {

IN a[16], b[16], c[16], d[16], sel[2];

OUT out[16];

PARTS:

Mux16(a=a,b=b,sel=sel[0],out=w1);

Mux16(a=c,b=d,sel=sel[0],out=w2);

Mux16(a=w1,b=w2,sel=sel[1],out=out);

}

13.MUX8WAY16

CHIP Mux8Way16 {

IN a[16], b[16], c[16], d[16],

e[16], f[16], g[16], h[16],

sel[3];

OUT out[16];

PARTS:

Mux4Way16(a=a,b=b,c=c,d=d,sel=sel[0..1],out=tp1);

Mux4Way16(a=e,b=f,c=g,d=h,sel=sel[0..1],out=tp2);

Mux16(a=tp1,b=tp2,sel=sel[2],out=out);

}

14.DMUX4WAY

CHIP DMux4Way {

IN in, sel[2];

OUT a, b, c, d;

PARTS:

Not(in=sel[0],out=nsel0);

Not(in=sel[1],out=nsel1);

And(a=in,b=nsel0,out=a1);

And(a=a1,b=nsel1,out=a);

And(a=in,b=sel[0],out=b1);

And(a=b1,b=nsel1,out=b);

And(a=in,b=nsel0,out=c1);

And(a=c1,b=sel[1],out=c);

And(a=in,b=sel[0],out=d1);

And(a=d1,b=sel[1],out=d);

}

15.DMUX8WAY

CHIP DMux8Way {

IN in, sel[3];

OUT a, b, c, d, e, f, g, h;

PARTS:

DMux4Way(in=in,sel=sel[0..1],a=a1,b=b1,c=c1,d=d1);

DMux4Way(in=in,sel=sel[0..1],a=e1,b=f1,c=g1,d=h1);

Not(in=sel[2],out=nsel2);

And(a=a1,b=nsel2,out=a);

And(a=b1,b=nsel2,out=b);

And(a=c1,b=nsel2,out=c);

And(a=d1,b=nsel2,out=d);

And(a=e1,b=sel[2],out=e);

And(a=f1,b=sel[2],out=f);

And(a=g1,b=sel[2],out=g);

And(a=h1,b=sel[2],out=h);

}

相關推薦

計算機系統要素:第一章 布林邏輯

為了讓自己未來好複習,從而寫下”計算機系統要素:從零開始構建計算機”讀書筆記——2017.7.12。 第一章 布林邏輯 1.布林代數 布林代數處理布林型(也稱為二進位制型)數值,比較典型的有 true/false、1/0、YES/NO、on/o

計算機系統要素:第二章 布林運算

結論:補碼錶示法可以實現任何兩個用補碼錶示的有符號數的加法而不需要特殊的硬體。 完成實際專案: 1.半加器 CHIP HalfAdder { IN a, b; // 1-bit inputs OUT sum,

《計算機系統要素》學習筆記:第一章布林邏輯

1.工具準備 本書需要的工具和資源下載址:http://www.nand2tetris.org/software.php 工具分為tools和project兩個資料夾,開啟tools資料夾,開啟ha

【深入理解計算機系統隨筆】第一章

1、處理器的指令集架構和處理器的微體系結構應當分開 指令集架構描述的是每條機器程式碼指令的效果,ISA在CPU硬體和軟體之間提供了一個抽象層,對於CPU設計者來講,ISA是一種設計的規範和依據,對於編譯器設計者來講,亦然,知道了CPU採用的ISA,就可以知道自

《計算機系統要素學習》筆記之第1章 布林邏輯

《計算機系統要素學習》筆記之第1章 布林邏輯 布林表示式 xy代表x And y,x+y代表x Or y,~x代表Not x 硬體描述語言(HDL) Hardware Description Language 是一種結構化的硬體語言(hardware constructio

《計算機系統要素》學習筆記:第二章布林運算

1.學習要點 1)本章內容涉及數位電路中加法器的構建,以及二進位制資料在計算機中的計算方式,重點和難點為ALU的理解和實現。 2)重點理解補碼運算。 補碼:x的補碼=2的n次方-x,即反碼+1

計算機組成原理_第一章:計算機系統概論

匯編 概念 抽象 特性 解釋 及其 高級語言 語言 設備 第一章:計算機系統概論 1.1 計算機系統簡介 問題1:現代計算機系統由那兩部分組成? 現代計算機的多態性 CPS:信息物理系統 HPC:高速計算機,天河2號,Titan(Cray公司的,科磊公司) TF:TFlo

《計算機系統要素學習》筆記之第3章 時序邏輯

《計算機系統要素學習》筆記之第3章 時序邏輯 記憶單元:由時序晶片組成 底層時序門(Sequential gate):觸發器(Flip-flop),資料觸發器(Data Flip-flop),或DFF,D觸發器 規範詳述 D觸發器(DFF):data flip

《計算機系統要素學習》筆記之第2章 布林運算

《計算機系統要素學習》筆記之第2章 布林運算 2-補碼:也稱基補碼。if x!=0 then x=2^n-x else x=0 其中n為位數 規範詳述 半加器(HalfAdder):進行兩個一位二進位制加法 全加器(FullAdder):進行三個一位二進位制

《計算機系統要素》學習筆記:第五章計算機體系結構

1.學習要點 (1)系統 系統=計算裝置+程式 前三章只是靜態的構建計算裝置,第四章描述了程式的最底層表達,即機器語言。最後第五章是對前四章的總結,構建了一個完整的動態的計算機系統工作的模型。 (2)計算機工作的要點就在於:程式儲存和程式控制。而程式儲存

網絡操作系統:第一章 概述

direct 好的 小結 directory 哪些 自由軟件 什麽 第一章 war 本章小結 本章介紹了計算機網絡操作系統的概念,功能、特征和分類,對目前流行的幾種網絡操作系統,如Windows,UNIX、Linux和NetWare的發展及其特點進行了簡要介紹,此外,

Java學習(一):第一章 計算機、程式和Java概述

第一章 計算機、程式和Java概述 (1)匯流排--》 儲存裝置、記憶體、CPU、通訊裝置、輸入裝置、輸出裝置; (2)語言: 機器語言: 二進位制形式

計算機網路:第一章 概述

重點: 網際網路邊緣部分和核心部分的作用,其中包含分組交換的概念 計算機網路的效能指標 計算機網路分層次的體系結構,包含協議和服務的概念 1.1 計算機網路在資訊時代的作用 有三類大家都非常熟悉的網路,即電信網路、有線電視網路和計

【計算機組成原理】第一章 計算機系統概論

1.1 計算機系統簡介 1.1.1 計算機的軟硬體概念 計算機組成概覽: 1.1.2 計算機系統的層次結構 物理角度: 程式設計師角度: 系統複雜性管理的方法之一:抽象 區別兩點: 計算

Rust Cookbook(譯):讓我們再次進行系統程式設計(第一章)

在本章中,我們將介紹以下配方: 在Linux和macOS中設定Rust 在Windows中設定Rust 建立你的第一個Rust程式 定義變數賦值 設定布林值和字元型別 控制小數點,數字格式和命名引數 執行算術運算 定義可變變數 宣告並執行字串操作 在Rust中

《資料庫系統概念》第一章:引言

資料庫(database):一個互相關聯的資料的集合。 資料庫管理系統(DataBase-Management System,DBMS):由資料庫和一組用以訪問這些資料的程式組成。 資料檢視 資料抽象 物理層(physical level)

計算機組成原理知識點(第一章:計算機系統概論)

** 第一章:計算機系統概論 ** 1.計算機軟硬體概念 軟體: 由人們事先編織的具有各類特殊功能的程式組成. 分為兩大類: 系統軟體和應用軟體. 系統軟體就是使系統資源得到合理排程, 高

深入理解計算機系統_3e 第四章家庭作業(部分) CS:APP3e chapter 4 homework

ray design sed copy default ror this 處理 implement 4.52以後的題目中的代碼大多是書上的,如需使用請聯系 [email protected] 流水線部分只寫了偶數題號的,這幾天太浮躁,落下了好多課。。。 4.

深入理解計算機系統_3e 第八章家庭作業 CS:APP3e chapter 8 homework

fig lar man message -- ali rail raise mat 8.9 關於並行的定義我之前寫過一篇文章,參考: 並發與並行的區別 The differences between Concurrency and Parallel +----------

《深入理解計算機系統》第三章學習筆記

並發 錯誤 ia32 庫函數 容易 簡單 linux 嚴重 格式 通過本周的學習,總結出一下知識內容 機器級代碼 計算機系統使用了多種不同形式的抽象,利用更簡單的抽象模型來隱藏實現的細節。 對於機器級編程來說,其中兩種抽象尤為重要: 1、指令集體系結構(Instructio