暫存器名稱和地址的對映分析

首先要清楚的一點,所有操作,最終目的都是操作暫存器

一,對比51微控制器和STM32對暫存器的操作

1)51微控制器:

sfr P0=0x80; //關鍵字sfr 宣告地址和名稱的對映

P0=0x00; //將0x00賦值給P0口的8位(51微控制器一組IO為8位)2)STM32:

GPIOA->ODR=0x00000000 //為GPIOA的ODR暫存器地址賦值0x00000000二,以GPIOA為例說明STM32暫存器和名稱的對映:

GPIOA下的某個暫存器,掛載在GPIOA下,地址為GPIOA基地址+偏移量

GPIOA掛載在APB2匯流排,地址為APB2

ABP2掛載加外設基地址,地址為外設基地址+ABP2偏移量

原始碼中可以找到:

//外部匯流排基地址

#define PERIPH_BASE ((uint32_t)0x40000000)

//APB2基地址=外部匯流排基地址+偏移量

#define APB2PERIPH_BASE (PERIPH_BASE + 0x10000)

//GPIOA基地址=APB2基地址+偏移量

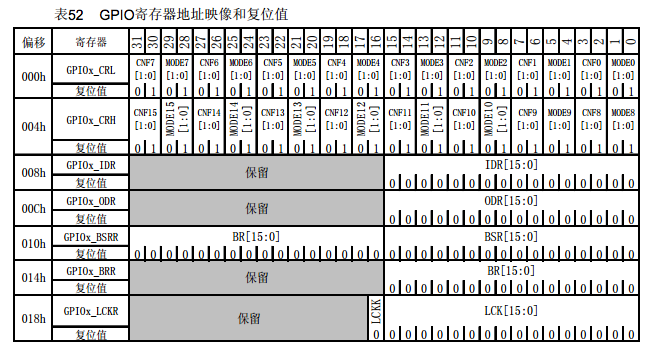

#define GPIOA_BASE (APB2PERIPH_BASE + 0x0800) 在STM32手冊中:GPIO暫存器地址映像如下:

如此,實現STM32暫存器名稱和地址之間的對映關係

相關推薦

暫存器名稱和地址的對映分析

首先要清楚的一點,所有操作,最終目的都是操作暫存器 一,對比51微控制器和STM32對暫存器的操作 1)51微控制器: sfr P0=0x80; //關鍵字sfr 宣告地址和名稱的對映 P0=0x00;

ADS1248 暫存器配置和通道轉換

ADS1248是TI的一款 24位delta-sigma(ΔΣ) 、2KSPS、8通道(4通道差分)ADC晶片。TI官方有RTD設計方案,參考文件做了一板4通道3線PT100溫度採集。除錯ADS1248過程中遇到一些問題,記錄下來方便以後使用。 參考程式碼:

Nand flash(三)暫存器及硬體初始化分析

關於NAND Flash S5PV210的NAND Flash控制器有如下特點: 1) 支援512byte,2k,4k,8k的頁大小 2) 通過各種軟體模式來進行NAND Flash的讀寫擦除等 3) 8bit的匯流排 4) 支援SLC和MCL的NAND Flash 5) 支

暫存器ESP和EBP的理解

一直對暫存器ESP和EBP的概念總是有些混淆,檢視定義ESP是棧頂指標,EBP是存取堆疊指標。還是不能很透徹理解。之後借於一段彙編程式碼,總算是對兩者有個比較清晰的理解。下面是按呼叫約定__stdcall 呼叫函式test(int p1,int p2)的彙編程式碼;假設執行

對暫存器ESP和EBP的一些理解

PS:EBP是當前函式的存取指標,即儲存或者讀取數時的指標基地址;ESP就是當前函式的棧頂指標。每一次發生函式的呼叫(主函式呼叫子函式)時,在被呼叫函式初始時,都會把當前函式(主函式)的EBP壓棧,以便從子函式返回到主函式時可以獲取EBP。 下面是按呼叫約定__stdc

C++程式碼反彙編後的函式呼叫過程,堆疊暫存器EBP和ESP

棧是從高地址向低地址生長的。 ebp始終指向當前棧幀的棧底部 , 通過ebp+4中儲存著函式的返回地址 。函式返回時將EBP的值推給EIP ,返回到上一個函幀繼續執行。 ret 與call指令 相反 ,call 將EIP壓入堆疊,然後跳到標號處。 ret 8 在函式返回

STM32 暫存器地址名稱對映

stm32韌體庫內可以看見指向結構體的指標,其賦值如下: 例:GPIOA->ODR=0x00000000; 此句是為ODR暫存器賦值為0x00000000; 在stm32f10x.h檔案裡定義了以下結構體 typedef str

2018/11/03-棧、x86架構和暫存器-《惡意程式碼分析實戰》

棧用於函式的記憶體、區域性變數、流控制結構等被儲存在棧中。棧是一種用壓和彈操作來刻畫的資料結構,向棧中壓入一些東西,然後再把他們彈出來。它是一種先入後出(LIFO)的結構。 x86架構有對棧的內建支援。用於這種支援的暫存器包括ESP和EBP。其中,ESP是棧指標,包含了指向棧頂的記憶體地址。一些東西

WinCE下的地址對映以及暫存器訪問

分享一下我老師大神的人工智慧教程!零基礎,通俗易懂!http://blog.csdn.net/jiangjunshow 也歡迎大家轉載本篇文章。分享知識,造福人民,實現我們中華民族偉大復興!

【arm】arm32位和arm64位架構、暫存器和指令差異分析總結

Date: 2018.9.21 1、參考 2、前言 最近三個月的時間,都在進行解碼庫的arm架構彙編優化,包括arm32位彙編優化和arm64位彙編優化。在arm32位入門之後,只要掌握了兩種架構的暫存器和指令集差異之後,就可以很快上手編寫arm64

ioremap 函式對映操作已知的實體地址(暫存器、埠、IO)

NAME ioremap - map bus memory into CPU space SYNOPSIS void __iomem * ioremap (unsigned

跟我學彙編(三)暫存器和實體地址的形成

一、通用暫存器 對於一個彙編程式設計師來說,CPU中主要部件是暫存器。暫存器是CPU中程式設計師可以用指令讀寫的部件。程式設計師通過改變各種暫存器的內容來實現對CPU的控制。 不同的CPU,暫存器的個數、結構是不同的。8086CPU 有14個暫存器,每個暫存

1.4 x86 CPU地址空間分配和暫存器訪問

1、基本概念 cpu地址空間和pci地址空間是兩個常用的比較容易混淆的概念,特別是其中不同系列的cpu的實現還各不相同:x86系列cpu地址空間和pci地址空間是重合的,即為同一空間;而非x86 cpu的cpu地址空間和pci地址空間為兩個獨立的空間。 也許

Verilog中儲存器——暫存器陣列定義和賦值

[轉載]http://blog.sina.com.cn/s/blog_9424755f0101rhrh.html 儲存器是一個暫存器陣列。儲存器使用如下方式說明: reg [ msb: 1sb] memory1 [ upper1: lower1], memory2 [upper2: lowe

ARM 程式狀態暫存器深入分析

程式狀態暫存器共分為兩種,它們的位數都是 32 位: 1 個 CPSR:當前程式狀態暫存器(current program status register),可以在任何工作模式下被訪問。 5 個 SPSR:保持程式狀態暫存器(saved program status r

ARM的7種執行模式和37個暫存器

ARM的7種工作模式 包括使用者模式和特權模式二大類,其中特權模式又分為系統模式和異常模式。CPU每次只能執行在一種工作模式下,各種模式之間的切換可以是程式設計師通過程式碼主動切換(通過程式狀態暫存器CPSR)也可以是CPU自己在某種情況下自動切換。在每種模式下最多隻能看到18個暫存器,其他

計算機儲存結構分析(暫存器,記憶體,快取,硬碟)

前言 一個計算機包含多種儲存器比如:暫存器、快取記憶體、記憶體、硬碟、光碟等,為啥有這麼多種儲存方式,對於不太瞭解的人,總是覺得雲裡霧裡的,搞不明白原因。

第005課 計算機單位和暫存器

計算機單位換算 單位換算 微米,毫米,釐米,分米....... 1Byte = 8Bit 1M = 1024KB 1G = 1024M 1個字母在計算機中佔一個位元組,8個位。 位寬 1個位元組 256 2個位元組 65

實現BX的內容加上123 並把和送到暫存器AX

① 一條指令 1 LEA AX,[BX+123] ②兩條指令 1 ADD BX,123 2 MOV AX,BX Tips: LEA指令與MOV指令的區別: ① MOV指令是 資料 傳送指令-------傳送

中斷,異常,系統呼叫,程序切換時的堆疊變化和暫存器儲存

1. 中斷,異常,系統呼叫相同: CPU自動壓入: ss 執行級別提升時需切換堆疊,因此多壓入