JTAG各類介面針腳定義、含義以及SWD接線方式

JTAG有10pin的、14pin的和20pin的,儘管引腳數和引腳的排列順序不同,但是其中有一些引腳是一樣的,各個引腳的定義如下。

一、引腳定義

Test Clock Input (TCK) -----強制要求1

TCK在IEEE1149.1標準裡是強制要求的。TCK為TAP的操作提供了一個獨立的、基本的時鐘訊號,TAP的所有操作都是通過這個時鐘訊號來驅動的。

Test Mode Selection Input (TMS) -----強制要求2

TMS訊號在TCK的上升沿有效。TMS在IEEE1149.1標準裡是強制要求的。TMS訊號用來控制TAP狀態機的轉換。通過TMS訊號,可以控制TAP在不同的狀態間相互轉換。

Test Data Input (TDI) -----強制要求3

TDI在IEEE1149.1標準裡是強制要求的。TDI是資料輸入的介面。所有要輸入到特定暫存器的資料都是通過TDI介面一位一位序列輸入的(由TCK驅動)。

Test Data Output (TDO) -----強制要求4

TDO在IEEE1149.1標準裡是強制要求的。TDO是資料輸出的介面。所有要從特定的暫存器中輸出的資料都是通過TDO介面一位一位序列輸出的(由TCK驅動)。

Test Reset Input (TRST) ----可選項1

這個訊號介面在IEEE 1149.1標準裡是可選的,並不是強制要求的。TRST可以用來對TAPController進行復位(初始化)。因為通過TMS也可以對TAP Controll進行復位(初始化)。所以有四線JTAG與五線JTAG之分。

(VTREF) -----強制要求5

介面訊號電平參考電壓一般直接連線Vsupply。這個可以用來確定ARM的JTAG介面使用的邏輯電平(比如3.3V還是5.0V?)

Return Test Clock ( RTCK) ----可選項2

可選項,由目標端反饋給模擬器的時鐘訊號,用來同步TCK訊號的產生,不使用時直接接地。

System Reset ( nSRST)----可選項3

可選項,與目標板上的系統復位訊號相連,可以直接對目標系統復位。同時可以檢測目標系統的復位情況,為了防止誤觸發應在目標端加上適當的上拉電阻。

USER IN

使用者自定義輸入。可以接到一個IO上,用來接受上位機的控制。

USER OUT

使用者自定義輸出。可以接到一個IO上,用來向上位機的反饋一個狀態

由於JTAG經常使用排線連線,為了增強抗干擾能力,在每條訊號線間加上地線就出現了這種20針的介面。但事實上,RTCK、USER IN、USER OUT一般都不使用,於是還有一種14針的介面。對於實際開發應用來說,由於實驗室電源穩定,電磁環境較好,干擾不大。

二、20、14、10pin JTAG的引腳名稱與序號對應關係

值得注意的是,不同的IC公司會自己定義自家產品專屬的Jtag頭,來下載或除錯程式。嵌入式系統中常用的20、14、10pin JTAG的訊號排列如下:

需要說明的是,上述Jtag頭的管腳名稱是對IC而言的。例如TDI腳,表示該腳應該與IC上的TDI腳相連,而不是表示資料從該腳進入download cable。

實際上10針的只需要接4根線,4號是自連回路,不需要接,1,2接的都是1管腳,而8,10接的是GND,也可以不接。

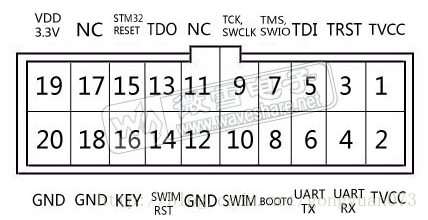

附轉接板電路:

JTAG介面的SWD接線方式

JTAG引腳示意圖:

一、SWD 和傳統的除錯方式區別

1. SWD 模式比 JTAG 在高速模式下面更加可靠

2. GPIO 剛好缺一個的時候, 可以使用 SWD 模擬, 這種模式支援更少的引腳

3. 在板子的體積有限的時候推薦使用 SWD 模式

二、模擬器對 SWD 模式支援情況

1. 市面上的常用模擬器對 SWD 模式支援情況

JLINKV8 非常好的支援 SWD 模擬模式, 速度可以到 10M

ULINK2 非常好的支援 SWD 模式, 速度可以達到 10M

2. SWD 硬體介面上的不同

(1) JLINKV7 需要的硬體介面為: GND, RST, SWDIO, SWDCLK

(2) JLINKV8 需要的硬體介面為: VCC, GND, RST, SWDIO, SWDCLK (注:下面有我自己用JLINKV8的實際連線及相應實驗結果)

(3) ULINK1 不支援 SWD 模式

(4) ULINK2 需要的硬體介面為: GND, RST, SWDIO, SWDCLK

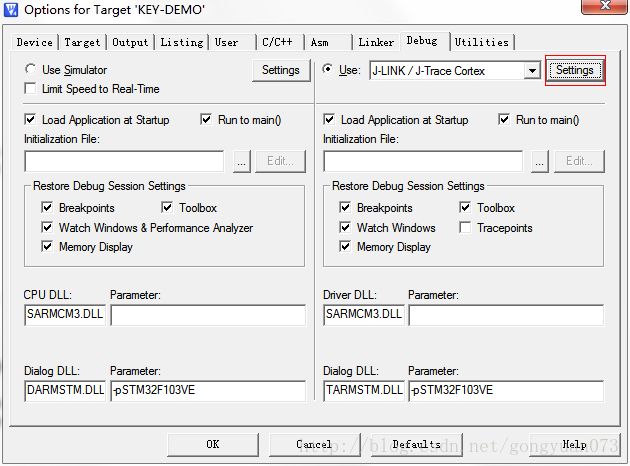

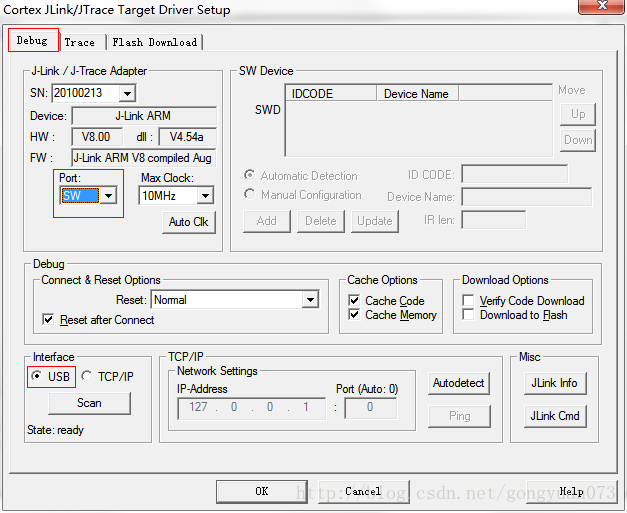

三、在 MDK 中SWD 模式的設定

正常的JTAG需要20管腳,而J-Link 的SWD只需要2根線(PA13/JTMS/SWDIO、PA14/JTCK/SWCLK)就夠了(加上電源線也就4根),這樣就節省了3個I/O口(PA15/JTDI、PB3/JTDO、PB4/JNTRST)為其它所用,並且可節省一部分板子的空間(只需4個口就可以了)

第一步:

第二步:

另外, JTAG引腳可以被複用為IO口,但是這樣一來,JLINK就不能夠連上晶片了。解決的方法有兩種:

(1)另寫一段程式,不要將JTAG複用為I/O口,然後將這段程式用串列埠工具寫入晶片中

(2)將BOOT0/BOOT1設定成為內部RAM啟動,那麼上電後就不會執行FLASH中的程式,這樣JLINK就能順利“接管”JTAG引腳

例項應用:

10針JTAG與20針JTAG的連線:

下面說一下接法,其實根本不需要什麼轉接板什麼的,直接把相應的幾根線對接就可以用了,所以要參考電路圖,上面為TQ2440開發板的JTAG電路圖,下面為JLINK的20針電路圖,下面的JLINKV7電路圖是標準介面,網上到處都能找到

10針JTAG針序 | 20針JTAG針序 | 訊號 |

| 1,2 | 1 | VTref |

| - | 2 | NC |

| 3 | 3 | nTRST |

| - | 4 | GND |

| 5 | 5 | TDI |

| - | 6 | GND |

| 7 | 7 | TMS |

| 8 | 8 | GND |

| 9 | 9 | TCK |

| 10 | 10 | GND |

| - | 11 | RTCK |

| - | 12 | GND |

| 6 | 13 | TDO |

| - | 14 | GND |

| 4 | 15 | RESET |

| - | 16 | GND |

| - | 17 | DBGRQ |

| - | 18 | GND |

| - | 19 | 5V-Supply |

| - | 20 | GND |

實際上只需要接4跟線,4號是自連回路,不需要接,1,2接的都是1管腳,而8,10接的是GND,也可以不接