nandflash驅動詳解

阿新 • • 發佈:2019-01-24

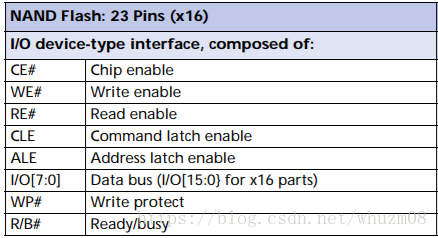

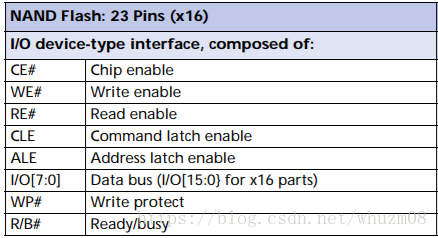

對nandflash儲存原理不瞭解的請先閱讀《flash memory技術》架構圖+ ----------- +系統匯流排+ ------------------- + CLE,io [8:0] + ----- -------------- + | cpu |←------------→| nand控制器| ←--------------→| nand flash |+ ----------- + + ------------------- + + --------------- ---- +cpu通過系統匯流排訪問nand控制器暫存器,設定讀寫flash的命令和相應的地址,當完成操作時nand controler發出中斷,也可以通過查詢nand controler的狀態暫存器來獲取操作狀態,nand controler將相應的命令狀態為nand flash能夠理解的時序

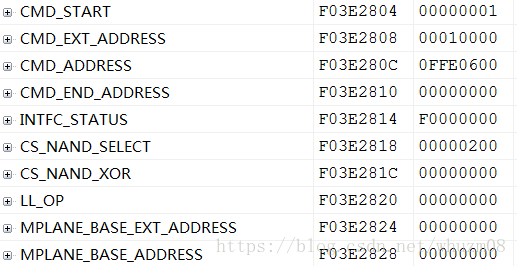

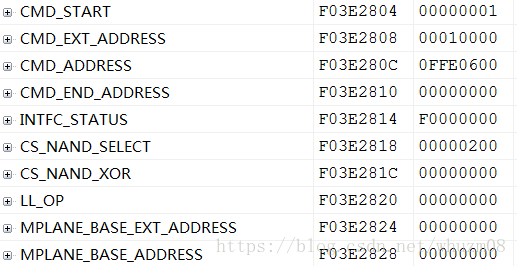

如果支援直接訪問模式,可以將nandflash直接對映到實體地址空間,通過XOR可以對映到不同的物理空間,這樣就可以直接從nandflash執行程式了(注意不能寫,因為寫之前必須要先擦除)NAND直接存取模式/ *禁止所有NAND CS的直接定址+ XOR * / BDEV_UNSET(BCHP_NAND_CS_NAND_SELECT,0xff); BDEV_UNSET(BCHP_NAND_CS_NAND_XOR,0xff);nandflash控制器全域性暫存器

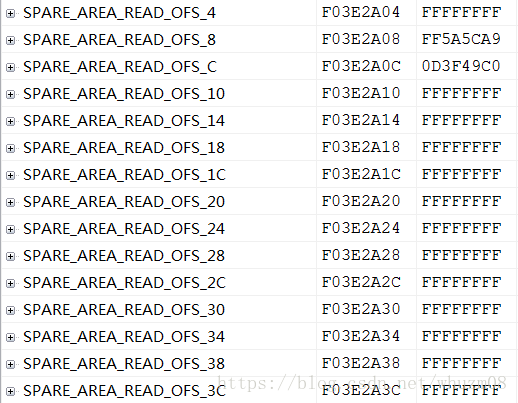

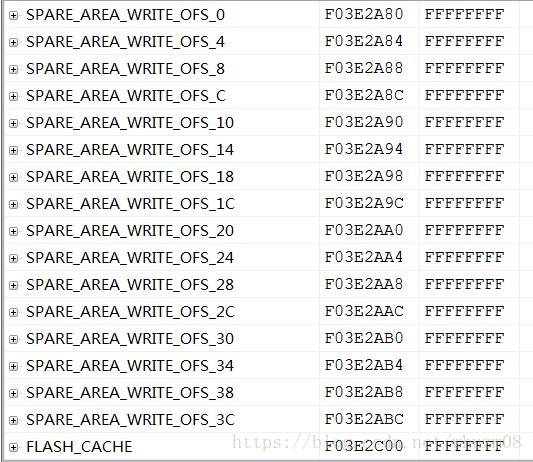

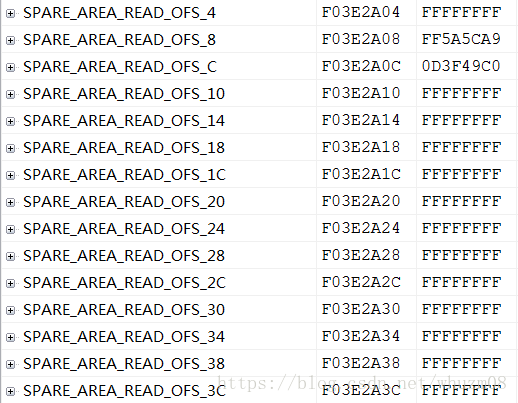

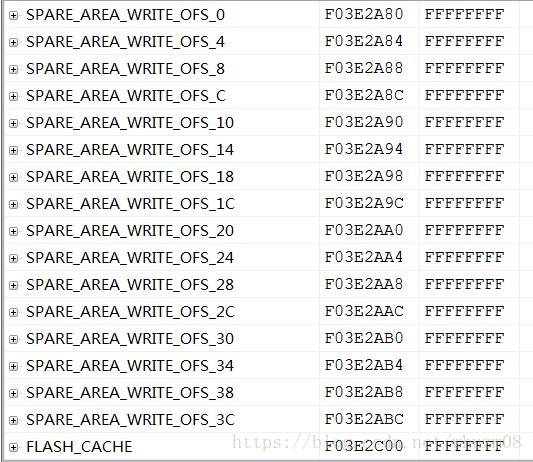

oob:spare_area 0x40 = 64byte資料:flash_cache 128位元組= 128 * 4 = 512位元組

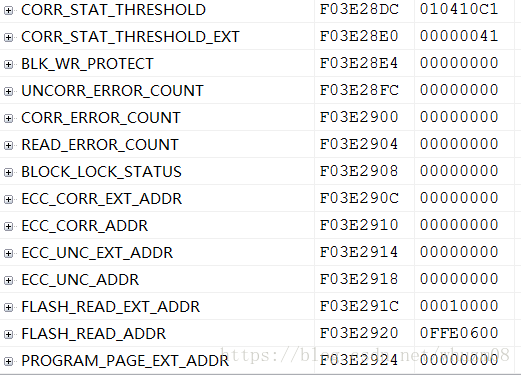

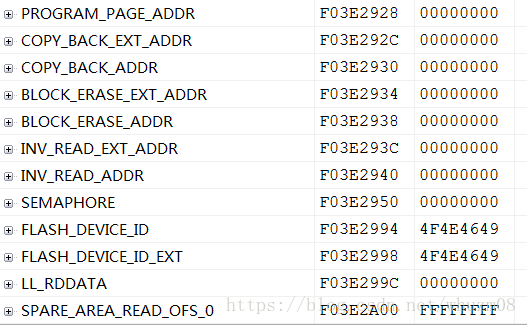

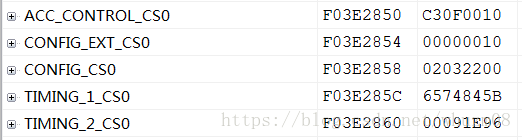

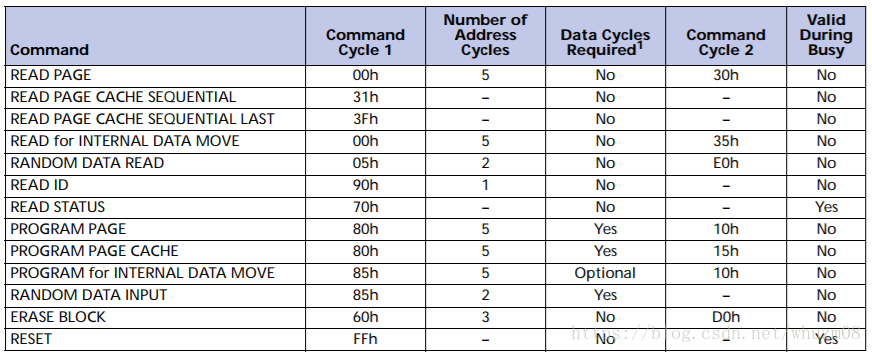

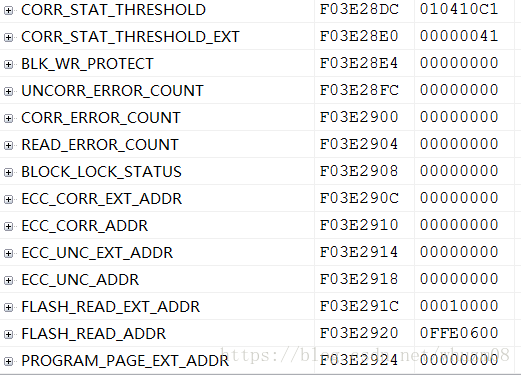

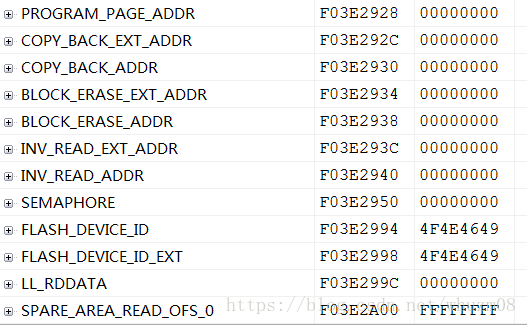

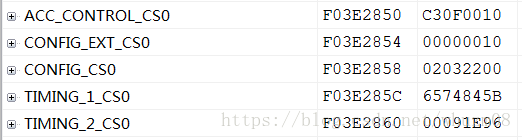

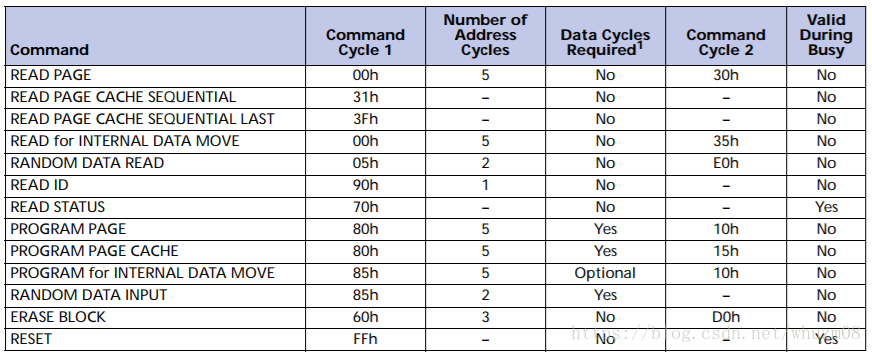

oob:spare_area 0x40 = 64byte資料:flash_cache 128位元組= 128 * 4 = 512位元組  Brcm nandflash控制器最多支援7個銀行 BCHP_NAND_ACC_CONTROL_CS0 Nand Flash訪問控制 RD_ECC_EN [31:31] RW為PAGE_READ操作啟用ECC校正。重置值:0x1WR_ECC_EN [30:30] RW為任何塊啟用對PROGRAM_PAGE或PROGRAM_SPARE_AREA操作的ECC校驗位生成。當該位置位時,ECC位元組將被忽略。選擇漢明碼時的ECC位元組位置是SPARE_AREA_WRITE_OFS_4和SPARE_AREA_WRITE_OFS_8暫存器的BYTE_OFS_6,BYTE_OFS_7和BYTE_OFS_8的3個位元組。選擇BCH碼時的ECC位元組位置是備用區域的最後位元組位置。例如,如果SPARE_AREA_SIZE = 16且ECC_LEVEL = 4(7個ECC位元組),則ECC位元組位置是BYTE_OFS_9到BYTE_OFS_15中的16個位元組中的最後7個。當此位設定為PROGRAM_PAGE操作時,ECC位元組將由H / W生成的ECC校驗位元組替代; 對於PROGRAM_SPARE_AREA操作,ECC位元組將被FFh替換。重置值:0x1CE_CARE [29:29] RW此欄位僅適用於CE護理裝置。當設定為1時,EBI_CS [n]將在NAND_RBb低電平期間保持置位狀態(器件忙)。在此期間,其他晶片選擇中的器件無法訪問。預設設定為0以獲得更好的效能。復位值:0x0保留 [28:28] RWX RD_ERASED_ECC_EN [27:27] RW確定擦除頁面中的PAGE_READ操作是否會生成不可糾正的ECC錯誤。(一個Erased Page被定義為全部512個數據位元組,所有3個ECC位元組都包含0xFF,剩餘的Spare Area位元組未被考慮)。無論該位的狀態如何,如果ECC被RD_ECC_EN = 0或RD_ECC_BLK0_EN = 0禁用,將不會生成錯誤。1 =從擦除頁讀取生成ECC錯誤。0 =從擦除頁讀取不會產生ECC錯誤。復位值:0x0PARTIAL_PAGE_EN [26:26] RW啟用部分頁面程式設計。建議清除此位以提高效能並防止部分頁面程式設計,這是許多nand快閃記憶體裝置所禁止的。 當該位置位且軟體啟動PROGRAM_PAGE操作時,硬體將資料直接寫入快閃記憶體單元。當該位清零並且軟體啟動PROGRAM_PAGE操作時,硬體將資料移入NAND Flash裝置快取並返回空閒狀態。只有當NAND_CMD_ADDRESS指向頁面的最後512位元組扇區時,硬體才會將資料程式設計到快閃記憶體單元中。小頁面裝置會忽略該位。復位值:0x0WR_PREEMPT_EN [25:25] RW使能其他EBI或PCI週期的寫突發操作的搶佔。當另一個請求者試圖使用匯流排時,這允許將來自Flash外部匯流排的長512位元組突發分成16次傳輸的多個突發。重置值:0x1PAGE_HIT_EN [24:24] RW啟用Flash頁面檢測檢測,作為頁面大小大於512B的頁面內512位元組讀取的優化。該位僅為大頁面裝置提供效能優化。如果設定,並且硬體發現讀取未命中,但是從已經讀入FlashCache的相同頁面,它將簡單地使用快閃記憶體的隨機讀取操作來節省時間。重置值:0x1PREFETCH_EN [23:23] RW硬體自動讀取當前頁面讀取命令地址的下一個512B或1KB資料,扇區大小取決於SECTOR_SIZE_1K位。啟用此位可提高讀取連續地址的效能。預取對軟體是透明的。CTLR_READY位始終指示當前地址讀取完成。注:建議將此位設定為長連續讀取,例如DMA傳輸。如果讀取地址不連續,則由於後臺預取,軟體可能會看到更長的繁忙時間和效能下降。注:僅當ECC_type為BCH時才支援預取。復位值:0x0CACHE_MODE_EN [22:22] RW啟用程式頁面或頁面讀取快取模式。如果置位,並且發出頁面讀取命令,硬體將啟動具有快取模式操作碼31h的頁面讀操作。如果置位,並且發出程式頁命令,則硬體以快取記憶體模式操作碼15h結束程式頁操作。快取模式通過連續頁面訪問跳過快閃記憶體裝置繁忙時間來提高效能。例如:第n,n + 1,n + 2,n + 3,n + 4 ... n + m的DMA傳輸注:硬體不檢測頁面地址的連貫性。軟體需要管理設定這一點。要恢復正常的頁面讀取和程式頁面命令,請取消設定此位。復位值:0x0保留 [21:21] RWX ECC_LEVEL [20:16] RW設定每512個數據位元組可以糾正的編碼型別和位數。定義T:=每扇區可修正的位數。當SECTOR_SIZE_1K = 0時,則T = ECC_LEVEL當SECTOR_SIZE_1K = 1時,則T = ECC_LEVEL * 2異常是SECTOR_SIZE_1K = 0,SPARE_AREA_SIZE = 16,ECC_LEVEL = 15,則T = 1(海明模式)保留 [15:8] RWX SECTOR_SIZE_1K [7:7] RW定義ECC碼字大小,也稱為扇區大小。注意:當使用1k位元組扇區大小時,ECC_LEVEL欄位指定T值的一半,漢明碼不可用。請參閱ECC_LEVEL說明中顯示的表。注意:當使用1k位元組扇區大小時,必須清除PARTIAL_PAGE_EN位,並且快閃記憶體頁面大小必須大於512。0 512位元組1個1k位元組當strap_nand_flash = 1時,該欄位將根據選定的ECC級別繫結在strap_nand_ecc_level [n:0]上進行初始化。復位值:0x0SPARE_AREA_SIZE [6:0] RW表示每512個數據位元組包含在快閃記憶體裝置中的備用區位元組數。有效設定是16到64(含)。對於16位寬的NAND快閃記憶體器件,此欄位必須包含偶數。對於大頁面裝置(頁面大小為2kB或更大),每頁的備用區域除以每頁的扇區數量。 例如,(2kB + 64B)頁面大小和512B扇區大小每頁有4個扇區,每頁全部64位元組備用區域將被分成4個相等的部分,每個16位元組; 並且這些部分中的每一個都將被不同的部門使用。選擇漢明碼時的ECC位元組位置是SPARE_AREA_WRITE_OFS_4和SPARE_AREA_WRITE_OFS_8暫存器的BYTE_OFS_6,BYTE_OFS_7和BYTE_OFS_8的3個位元組。選擇BCH碼時的ECC位元組位置是該特定扇區的備用區的最後一個位元組位置。 例如,如果SPARE_AREA_SIZE = 16且ECC_LEVEL = 4(7個ECC位元組),則ECC位元組位置是BYTE_OFS_9到BYTE_OFS_15中的16個位元組中的最後7個。當SECTOR_SIZE_1K = 1時,該欄位仍指定每512個備用位元組。當strap_nand_flash = 1時,該欄位將根據選定的ECC級別繫結在strap_nand_ecc_level [n:0]上進行初始化。重置值:0x10因為ECC校驗是由控制器自動完成的,那麼就必須讓控制器知道該bank上的nandflash使用的ECC LEVEL和SPARE_AREA_SIZE,這樣控制器就能知道ECC位元組在SPARE_AREA_READ_OFS_0中的位置.ECC位元組在nandflash中的位置理論上來說跟nandflash沒有多大關係,因為nandflash對ECC位元組是無知的,它由控制器來使用,nandflash會根據本身工藝推薦ECC LEVEL,理論上大於這個值都是可行的。BCHP_NAND_CONFIG_EXT_CS0 Nand Flash配置擴充套件 快閃記憶體裝置介面引數。根據NAND_CMD_EXT_ADDRESS暫存器中的CS_SEL值,硬體會根據剛剛復位後從外部Nand Flash器件讀取的DeviceID或ONFI引數值將預設值裝入此暫存器。保留[31:12] RWX BLOCK_SIZE [11:4] RW塊大小(以位元組為單位)。(注意:該欄位僅用於確定目標地址是否位於快閃記憶體的塊0中,以便在WR_PROTECT_BLK0位置位時知道是否應用防寫,或者當RD_ECC_BLK0_EN位為是時是否執行ECC糾正組。)值名稱0 BK_SIZE_8KB1 BK_SIZE_16KB2 BK_SIZE_32KB3 BK_SIZE_64KB4 BK_SIZE_128KB5 BK_SIZE_256KB6 BK_SIZE_512KB7 BK_SIZE_1024KB8 BK_SIZE_2048KB9 BK_SIZE_4096KB10 BK_SIZE_8192KBPAGE_SIZE [3:0] RW頁面大小(以位元組為單位)。值名稱說明0 PG_SIZE_512 512位元組。1 PG_SIZE_1KB 1k位元組。2 PG_SIZE_2KB 2k位元組。3 PG_SIZE_4KB 4k位元組。4 PG_SIZE_8KB 8k位元組。5 PG_SIZE_16KB 16k位元組。BCHP_NAND_CONFIG_CS0 Nand Flash配置快閃記憶體裝置介面引數。根據NAND_CMD_EXT_ADDRESS暫存器中的CS_SEL值,硬體會根據剛剛復位後從外部Nand Flash器件讀取的DeviceID或ONFI引數值將預設值裝入此暫存器。CONFIG_LOCK [31:31] RW當該位設定為1時,該暫存器和CONFIG_EXT暫存器變為只讀暫存器,防止進一步寫入該暫存器和CONFIG_EXT暫存器。一旦設定,該位只能通過復位清零。復位值:0x0保留[30:28] RWX DEVICE_SIZE [27:24] RW裝置大小(以位元組為單位)。值名稱0 DVC_SIZE_4MB1 DVC_SIZE_8MB2 DVC_SIZE_16MB3 DVC_SIZE_32MB4 DVC_SIZE_64MB5 DVC_SIZE_128MB6 DVC_SIZE_256MB7 DVC_SIZE_512MB8 DVC_SIZE_1GB9 DVC_SIZE_2GB10 DVC_SIZE_4GB11 DVC_SIZE_8GB12 DVC_SIZE_16GB13 DVC_SIZE_32GB14 DVC_SIZE_64GB15 DVC_SIZE_128GBDEVICE_WIDTH [23:23] RW裝置I / O資料匯流排寬度(以位為單位)。值名稱0 DVC_WIDTH_81 DVC_WIDTH_16保留[22:19] RWX FUL_ADR_BYTES [18:16] RW在裝置內傳送到Flash的完整地址的地址位元組數。當PAGE_SIZE> 512B時,FUL_ADR_BYTES = COL_ADR_BYTES + BLK_ADR_BYTES。當PAGE_SIZE = 512B時,FUL_ADR_BYTES = 1 + BLK_ADR_BYTES。該欄位通過繫結或AUTO_DEVICE_ID_CONFIG初始化。保留[15:15] RWX COL_ADR_BYTES [14:12] RW傳送到Flash以指定頁面內隨機資料訪問的列地址的地址位元組數。該欄位僅用於頁面大小大於512B的頁面,用於頁面內的隨機定址,以定址PROGRAM_PAGE和PAGE_READ命令的備用區域。2為512B <=頁面大小<= 32KB該欄位通過繫結或AUTO_DEVICE_ID_CONFIG初始化。保留[11:11] RWX BLK_ADR_BYTES [10:8] RW傳送到Flash以指定行和塊的地址位元組數。該欄位相當於NAND快閃記憶體資料表中的頁面地址+塊地址。該欄位僅用於BLOCK_ERASE和BLOCKS_UNLOCK命令。該欄位通過繫結或AUTO_DEVICE_ID_CONFIG初始化。保留[7:0] RWX BCHP_NAND_TIMING_1_CS0 Nand Flash時序引數1 快閃記憶體裝置介面時序引數。時序以內部108 MHz時鐘(9.26 ns)或內部216 MHz時鐘(4.63 ns)為單位指定,具體取決於TIMING_2.CLK_SELECT的值。任何時間欄位中的最小值是2(2個時鐘)。tWP [31:28] RW時鐘數WE低脈衝寬度。重置值:0x6tWH [27:24] RW片段數WE高脈衝寬度。(除了ALE較高時,在這種情況下,tALH控制WE高脈衝寬度而不是tWH。)重置值:0x5tRP [23:20] RW時鐘數RE低脈衝寬度。重置值:0x7tREH [19:16] RW時鐘數RE高脈衝寬度。重置值:0x4tCS [15:12] RW從CE低到第一個WE低的時鐘數。注意:當CLK_SELECT = CLK_108時,該暫存器欄位中的值將被硬體加倍,當CLK_SELECT = CLK_216時,該值將被硬體加倍。重置值:0x8tCLH [11:8] RW從WE高到CLE低的塊數。重置值:0x4tALH [7:4] RW從WE高到ALE低的時針數量。而且,當ALE高時,螢幕的數量WE高脈衝寬度。該位應該被設定為來自快閃記憶體製造商資料表的tWH和tALH之間的較大值。重置值:0x5tADL [3:0] RW從最後一個addr到第一次資料寫入的時鐘片數。注意:當CLK_SELECT = CLK_108時,該暫存器欄位中的值將被硬體加倍,當CLK_SELECT = CLK_216時,該值將被硬體加倍。復位值:0xBBCHP_NAND_TIMING_2_CS0 Nand Flash時序引數2 快閃記憶體裝置介面時序引數。時序以內部108 MHz時鐘(9.26 ns)或內部216 MHz時鐘(4.63 ns)為單位指定,具體取決於TIMING_2.CLK_SELECT的值。任何時間欄位中的最小值是2(2個時鐘)。CLK_SELECT [31:31] RW確定NAND_TIMING_1和NAND_TIMING_2中的引數用於nand快閃記憶體定時狀態機的時鐘。值名稱說明0 CLK_108內部108 MHz時鐘。1 CLK_216內部216 MHz時鐘。重置值:CLK_108保留[30:20] RWX tCCS [19:16] RW更改列命令設定時間。注:當CLK_SELECT = CLK_108時,硬體將該暫存器欄位中的值翻兩倍,並且當CLK_SELECT = CLK_216時,該值將由硬體八倍。重置值:0x9保留[15:13] RWX tWB [12:9] RW在硬體開始取樣R / B引腳之前,CE的高電平時鐘數。注意:當CLK_SELECT = CLK_108時,該暫存器欄位中的值將被硬體加倍,當CLK_SELECT = CLK_216時,該值將被硬體加倍。復位值:0xFtWHR [8:4] RW從WE高到RE低的時鐘片數。此引數僅用於狀態讀取和裝置ID讀取操作。注意:當CLK_SELECT = CLK_108時,該暫存器欄位中的值將被硬體加倍,當CLK_SELECT = CLK_216時,該值將被硬體加倍。重置值:0x9tREAD [3:0] RW RE低後取樣讀取資料之前等待的時鐘數。為獲得最佳效能,應通過將nns快閃記憶體器件的RE存取時間(tREA)加上17ns,然後將總和除以CLK_SELECT所選的時鐘週期,然後將其四捨五入至下一較大整數來計算此引數。例如,如果器件tREA = 20ns並且CLK_SELECT = 1(216MHz => 4.63ns):tREAD =(20ns + 17ns)/4.63ns=7.99(四捨五入)=> 8。tREAD的最大值是(tRP + tREH)。重置值:0x6操作時序在程式設計操作中,要被程式設計的資料在WE#的上升沿被同步到資料暫存器中。資料以類似的方式通過讀使能(RE#)訊號從資料暫存器輸出,該訊號負責輸出當前資料並遞增到下一個位置。WE#和RE#時鐘每次傳輸可以執行25ns。當RE#或晶片使能(CE#)未置為低電平時,輸出緩衝器為三態。CE#和RE#的這種組合激活了輸出緩衝器,使NAND Flash能夠與其他型別的儲存器(如NOR快閃記憶體,SRAM或DRAM)共享資料匯流排。這個功能有時被稱為“晶片使能不關心”。在RE#為低時,讀使能,輸出緩衝器直接放置在io上,可跟著變化。所有的NAND Flash操作都是通過發出一個命令週期來啟動的。這是通過將命令放在I / O [7:0]上,驅動CE#為低電平並且為高電平,然後發出WE#時鐘來完成的。命令,地址和資料在WE#的上升沿時鐘輸入NAND快閃記憶體器件,大多數命令需要多個地址週期,然後是第二個命令週期。除RESET和READ STATUS命令外,當裝置忙時不應發出新命令。支援的命令:

Brcm nandflash控制器最多支援7個銀行 BCHP_NAND_ACC_CONTROL_CS0 Nand Flash訪問控制 RD_ECC_EN [31:31] RW為PAGE_READ操作啟用ECC校正。重置值:0x1WR_ECC_EN [30:30] RW為任何塊啟用對PROGRAM_PAGE或PROGRAM_SPARE_AREA操作的ECC校驗位生成。當該位置位時,ECC位元組將被忽略。選擇漢明碼時的ECC位元組位置是SPARE_AREA_WRITE_OFS_4和SPARE_AREA_WRITE_OFS_8暫存器的BYTE_OFS_6,BYTE_OFS_7和BYTE_OFS_8的3個位元組。選擇BCH碼時的ECC位元組位置是備用區域的最後位元組位置。例如,如果SPARE_AREA_SIZE = 16且ECC_LEVEL = 4(7個ECC位元組),則ECC位元組位置是BYTE_OFS_9到BYTE_OFS_15中的16個位元組中的最後7個。當此位設定為PROGRAM_PAGE操作時,ECC位元組將由H / W生成的ECC校驗位元組替代; 對於PROGRAM_SPARE_AREA操作,ECC位元組將被FFh替換。重置值:0x1CE_CARE [29:29] RW此欄位僅適用於CE護理裝置。當設定為1時,EBI_CS [n]將在NAND_RBb低電平期間保持置位狀態(器件忙)。在此期間,其他晶片選擇中的器件無法訪問。預設設定為0以獲得更好的效能。復位值:0x0保留 [28:28] RWX RD_ERASED_ECC_EN [27:27] RW確定擦除頁面中的PAGE_READ操作是否會生成不可糾正的ECC錯誤。(一個Erased Page被定義為全部512個數據位元組,所有3個ECC位元組都包含0xFF,剩餘的Spare Area位元組未被考慮)。無論該位的狀態如何,如果ECC被RD_ECC_EN = 0或RD_ECC_BLK0_EN = 0禁用,將不會生成錯誤。1 =從擦除頁讀取生成ECC錯誤。0 =從擦除頁讀取不會產生ECC錯誤。復位值:0x0PARTIAL_PAGE_EN [26:26] RW啟用部分頁面程式設計。建議清除此位以提高效能並防止部分頁面程式設計,這是許多nand快閃記憶體裝置所禁止的。 當該位置位且軟體啟動PROGRAM_PAGE操作時,硬體將資料直接寫入快閃記憶體單元。當該位清零並且軟體啟動PROGRAM_PAGE操作時,硬體將資料移入NAND Flash裝置快取並返回空閒狀態。只有當NAND_CMD_ADDRESS指向頁面的最後512位元組扇區時,硬體才會將資料程式設計到快閃記憶體單元中。小頁面裝置會忽略該位。復位值:0x0WR_PREEMPT_EN [25:25] RW使能其他EBI或PCI週期的寫突發操作的搶佔。當另一個請求者試圖使用匯流排時,這允許將來自Flash外部匯流排的長512位元組突發分成16次傳輸的多個突發。重置值:0x1PAGE_HIT_EN [24:24] RW啟用Flash頁面檢測檢測,作為頁面大小大於512B的頁面內512位元組讀取的優化。該位僅為大頁面裝置提供效能優化。如果設定,並且硬體發現讀取未命中,但是從已經讀入FlashCache的相同頁面,它將簡單地使用快閃記憶體的隨機讀取操作來節省時間。重置值:0x1PREFETCH_EN [23:23] RW硬體自動讀取當前頁面讀取命令地址的下一個512B或1KB資料,扇區大小取決於SECTOR_SIZE_1K位。啟用此位可提高讀取連續地址的效能。預取對軟體是透明的。CTLR_READY位始終指示當前地址讀取完成。注:建議將此位設定為長連續讀取,例如DMA傳輸。如果讀取地址不連續,則由於後臺預取,軟體可能會看到更長的繁忙時間和效能下降。注:僅當ECC_type為BCH時才支援預取。復位值:0x0CACHE_MODE_EN [22:22] RW啟用程式頁面或頁面讀取快取模式。如果置位,並且發出頁面讀取命令,硬體將啟動具有快取模式操作碼31h的頁面讀操作。如果置位,並且發出程式頁命令,則硬體以快取記憶體模式操作碼15h結束程式頁操作。快取模式通過連續頁面訪問跳過快閃記憶體裝置繁忙時間來提高效能。例如:第n,n + 1,n + 2,n + 3,n + 4 ... n + m的DMA傳輸注:硬體不檢測頁面地址的連貫性。軟體需要管理設定這一點。要恢復正常的頁面讀取和程式頁面命令,請取消設定此位。復位值:0x0保留 [21:21] RWX ECC_LEVEL [20:16] RW設定每512個數據位元組可以糾正的編碼型別和位數。定義T:=每扇區可修正的位數。當SECTOR_SIZE_1K = 0時,則T = ECC_LEVEL當SECTOR_SIZE_1K = 1時,則T = ECC_LEVEL * 2異常是SECTOR_SIZE_1K = 0,SPARE_AREA_SIZE = 16,ECC_LEVEL = 15,則T = 1(海明模式)保留 [15:8] RWX SECTOR_SIZE_1K [7:7] RW定義ECC碼字大小,也稱為扇區大小。注意:當使用1k位元組扇區大小時,ECC_LEVEL欄位指定T值的一半,漢明碼不可用。請參閱ECC_LEVEL說明中顯示的表。注意:當使用1k位元組扇區大小時,必須清除PARTIAL_PAGE_EN位,並且快閃記憶體頁面大小必須大於512。0 512位元組1個1k位元組當strap_nand_flash = 1時,該欄位將根據選定的ECC級別繫結在strap_nand_ecc_level [n:0]上進行初始化。復位值:0x0SPARE_AREA_SIZE [6:0] RW表示每512個數據位元組包含在快閃記憶體裝置中的備用區位元組數。有效設定是16到64(含)。對於16位寬的NAND快閃記憶體器件,此欄位必須包含偶數。對於大頁面裝置(頁面大小為2kB或更大),每頁的備用區域除以每頁的扇區數量。 例如,(2kB + 64B)頁面大小和512B扇區大小每頁有4個扇區,每頁全部64位元組備用區域將被分成4個相等的部分,每個16位元組; 並且這些部分中的每一個都將被不同的部門使用。選擇漢明碼時的ECC位元組位置是SPARE_AREA_WRITE_OFS_4和SPARE_AREA_WRITE_OFS_8暫存器的BYTE_OFS_6,BYTE_OFS_7和BYTE_OFS_8的3個位元組。選擇BCH碼時的ECC位元組位置是該特定扇區的備用區的最後一個位元組位置。 例如,如果SPARE_AREA_SIZE = 16且ECC_LEVEL = 4(7個ECC位元組),則ECC位元組位置是BYTE_OFS_9到BYTE_OFS_15中的16個位元組中的最後7個。當SECTOR_SIZE_1K = 1時,該欄位仍指定每512個備用位元組。當strap_nand_flash = 1時,該欄位將根據選定的ECC級別繫結在strap_nand_ecc_level [n:0]上進行初始化。重置值:0x10因為ECC校驗是由控制器自動完成的,那麼就必須讓控制器知道該bank上的nandflash使用的ECC LEVEL和SPARE_AREA_SIZE,這樣控制器就能知道ECC位元組在SPARE_AREA_READ_OFS_0中的位置.ECC位元組在nandflash中的位置理論上來說跟nandflash沒有多大關係,因為nandflash對ECC位元組是無知的,它由控制器來使用,nandflash會根據本身工藝推薦ECC LEVEL,理論上大於這個值都是可行的。BCHP_NAND_CONFIG_EXT_CS0 Nand Flash配置擴充套件 快閃記憶體裝置介面引數。根據NAND_CMD_EXT_ADDRESS暫存器中的CS_SEL值,硬體會根據剛剛復位後從外部Nand Flash器件讀取的DeviceID或ONFI引數值將預設值裝入此暫存器。保留[31:12] RWX BLOCK_SIZE [11:4] RW塊大小(以位元組為單位)。(注意:該欄位僅用於確定目標地址是否位於快閃記憶體的塊0中,以便在WR_PROTECT_BLK0位置位時知道是否應用防寫,或者當RD_ECC_BLK0_EN位為是時是否執行ECC糾正組。)值名稱0 BK_SIZE_8KB1 BK_SIZE_16KB2 BK_SIZE_32KB3 BK_SIZE_64KB4 BK_SIZE_128KB5 BK_SIZE_256KB6 BK_SIZE_512KB7 BK_SIZE_1024KB8 BK_SIZE_2048KB9 BK_SIZE_4096KB10 BK_SIZE_8192KBPAGE_SIZE [3:0] RW頁面大小(以位元組為單位)。值名稱說明0 PG_SIZE_512 512位元組。1 PG_SIZE_1KB 1k位元組。2 PG_SIZE_2KB 2k位元組。3 PG_SIZE_4KB 4k位元組。4 PG_SIZE_8KB 8k位元組。5 PG_SIZE_16KB 16k位元組。BCHP_NAND_CONFIG_CS0 Nand Flash配置快閃記憶體裝置介面引數。根據NAND_CMD_EXT_ADDRESS暫存器中的CS_SEL值,硬體會根據剛剛復位後從外部Nand Flash器件讀取的DeviceID或ONFI引數值將預設值裝入此暫存器。CONFIG_LOCK [31:31] RW當該位設定為1時,該暫存器和CONFIG_EXT暫存器變為只讀暫存器,防止進一步寫入該暫存器和CONFIG_EXT暫存器。一旦設定,該位只能通過復位清零。復位值:0x0保留[30:28] RWX DEVICE_SIZE [27:24] RW裝置大小(以位元組為單位)。值名稱0 DVC_SIZE_4MB1 DVC_SIZE_8MB2 DVC_SIZE_16MB3 DVC_SIZE_32MB4 DVC_SIZE_64MB5 DVC_SIZE_128MB6 DVC_SIZE_256MB7 DVC_SIZE_512MB8 DVC_SIZE_1GB9 DVC_SIZE_2GB10 DVC_SIZE_4GB11 DVC_SIZE_8GB12 DVC_SIZE_16GB13 DVC_SIZE_32GB14 DVC_SIZE_64GB15 DVC_SIZE_128GBDEVICE_WIDTH [23:23] RW裝置I / O資料匯流排寬度(以位為單位)。值名稱0 DVC_WIDTH_81 DVC_WIDTH_16保留[22:19] RWX FUL_ADR_BYTES [18:16] RW在裝置內傳送到Flash的完整地址的地址位元組數。當PAGE_SIZE> 512B時,FUL_ADR_BYTES = COL_ADR_BYTES + BLK_ADR_BYTES。當PAGE_SIZE = 512B時,FUL_ADR_BYTES = 1 + BLK_ADR_BYTES。該欄位通過繫結或AUTO_DEVICE_ID_CONFIG初始化。保留[15:15] RWX COL_ADR_BYTES [14:12] RW傳送到Flash以指定頁面內隨機資料訪問的列地址的地址位元組數。該欄位僅用於頁面大小大於512B的頁面,用於頁面內的隨機定址,以定址PROGRAM_PAGE和PAGE_READ命令的備用區域。2為512B <=頁面大小<= 32KB該欄位通過繫結或AUTO_DEVICE_ID_CONFIG初始化。保留[11:11] RWX BLK_ADR_BYTES [10:8] RW傳送到Flash以指定行和塊的地址位元組數。該欄位相當於NAND快閃記憶體資料表中的頁面地址+塊地址。該欄位僅用於BLOCK_ERASE和BLOCKS_UNLOCK命令。該欄位通過繫結或AUTO_DEVICE_ID_CONFIG初始化。保留[7:0] RWX BCHP_NAND_TIMING_1_CS0 Nand Flash時序引數1 快閃記憶體裝置介面時序引數。時序以內部108 MHz時鐘(9.26 ns)或內部216 MHz時鐘(4.63 ns)為單位指定,具體取決於TIMING_2.CLK_SELECT的值。任何時間欄位中的最小值是2(2個時鐘)。tWP [31:28] RW時鐘數WE低脈衝寬度。重置值:0x6tWH [27:24] RW片段數WE高脈衝寬度。(除了ALE較高時,在這種情況下,tALH控制WE高脈衝寬度而不是tWH。)重置值:0x5tRP [23:20] RW時鐘數RE低脈衝寬度。重置值:0x7tREH [19:16] RW時鐘數RE高脈衝寬度。重置值:0x4tCS [15:12] RW從CE低到第一個WE低的時鐘數。注意:當CLK_SELECT = CLK_108時,該暫存器欄位中的值將被硬體加倍,當CLK_SELECT = CLK_216時,該值將被硬體加倍。重置值:0x8tCLH [11:8] RW從WE高到CLE低的塊數。重置值:0x4tALH [7:4] RW從WE高到ALE低的時針數量。而且,當ALE高時,螢幕的數量WE高脈衝寬度。該位應該被設定為來自快閃記憶體製造商資料表的tWH和tALH之間的較大值。重置值:0x5tADL [3:0] RW從最後一個addr到第一次資料寫入的時鐘片數。注意:當CLK_SELECT = CLK_108時,該暫存器欄位中的值將被硬體加倍,當CLK_SELECT = CLK_216時,該值將被硬體加倍。復位值:0xBBCHP_NAND_TIMING_2_CS0 Nand Flash時序引數2 快閃記憶體裝置介面時序引數。時序以內部108 MHz時鐘(9.26 ns)或內部216 MHz時鐘(4.63 ns)為單位指定,具體取決於TIMING_2.CLK_SELECT的值。任何時間欄位中的最小值是2(2個時鐘)。CLK_SELECT [31:31] RW確定NAND_TIMING_1和NAND_TIMING_2中的引數用於nand快閃記憶體定時狀態機的時鐘。值名稱說明0 CLK_108內部108 MHz時鐘。1 CLK_216內部216 MHz時鐘。重置值:CLK_108保留[30:20] RWX tCCS [19:16] RW更改列命令設定時間。注:當CLK_SELECT = CLK_108時,硬體將該暫存器欄位中的值翻兩倍,並且當CLK_SELECT = CLK_216時,該值將由硬體八倍。重置值:0x9保留[15:13] RWX tWB [12:9] RW在硬體開始取樣R / B引腳之前,CE的高電平時鐘數。注意:當CLK_SELECT = CLK_108時,該暫存器欄位中的值將被硬體加倍,當CLK_SELECT = CLK_216時,該值將被硬體加倍。復位值:0xFtWHR [8:4] RW從WE高到RE低的時鐘片數。此引數僅用於狀態讀取和裝置ID讀取操作。注意:當CLK_SELECT = CLK_108時,該暫存器欄位中的值將被硬體加倍,當CLK_SELECT = CLK_216時,該值將被硬體加倍。重置值:0x9tREAD [3:0] RW RE低後取樣讀取資料之前等待的時鐘數。為獲得最佳效能,應通過將nns快閃記憶體器件的RE存取時間(tREA)加上17ns,然後將總和除以CLK_SELECT所選的時鐘週期,然後將其四捨五入至下一較大整數來計算此引數。例如,如果器件tREA = 20ns並且CLK_SELECT = 1(216MHz => 4.63ns):tREAD =(20ns + 17ns)/4.63ns=7.99(四捨五入)=> 8。tREAD的最大值是(tRP + tREH)。重置值:0x6操作時序在程式設計操作中,要被程式設計的資料在WE#的上升沿被同步到資料暫存器中。資料以類似的方式通過讀使能(RE#)訊號從資料暫存器輸出,該訊號負責輸出當前資料並遞增到下一個位置。WE#和RE#時鐘每次傳輸可以執行25ns。當RE#或晶片使能(CE#)未置為低電平時,輸出緩衝器為三態。CE#和RE#的這種組合激活了輸出緩衝器,使NAND Flash能夠與其他型別的儲存器(如NOR快閃記憶體,SRAM或DRAM)共享資料匯流排。這個功能有時被稱為“晶片使能不關心”。在RE#為低時,讀使能,輸出緩衝器直接放置在io上,可跟著變化。所有的NAND Flash操作都是通過發出一個命令週期來啟動的。這是通過將命令放在I / O [7:0]上,驅動CE#為低電平並且為高電平,然後發出WE#時鐘來完成的。命令,地址和資料在WE#的上升沿時鐘輸入NAND快閃記憶體器件,大多數命令需要多個地址週期,然後是第二個命令週期。除RESET和READ STATUS命令外,當裝置忙時不應發出新命令。支援的命令:

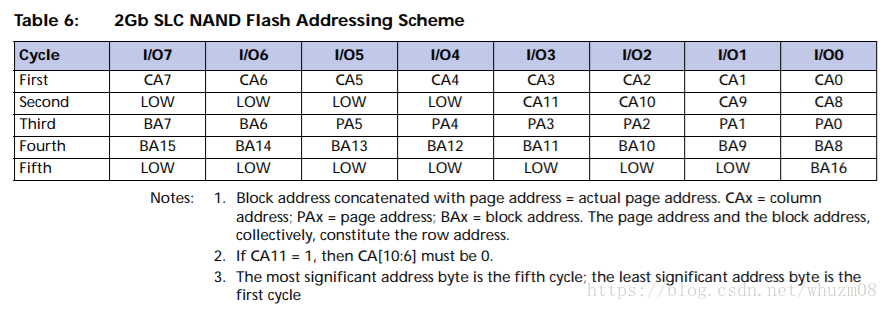

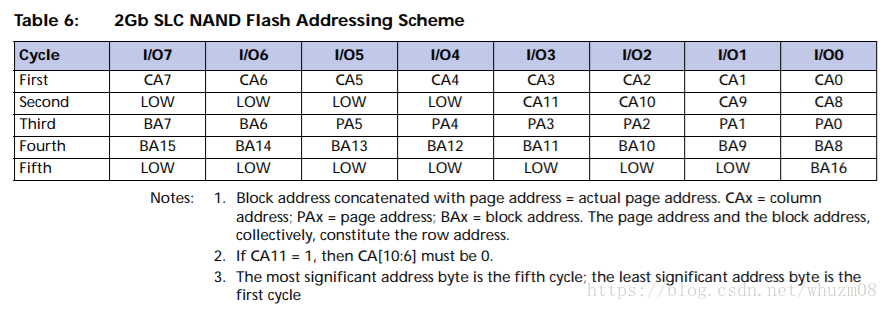

2Gb NAND Flash器件的定址方案如表6所示。第一個和第二個地址週期(或位元組)指定了列地址,它指定了頁面內的起始位元組。最後一列的位置是2112,因此最後一個位置的地址是第二個位元組中的08h,第一個位元組中是3Fh。PA [5:0]指定塊內的頁面地址,BA [16:6]指定塊地址。儘管大多數PROGRAM和READ操作需要完整的5位元組地址,但對於在頁面內隨機訪問資料的操作,只需要第一個和第二個位元組(或迴圈)。BLOCK ERASE操作只需要三個最重要的位元組(第三,第四和第五)來選擇該塊。

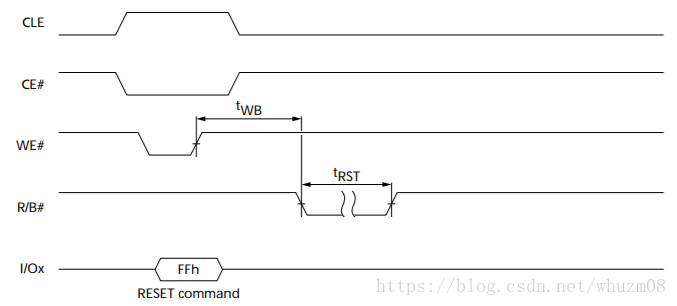

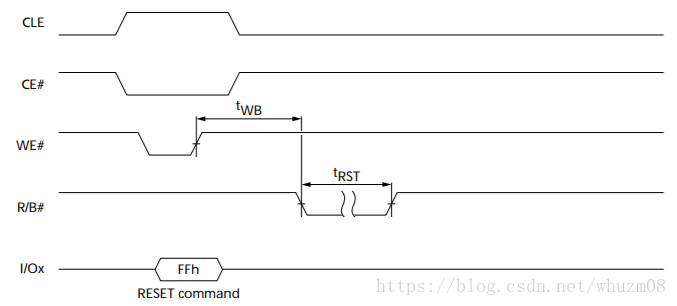

當CA11 = 1時表示訪問oob資料,一般列地址都為0,表示從頁面內偏移0開始訪問整個頁面。復位操作RESET是NAND Flash器件繁忙時可以發出的兩個命令之一。如果裝置正忙於處理先前的命令,則發出RESET命令會中止前一個操作。如果之前的操作是ERASE或PROGRAM命令,則發出RESET命令會過早地中止該命令,並且所需的操作不會完成。ERASE和PROGRAM可以是耗時的操作; 發出RESET命令可以中止或稍後重新發出命令。

CE先拉低選中晶片,在io [8:0]上放置FFh,然後CLE拉高,將io [8:0]與命令鎖存器相連,然後將WE拉低,接著拉高,在上升沿完成命令的寫操作,延時TWB後查詢R / B腳的狀態,當為1時表示RESET完成。READ ID操作READ ID(90h)命令需要一個虛擬地址週期(00h),但不需要第二個命令週期。在發出命令和虛擬地址後,通過保持CLE和ALE為低電平並讀取ID的每個位元組的RE#訊號,可以讀出ID資料。

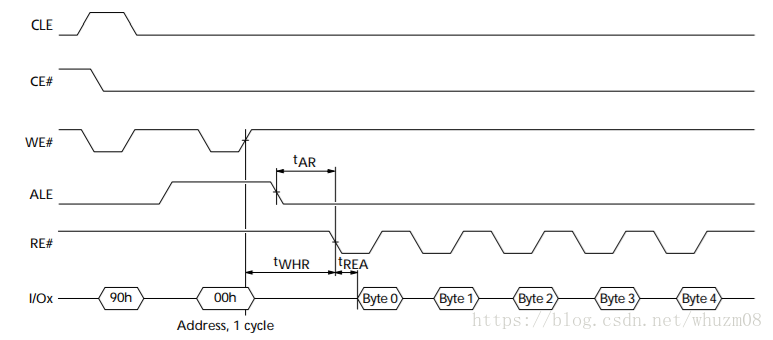

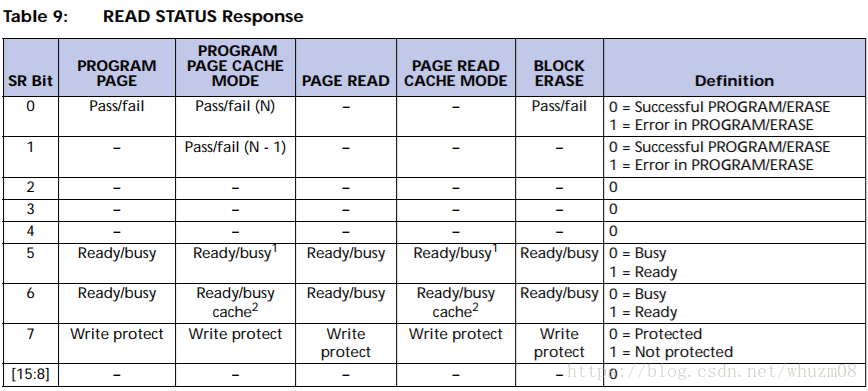

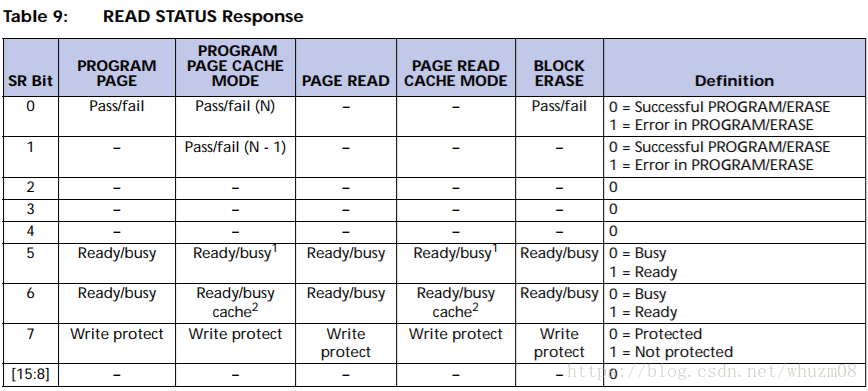

CE先拉低選中chip,在io [8:0]上放置90h,然後CLE拉高,將io [8:0]與命令鎖存器相連,然後將WE拉低,接著拉高,在上升沿完成命令的寫操作,然後拉低CLE,拉高ALE,將io [8:0]與地址鎖存器相連,在io [8:0]上放置00h,然後將WE拉低,然後拉高WE ,在上升沿完成addrees的寫操作,接著拉低ALE,適當的延時後拉低RE,(CLE和ALE都為低時,IO [8:0]與資料鎖存器相連,CLE和ALE都為高時為非法),chip將資料放置在io [8:0]上,nand controler從io [8:0]上讀取資料,讀完後RE拉高,然後拉低讀取下一個位元組。READ STATUS操作讀取狀態(70h)是NAND Flash器件忙時可以發出的第二個命令。該命令不需要地址或第二個命令週期。通過在READ STATUS命令之後發出RE#時鐘訊號,可以監控NAND快閃記憶體器件的狀態。如果使用READ STATUS命令監視器件的就緒狀態,則該命令只能發出一次,並且可以通過重新發出RE#時鐘來重新讀取狀態。或者,RE#訊號可以保持低電平,在繼續之前等待接收適當的狀態位。READ STATUS還會報告防寫訊號的狀態以及之前PROGRAM或ERASE操作的通過/失敗狀態。在PROGRAM或ERASE操作中必須達到合格狀態以確保資料完整性。

擦除操作BLOCK ERASE(60h)操作會擦除整個64頁的頁面,總共128KB。要發出BLOCK ERASE操作,使用WE#訊號在CLE置位時在ERASE(60h)命令中計時。接下來,在三個地址週期中的時鐘,保持每個位元組地址的ALE有效。(這三個地址週期是最重要的地址週期,包括塊地址和頁地址,如第9頁的表6所示。)頁地址部分(第三個地址週期的六個低位)被忽略,並且只使用三個最高有效位元組的塊地址部分。地址完全輸入後,發出D0h的第二個命令(命令週期2),當CLE置位時,它由WE#提供時鐘。這確認了ERASE操作,並且裝置忙了大約500μs。當裝置完成此操作時,它已準備好執行另一個命令。READ STATUS命令可以隨時發出,即使在ERASE操作過程中裝置處於繁忙狀態。微處理器或控制器可以通過READ STATUS命令監視裝置

提交70H命令查詢狀態後,RE一直為低,監控IO [5]引腳上的值,為0時表示擦除完成程式操作PROGRAM操作只能將位程式設計為0,並假定使用者以先前擦除的塊開始。如果使用者不想程式設計一個位(或一組位),則通過將該特定位/組設定為1,可以將位保持在擦除狀態。當接收到程式設計頁(80h)命令時,輸入暫存器被重置(內部)到全1。這支援只輸入要用0位程式設計的資料位元組。PROGRAM操作從80h命令開始(CLE置位 - 見圖8)。接下來,取消斷言CLE並斷言ALE輸入完整的五個地址週期。輸入命令和地址後,資料輸入到暫存器。

如果支援直接訪問模式,可以將nandflash直接對映到實體地址空間,通過XOR可以對映到不同的物理空間,這樣就可以直接從nandflash執行程式了(注意不能寫,因為寫之前必須要先擦除)NAND直接存取模式/ *禁止所有NAND CS的直接定址+ XOR * / BDEV_UNSET(BCHP_NAND_CS_NAND_SELECT,0xff); BDEV_UNSET(BCHP_NAND_CS_NAND_XOR,0xff);nandflash控制器全域性暫存器

oob:spare_area 0x40 = 64byte資料:flash_cache 128位元組= 128 * 4 = 512位元組

oob:spare_area 0x40 = 64byte資料:flash_cache 128位元組= 128 * 4 = 512位元組 Brcm nandflash控制器最多支援7個銀行 BCHP_NAND_ACC_CONTROL_CS0 Nand Flash訪問控制 RD_ECC_EN [31:31] RW為PAGE_READ操作啟用ECC校正。重置值:0x1WR_ECC_EN [30:30] RW為任何塊啟用對PROGRAM_PAGE或PROGRAM_SPARE_AREA操作的ECC校驗位生成。當該位置位時,ECC位元組將被忽略。選擇漢明碼時的ECC位元組位置是SPARE_AREA_WRITE_OFS_4和SPARE_AREA_WRITE_OFS_8暫存器的BYTE_OFS_6,BYTE_OFS_7和BYTE_OFS_8的3個位元組。選擇BCH碼時的ECC位元組位置是備用區域的最後位元組位置。例如,如果SPARE_AREA_SIZE = 16且ECC_LEVEL = 4(7個ECC位元組),則ECC位元組位置是BYTE_OFS_9到BYTE_OFS_15中的16個位元組中的最後7個。當此位設定為PROGRAM_PAGE操作時,ECC位元組將由H / W生成的ECC校驗位元組替代; 對於PROGRAM_SPARE_AREA操作,ECC位元組將被FFh替換。重置值:0x1CE_CARE [29:29] RW此欄位僅適用於CE護理裝置。當設定為1時,EBI_CS [n]將在NAND_RBb低電平期間保持置位狀態(器件忙)。在此期間,其他晶片選擇中的器件無法訪問。預設設定為0以獲得更好的效能。復位值:0x0保留 [28:28] RWX RD_ERASED_ECC_EN [27:27] RW確定擦除頁面中的PAGE_READ操作是否會生成不可糾正的ECC錯誤。(一個Erased Page被定義為全部512個數據位元組,所有3個ECC位元組都包含0xFF,剩餘的Spare Area位元組未被考慮)。無論該位的狀態如何,如果ECC被RD_ECC_EN = 0或RD_ECC_BLK0_EN = 0禁用,將不會生成錯誤。1 =從擦除頁讀取生成ECC錯誤。0 =從擦除頁讀取不會產生ECC錯誤。復位值:0x0PARTIAL_PAGE_EN [26:26] RW啟用部分頁面程式設計。建議清除此位以提高效能並防止部分頁面程式設計,這是許多nand快閃記憶體裝置所禁止的。 當該位置位且軟體啟動PROGRAM_PAGE操作時,硬體將資料直接寫入快閃記憶體單元。當該位清零並且軟體啟動PROGRAM_PAGE操作時,硬體將資料移入NAND Flash裝置快取並返回空閒狀態。只有當NAND_CMD_ADDRESS指向頁面的最後512位元組扇區時,硬體才會將資料程式設計到快閃記憶體單元中。小頁面裝置會忽略該位。復位值:0x0WR_PREEMPT_EN [25:25] RW使能其他EBI或PCI週期的寫突發操作的搶佔。當另一個請求者試圖使用匯流排時,這允許將來自Flash外部匯流排的長512位元組突發分成16次傳輸的多個突發。重置值:0x1PAGE_HIT_EN [24:24] RW啟用Flash頁面檢測檢測,作為頁面大小大於512B的頁面內512位元組讀取的優化。該位僅為大頁面裝置提供效能優化。如果設定,並且硬體發現讀取未命中,但是從已經讀入FlashCache的相同頁面,它將簡單地使用快閃記憶體的隨機讀取操作來節省時間。重置值:0x1PREFETCH_EN [23:23] RW硬體自動讀取當前頁面讀取命令地址的下一個512B或1KB資料,扇區大小取決於SECTOR_SIZE_1K位。啟用此位可提高讀取連續地址的效能。預取對軟體是透明的。CTLR_READY位始終指示當前地址讀取完成。注:建議將此位設定為長連續讀取,例如DMA傳輸。如果讀取地址不連續,則由於後臺預取,軟體可能會看到更長的繁忙時間和效能下降。注:僅當ECC_type為BCH時才支援預取。復位值:0x0CACHE_MODE_EN [22:22] RW啟用程式頁面或頁面讀取快取模式。如果置位,並且發出頁面讀取命令,硬體將啟動具有快取模式操作碼31h的頁面讀操作。如果置位,並且發出程式頁命令,則硬體以快取記憶體模式操作碼15h結束程式頁操作。快取模式通過連續頁面訪問跳過快閃記憶體裝置繁忙時間來提高效能。例如:第n,n + 1,n + 2,n + 3,n + 4 ... n + m的DMA傳輸注:硬體不檢測頁面地址的連貫性。軟體需要管理設定這一點。要恢復正常的頁面讀取和程式頁面命令,請取消設定此位。復位值:0x0保留 [21:21] RWX ECC_LEVEL [20:16] RW設定每512個數據位元組可以糾正的編碼型別和位數。定義T:=每扇區可修正的位數。當SECTOR_SIZE_1K = 0時,則T = ECC_LEVEL當SECTOR_SIZE_1K = 1時,則T = ECC_LEVEL * 2異常是SECTOR_SIZE_1K = 0,SPARE_AREA_SIZE = 16,ECC_LEVEL = 15,則T = 1(海明模式)保留 [15:8] RWX SECTOR_SIZE_1K [7:7] RW定義ECC碼字大小,也稱為扇區大小。注意:當使用1k位元組扇區大小時,ECC_LEVEL欄位指定T值的一半,漢明碼不可用。請參閱ECC_LEVEL說明中顯示的表。注意:當使用1k位元組扇區大小時,必須清除PARTIAL_PAGE_EN位,並且快閃記憶體頁面大小必須大於512。0 512位元組1個1k位元組當strap_nand_flash = 1時,該欄位將根據選定的ECC級別繫結在strap_nand_ecc_level [n:0]上進行初始化。復位值:0x0SPARE_AREA_SIZE [6:0] RW表示每512個數據位元組包含在快閃記憶體裝置中的備用區位元組數。有效設定是16到64(含)。對於16位寬的NAND快閃記憶體器件,此欄位必須包含偶數。對於大頁面裝置(頁面大小為2kB或更大),每頁的備用區域除以每頁的扇區數量。 例如,(2kB + 64B)頁面大小和512B扇區大小每頁有4個扇區,每頁全部64位元組備用區域將被分成4個相等的部分,每個16位元組; 並且這些部分中的每一個都將被不同的部門使用。選擇漢明碼時的ECC位元組位置是SPARE_AREA_WRITE_OFS_4和SPARE_AREA_WRITE_OFS_8暫存器的BYTE_OFS_6,BYTE_OFS_7和BYTE_OFS_8的3個位元組。選擇BCH碼時的ECC位元組位置是該特定扇區的備用區的最後一個位元組位置。 例如,如果SPARE_AREA_SIZE = 16且ECC_LEVEL = 4(7個ECC位元組),則ECC位元組位置是BYTE_OFS_9到BYTE_OFS_15中的16個位元組中的最後7個。當SECTOR_SIZE_1K = 1時,該欄位仍指定每512個備用位元組。當strap_nand_flash = 1時,該欄位將根據選定的ECC級別繫結在strap_nand_ecc_level [n:0]上進行初始化。重置值:0x10因為ECC校驗是由控制器自動完成的,那麼就必須讓控制器知道該bank上的nandflash使用的ECC LEVEL和SPARE_AREA_SIZE,這樣控制器就能知道ECC位元組在SPARE_AREA_READ_OFS_0中的位置.ECC位元組在nandflash中的位置理論上來說跟nandflash沒有多大關係,因為nandflash對ECC位元組是無知的,它由控制器來使用,nandflash會根據本身工藝推薦ECC LEVEL,理論上大於這個值都是可行的。BCHP_NAND_CONFIG_EXT_CS0 Nand Flash配置擴充套件 快閃記憶體裝置介面引數。根據NAND_CMD_EXT_ADDRESS暫存器中的CS_SEL值,硬體會根據剛剛復位後從外部Nand Flash器件讀取的DeviceID或ONFI引數值將預設值裝入此暫存器。保留[31:12] RWX BLOCK_SIZE [11:4] RW塊大小(以位元組為單位)。(注意:該欄位僅用於確定目標地址是否位於快閃記憶體的塊0中,以便在WR_PROTECT_BLK0位置位時知道是否應用防寫,或者當RD_ECC_BLK0_EN位為是時是否執行ECC糾正組。)值名稱0 BK_SIZE_8KB1 BK_SIZE_16KB2 BK_SIZE_32KB3 BK_SIZE_64KB4 BK_SIZE_128KB5 BK_SIZE_256KB6 BK_SIZE_512KB7 BK_SIZE_1024KB8 BK_SIZE_2048KB9 BK_SIZE_4096KB10 BK_SIZE_8192KBPAGE_SIZE [3:0] RW頁面大小(以位元組為單位)。值名稱說明0 PG_SIZE_512 512位元組。1 PG_SIZE_1KB 1k位元組。2 PG_SIZE_2KB 2k位元組。3 PG_SIZE_4KB 4k位元組。4 PG_SIZE_8KB 8k位元組。5 PG_SIZE_16KB 16k位元組。BCHP_NAND_CONFIG_CS0 Nand Flash配置快閃記憶體裝置介面引數。根據NAND_CMD_EXT_ADDRESS暫存器中的CS_SEL值,硬體會根據剛剛復位後從外部Nand Flash器件讀取的DeviceID或ONFI引數值將預設值裝入此暫存器。CONFIG_LOCK [31:31] RW當該位設定為1時,該暫存器和CONFIG_EXT暫存器變為只讀暫存器,防止進一步寫入該暫存器和CONFIG_EXT暫存器。一旦設定,該位只能通過復位清零。復位值:0x0保留[30:28] RWX DEVICE_SIZE [27:24] RW裝置大小(以位元組為單位)。值名稱0 DVC_SIZE_4MB1 DVC_SIZE_8MB2 DVC_SIZE_16MB3 DVC_SIZE_32MB4 DVC_SIZE_64MB5 DVC_SIZE_128MB6 DVC_SIZE_256MB7 DVC_SIZE_512MB8 DVC_SIZE_1GB9 DVC_SIZE_2GB10 DVC_SIZE_4GB11 DVC_SIZE_8GB12 DVC_SIZE_16GB13 DVC_SIZE_32GB14 DVC_SIZE_64GB15 DVC_SIZE_128GBDEVICE_WIDTH [23:23] RW裝置I / O資料匯流排寬度(以位為單位)。值名稱0 DVC_WIDTH_81 DVC_WIDTH_16保留[22:19] RWX FUL_ADR_BYTES [18:16] RW在裝置內傳送到Flash的完整地址的地址位元組數。當PAGE_SIZE> 512B時,FUL_ADR_BYTES = COL_ADR_BYTES + BLK_ADR_BYTES。當PAGE_SIZE = 512B時,FUL_ADR_BYTES = 1 + BLK_ADR_BYTES。該欄位通過繫結或AUTO_DEVICE_ID_CONFIG初始化。保留[15:15] RWX COL_ADR_BYTES [14:12] RW傳送到Flash以指定頁面內隨機資料訪問的列地址的地址位元組數。該欄位僅用於頁面大小大於512B的頁面,用於頁面內的隨機定址,以定址PROGRAM_PAGE和PAGE_READ命令的備用區域。2為512B <=頁面大小<= 32KB該欄位通過繫結或AUTO_DEVICE_ID_CONFIG初始化。保留[11:11] RWX BLK_ADR_BYTES [10:8] RW傳送到Flash以指定行和塊的地址位元組數。該欄位相當於NAND快閃記憶體資料表中的頁面地址+塊地址。該欄位僅用於BLOCK_ERASE和BLOCKS_UNLOCK命令。該欄位通過繫結或AUTO_DEVICE_ID_CONFIG初始化。保留[7:0] RWX BCHP_NAND_TIMING_1_CS0 Nand Flash時序引數1 快閃記憶體裝置介面時序引數。時序以內部108 MHz時鐘(9.26 ns)或內部216 MHz時鐘(4.63 ns)為單位指定,具體取決於TIMING_2.CLK_SELECT的值。任何時間欄位中的最小值是2(2個時鐘)。tWP [31:28] RW時鐘數WE低脈衝寬度。重置值:0x6tWH [27:24] RW片段數WE高脈衝寬度。(除了ALE較高時,在這種情況下,tALH控制WE高脈衝寬度而不是tWH。)重置值:0x5tRP [23:20] RW時鐘數RE低脈衝寬度。重置值:0x7tREH [19:16] RW時鐘數RE高脈衝寬度。重置值:0x4tCS [15:12] RW從CE低到第一個WE低的時鐘數。注意:當CLK_SELECT = CLK_108時,該暫存器欄位中的值將被硬體加倍,當CLK_SELECT = CLK_216時,該值將被硬體加倍。重置值:0x8tCLH [11:8] RW從WE高到CLE低的塊數。重置值:0x4tALH [7:4] RW從WE高到ALE低的時針數量。而且,當ALE高時,螢幕的數量WE高脈衝寬度。該位應該被設定為來自快閃記憶體製造商資料表的tWH和tALH之間的較大值。重置值:0x5tADL [3:0] RW從最後一個addr到第一次資料寫入的時鐘片數。注意:當CLK_SELECT = CLK_108時,該暫存器欄位中的值將被硬體加倍,當CLK_SELECT = CLK_216時,該值將被硬體加倍。復位值:0xBBCHP_NAND_TIMING_2_CS0 Nand Flash時序引數2 快閃記憶體裝置介面時序引數。時序以內部108 MHz時鐘(9.26 ns)或內部216 MHz時鐘(4.63 ns)為單位指定,具體取決於TIMING_2.CLK_SELECT的值。任何時間欄位中的最小值是2(2個時鐘)。CLK_SELECT [31:31] RW確定NAND_TIMING_1和NAND_TIMING_2中的引數用於nand快閃記憶體定時狀態機的時鐘。值名稱說明0 CLK_108內部108 MHz時鐘。1 CLK_216內部216 MHz時鐘。重置值:CLK_108保留[30:20] RWX tCCS [19:16] RW更改列命令設定時間。注:當CLK_SELECT = CLK_108時,硬體將該暫存器欄位中的值翻兩倍,並且當CLK_SELECT = CLK_216時,該值將由硬體八倍。重置值:0x9保留[15:13] RWX tWB [12:9] RW在硬體開始取樣R / B引腳之前,CE的高電平時鐘數。注意:當CLK_SELECT = CLK_108時,該暫存器欄位中的值將被硬體加倍,當CLK_SELECT = CLK_216時,該值將被硬體加倍。復位值:0xFtWHR [8:4] RW從WE高到RE低的時鐘片數。此引數僅用於狀態讀取和裝置ID讀取操作。注意:當CLK_SELECT = CLK_108時,該暫存器欄位中的值將被硬體加倍,當CLK_SELECT = CLK_216時,該值將被硬體加倍。重置值:0x9tREAD [3:0] RW RE低後取樣讀取資料之前等待的時鐘數。為獲得最佳效能,應通過將nns快閃記憶體器件的RE存取時間(tREA)加上17ns,然後將總和除以CLK_SELECT所選的時鐘週期,然後將其四捨五入至下一較大整數來計算此引數。例如,如果器件tREA = 20ns並且CLK_SELECT = 1(216MHz => 4.63ns):tREAD =(20ns + 17ns)/4.63ns=7.99(四捨五入)=> 8。tREAD的最大值是(tRP + tREH)。重置值:0x6操作時序在程式設計操作中,要被程式設計的資料在WE#的上升沿被同步到資料暫存器中。資料以類似的方式通過讀使能(RE#)訊號從資料暫存器輸出,該訊號負責輸出當前資料並遞增到下一個位置。WE#和RE#時鐘每次傳輸可以執行25ns。當RE#或晶片使能(CE#)未置為低電平時,輸出緩衝器為三態。CE#和RE#的這種組合激活了輸出緩衝器,使NAND Flash能夠與其他型別的儲存器(如NOR快閃記憶體,SRAM或DRAM)共享資料匯流排。這個功能有時被稱為“晶片使能不關心”。在RE#為低時,讀使能,輸出緩衝器直接放置在io上,可跟著變化。所有的NAND Flash操作都是通過發出一個命令週期來啟動的。這是通過將命令放在I / O [7:0]上,驅動CE#為低電平並且為高電平,然後發出WE#時鐘來完成的。命令,地址和資料在WE#的上升沿時鐘輸入NAND快閃記憶體器件,大多數命令需要多個地址週期,然後是第二個命令週期。除RESET和READ STATUS命令外,當裝置忙時不應發出新命令。支援的命令:

Brcm nandflash控制器最多支援7個銀行 BCHP_NAND_ACC_CONTROL_CS0 Nand Flash訪問控制 RD_ECC_EN [31:31] RW為PAGE_READ操作啟用ECC校正。重置值:0x1WR_ECC_EN [30:30] RW為任何塊啟用對PROGRAM_PAGE或PROGRAM_SPARE_AREA操作的ECC校驗位生成。當該位置位時,ECC位元組將被忽略。選擇漢明碼時的ECC位元組位置是SPARE_AREA_WRITE_OFS_4和SPARE_AREA_WRITE_OFS_8暫存器的BYTE_OFS_6,BYTE_OFS_7和BYTE_OFS_8的3個位元組。選擇BCH碼時的ECC位元組位置是備用區域的最後位元組位置。例如,如果SPARE_AREA_SIZE = 16且ECC_LEVEL = 4(7個ECC位元組),則ECC位元組位置是BYTE_OFS_9到BYTE_OFS_15中的16個位元組中的最後7個。當此位設定為PROGRAM_PAGE操作時,ECC位元組將由H / W生成的ECC校驗位元組替代; 對於PROGRAM_SPARE_AREA操作,ECC位元組將被FFh替換。重置值:0x1CE_CARE [29:29] RW此欄位僅適用於CE護理裝置。當設定為1時,EBI_CS [n]將在NAND_RBb低電平期間保持置位狀態(器件忙)。在此期間,其他晶片選擇中的器件無法訪問。預設設定為0以獲得更好的效能。復位值:0x0保留 [28:28] RWX RD_ERASED_ECC_EN [27:27] RW確定擦除頁面中的PAGE_READ操作是否會生成不可糾正的ECC錯誤。(一個Erased Page被定義為全部512個數據位元組,所有3個ECC位元組都包含0xFF,剩餘的Spare Area位元組未被考慮)。無論該位的狀態如何,如果ECC被RD_ECC_EN = 0或RD_ECC_BLK0_EN = 0禁用,將不會生成錯誤。1 =從擦除頁讀取生成ECC錯誤。0 =從擦除頁讀取不會產生ECC錯誤。復位值:0x0PARTIAL_PAGE_EN [26:26] RW啟用部分頁面程式設計。建議清除此位以提高效能並防止部分頁面程式設計,這是許多nand快閃記憶體裝置所禁止的。 當該位置位且軟體啟動PROGRAM_PAGE操作時,硬體將資料直接寫入快閃記憶體單元。當該位清零並且軟體啟動PROGRAM_PAGE操作時,硬體將資料移入NAND Flash裝置快取並返回空閒狀態。只有當NAND_CMD_ADDRESS指向頁面的最後512位元組扇區時,硬體才會將資料程式設計到快閃記憶體單元中。小頁面裝置會忽略該位。復位值:0x0WR_PREEMPT_EN [25:25] RW使能其他EBI或PCI週期的寫突發操作的搶佔。當另一個請求者試圖使用匯流排時,這允許將來自Flash外部匯流排的長512位元組突發分成16次傳輸的多個突發。重置值:0x1PAGE_HIT_EN [24:24] RW啟用Flash頁面檢測檢測,作為頁面大小大於512B的頁面內512位元組讀取的優化。該位僅為大頁面裝置提供效能優化。如果設定,並且硬體發現讀取未命中,但是從已經讀入FlashCache的相同頁面,它將簡單地使用快閃記憶體的隨機讀取操作來節省時間。重置值:0x1PREFETCH_EN [23:23] RW硬體自動讀取當前頁面讀取命令地址的下一個512B或1KB資料,扇區大小取決於SECTOR_SIZE_1K位。啟用此位可提高讀取連續地址的效能。預取對軟體是透明的。CTLR_READY位始終指示當前地址讀取完成。注:建議將此位設定為長連續讀取,例如DMA傳輸。如果讀取地址不連續,則由於後臺預取,軟體可能會看到更長的繁忙時間和效能下降。注:僅當ECC_type為BCH時才支援預取。復位值:0x0CACHE_MODE_EN [22:22] RW啟用程式頁面或頁面讀取快取模式。如果置位,並且發出頁面讀取命令,硬體將啟動具有快取模式操作碼31h的頁面讀操作。如果置位,並且發出程式頁命令,則硬體以快取記憶體模式操作碼15h結束程式頁操作。快取模式通過連續頁面訪問跳過快閃記憶體裝置繁忙時間來提高效能。例如:第n,n + 1,n + 2,n + 3,n + 4 ... n + m的DMA傳輸注:硬體不檢測頁面地址的連貫性。軟體需要管理設定這一點。要恢復正常的頁面讀取和程式頁面命令,請取消設定此位。復位值:0x0保留 [21:21] RWX ECC_LEVEL [20:16] RW設定每512個數據位元組可以糾正的編碼型別和位數。定義T:=每扇區可修正的位數。當SECTOR_SIZE_1K = 0時,則T = ECC_LEVEL當SECTOR_SIZE_1K = 1時,則T = ECC_LEVEL * 2異常是SECTOR_SIZE_1K = 0,SPARE_AREA_SIZE = 16,ECC_LEVEL = 15,則T = 1(海明模式)保留 [15:8] RWX SECTOR_SIZE_1K [7:7] RW定義ECC碼字大小,也稱為扇區大小。注意:當使用1k位元組扇區大小時,ECC_LEVEL欄位指定T值的一半,漢明碼不可用。請參閱ECC_LEVEL說明中顯示的表。注意:當使用1k位元組扇區大小時,必須清除PARTIAL_PAGE_EN位,並且快閃記憶體頁面大小必須大於512。0 512位元組1個1k位元組當strap_nand_flash = 1時,該欄位將根據選定的ECC級別繫結在strap_nand_ecc_level [n:0]上進行初始化。復位值:0x0SPARE_AREA_SIZE [6:0] RW表示每512個數據位元組包含在快閃記憶體裝置中的備用區位元組數。有效設定是16到64(含)。對於16位寬的NAND快閃記憶體器件,此欄位必須包含偶數。對於大頁面裝置(頁面大小為2kB或更大),每頁的備用區域除以每頁的扇區數量。 例如,(2kB + 64B)頁面大小和512B扇區大小每頁有4個扇區,每頁全部64位元組備用區域將被分成4個相等的部分,每個16位元組; 並且這些部分中的每一個都將被不同的部門使用。選擇漢明碼時的ECC位元組位置是SPARE_AREA_WRITE_OFS_4和SPARE_AREA_WRITE_OFS_8暫存器的BYTE_OFS_6,BYTE_OFS_7和BYTE_OFS_8的3個位元組。選擇BCH碼時的ECC位元組位置是該特定扇區的備用區的最後一個位元組位置。 例如,如果SPARE_AREA_SIZE = 16且ECC_LEVEL = 4(7個ECC位元組),則ECC位元組位置是BYTE_OFS_9到BYTE_OFS_15中的16個位元組中的最後7個。當SECTOR_SIZE_1K = 1時,該欄位仍指定每512個備用位元組。當strap_nand_flash = 1時,該欄位將根據選定的ECC級別繫結在strap_nand_ecc_level [n:0]上進行初始化。重置值:0x10因為ECC校驗是由控制器自動完成的,那麼就必須讓控制器知道該bank上的nandflash使用的ECC LEVEL和SPARE_AREA_SIZE,這樣控制器就能知道ECC位元組在SPARE_AREA_READ_OFS_0中的位置.ECC位元組在nandflash中的位置理論上來說跟nandflash沒有多大關係,因為nandflash對ECC位元組是無知的,它由控制器來使用,nandflash會根據本身工藝推薦ECC LEVEL,理論上大於這個值都是可行的。BCHP_NAND_CONFIG_EXT_CS0 Nand Flash配置擴充套件 快閃記憶體裝置介面引數。根據NAND_CMD_EXT_ADDRESS暫存器中的CS_SEL值,硬體會根據剛剛復位後從外部Nand Flash器件讀取的DeviceID或ONFI引數值將預設值裝入此暫存器。保留[31:12] RWX BLOCK_SIZE [11:4] RW塊大小(以位元組為單位)。(注意:該欄位僅用於確定目標地址是否位於快閃記憶體的塊0中,以便在WR_PROTECT_BLK0位置位時知道是否應用防寫,或者當RD_ECC_BLK0_EN位為是時是否執行ECC糾正組。)值名稱0 BK_SIZE_8KB1 BK_SIZE_16KB2 BK_SIZE_32KB3 BK_SIZE_64KB4 BK_SIZE_128KB5 BK_SIZE_256KB6 BK_SIZE_512KB7 BK_SIZE_1024KB8 BK_SIZE_2048KB9 BK_SIZE_4096KB10 BK_SIZE_8192KBPAGE_SIZE [3:0] RW頁面大小(以位元組為單位)。值名稱說明0 PG_SIZE_512 512位元組。1 PG_SIZE_1KB 1k位元組。2 PG_SIZE_2KB 2k位元組。3 PG_SIZE_4KB 4k位元組。4 PG_SIZE_8KB 8k位元組。5 PG_SIZE_16KB 16k位元組。BCHP_NAND_CONFIG_CS0 Nand Flash配置快閃記憶體裝置介面引數。根據NAND_CMD_EXT_ADDRESS暫存器中的CS_SEL值,硬體會根據剛剛復位後從外部Nand Flash器件讀取的DeviceID或ONFI引數值將預設值裝入此暫存器。CONFIG_LOCK [31:31] RW當該位設定為1時,該暫存器和CONFIG_EXT暫存器變為只讀暫存器,防止進一步寫入該暫存器和CONFIG_EXT暫存器。一旦設定,該位只能通過復位清零。復位值:0x0保留[30:28] RWX DEVICE_SIZE [27:24] RW裝置大小(以位元組為單位)。值名稱0 DVC_SIZE_4MB1 DVC_SIZE_8MB2 DVC_SIZE_16MB3 DVC_SIZE_32MB4 DVC_SIZE_64MB5 DVC_SIZE_128MB6 DVC_SIZE_256MB7 DVC_SIZE_512MB8 DVC_SIZE_1GB9 DVC_SIZE_2GB10 DVC_SIZE_4GB11 DVC_SIZE_8GB12 DVC_SIZE_16GB13 DVC_SIZE_32GB14 DVC_SIZE_64GB15 DVC_SIZE_128GBDEVICE_WIDTH [23:23] RW裝置I / O資料匯流排寬度(以位為單位)。值名稱0 DVC_WIDTH_81 DVC_WIDTH_16保留[22:19] RWX FUL_ADR_BYTES [18:16] RW在裝置內傳送到Flash的完整地址的地址位元組數。當PAGE_SIZE> 512B時,FUL_ADR_BYTES = COL_ADR_BYTES + BLK_ADR_BYTES。當PAGE_SIZE = 512B時,FUL_ADR_BYTES = 1 + BLK_ADR_BYTES。該欄位通過繫結或AUTO_DEVICE_ID_CONFIG初始化。保留[15:15] RWX COL_ADR_BYTES [14:12] RW傳送到Flash以指定頁面內隨機資料訪問的列地址的地址位元組數。該欄位僅用於頁面大小大於512B的頁面,用於頁面內的隨機定址,以定址PROGRAM_PAGE和PAGE_READ命令的備用區域。2為512B <=頁面大小<= 32KB該欄位通過繫結或AUTO_DEVICE_ID_CONFIG初始化。保留[11:11] RWX BLK_ADR_BYTES [10:8] RW傳送到Flash以指定行和塊的地址位元組數。該欄位相當於NAND快閃記憶體資料表中的頁面地址+塊地址。該欄位僅用於BLOCK_ERASE和BLOCKS_UNLOCK命令。該欄位通過繫結或AUTO_DEVICE_ID_CONFIG初始化。保留[7:0] RWX BCHP_NAND_TIMING_1_CS0 Nand Flash時序引數1 快閃記憶體裝置介面時序引數。時序以內部108 MHz時鐘(9.26 ns)或內部216 MHz時鐘(4.63 ns)為單位指定,具體取決於TIMING_2.CLK_SELECT的值。任何時間欄位中的最小值是2(2個時鐘)。tWP [31:28] RW時鐘數WE低脈衝寬度。重置值:0x6tWH [27:24] RW片段數WE高脈衝寬度。(除了ALE較高時,在這種情況下,tALH控制WE高脈衝寬度而不是tWH。)重置值:0x5tRP [23:20] RW時鐘數RE低脈衝寬度。重置值:0x7tREH [19:16] RW時鐘數RE高脈衝寬度。重置值:0x4tCS [15:12] RW從CE低到第一個WE低的時鐘數。注意:當CLK_SELECT = CLK_108時,該暫存器欄位中的值將被硬體加倍,當CLK_SELECT = CLK_216時,該值將被硬體加倍。重置值:0x8tCLH [11:8] RW從WE高到CLE低的塊數。重置值:0x4tALH [7:4] RW從WE高到ALE低的時針數量。而且,當ALE高時,螢幕的數量WE高脈衝寬度。該位應該被設定為來自快閃記憶體製造商資料表的tWH和tALH之間的較大值。重置值:0x5tADL [3:0] RW從最後一個addr到第一次資料寫入的時鐘片數。注意:當CLK_SELECT = CLK_108時,該暫存器欄位中的值將被硬體加倍,當CLK_SELECT = CLK_216時,該值將被硬體加倍。復位值:0xBBCHP_NAND_TIMING_2_CS0 Nand Flash時序引數2 快閃記憶體裝置介面時序引數。時序以內部108 MHz時鐘(9.26 ns)或內部216 MHz時鐘(4.63 ns)為單位指定,具體取決於TIMING_2.CLK_SELECT的值。任何時間欄位中的最小值是2(2個時鐘)。CLK_SELECT [31:31] RW確定NAND_TIMING_1和NAND_TIMING_2中的引數用於nand快閃記憶體定時狀態機的時鐘。值名稱說明0 CLK_108內部108 MHz時鐘。1 CLK_216內部216 MHz時鐘。重置值:CLK_108保留[30:20] RWX tCCS [19:16] RW更改列命令設定時間。注:當CLK_SELECT = CLK_108時,硬體將該暫存器欄位中的值翻兩倍,並且當CLK_SELECT = CLK_216時,該值將由硬體八倍。重置值:0x9保留[15:13] RWX tWB [12:9] RW在硬體開始取樣R / B引腳之前,CE的高電平時鐘數。注意:當CLK_SELECT = CLK_108時,該暫存器欄位中的值將被硬體加倍,當CLK_SELECT = CLK_216時,該值將被硬體加倍。復位值:0xFtWHR [8:4] RW從WE高到RE低的時鐘片數。此引數僅用於狀態讀取和裝置ID讀取操作。注意:當CLK_SELECT = CLK_108時,該暫存器欄位中的值將被硬體加倍,當CLK_SELECT = CLK_216時,該值將被硬體加倍。重置值:0x9tREAD [3:0] RW RE低後取樣讀取資料之前等待的時鐘數。為獲得最佳效能,應通過將nns快閃記憶體器件的RE存取時間(tREA)加上17ns,然後將總和除以CLK_SELECT所選的時鐘週期,然後將其四捨五入至下一較大整數來計算此引數。例如,如果器件tREA = 20ns並且CLK_SELECT = 1(216MHz => 4.63ns):tREAD =(20ns + 17ns)/4.63ns=7.99(四捨五入)=> 8。tREAD的最大值是(tRP + tREH)。重置值:0x6操作時序在程式設計操作中,要被程式設計的資料在WE#的上升沿被同步到資料暫存器中。資料以類似的方式通過讀使能(RE#)訊號從資料暫存器輸出,該訊號負責輸出當前資料並遞增到下一個位置。WE#和RE#時鐘每次傳輸可以執行25ns。當RE#或晶片使能(CE#)未置為低電平時,輸出緩衝器為三態。CE#和RE#的這種組合激活了輸出緩衝器,使NAND Flash能夠與其他型別的儲存器(如NOR快閃記憶體,SRAM或DRAM)共享資料匯流排。這個功能有時被稱為“晶片使能不關心”。在RE#為低時,讀使能,輸出緩衝器直接放置在io上,可跟著變化。所有的NAND Flash操作都是通過發出一個命令週期來啟動的。這是通過將命令放在I / O [7:0]上,驅動CE#為低電平並且為高電平,然後發出WE#時鐘來完成的。命令,地址和資料在WE#的上升沿時鐘輸入NAND快閃記憶體器件,大多數命令需要多個地址週期,然後是第二個命令週期。除RESET和READ STATUS命令外,當裝置忙時不應發出新命令。支援的命令:

2Gb NAND Flash器件的定址方案如表6所示。第一個和第二個地址週期(或位元組)指定了列地址,它指定了頁面內的起始位元組。最後一列的位置是2112,因此最後一個位置的地址是第二個位元組中的08h,第一個位元組中是3Fh。PA [5:0]指定塊內的頁面地址,BA [16:6]指定塊地址。儘管大多數PROGRAM和READ操作需要完整的5位元組地址,但對於在頁面內隨機訪問資料的操作,只需要第一個和第二個位元組(或迴圈)。BLOCK ERASE操作只需要三個最重要的位元組(第三,第四和第五)來選擇該塊。

當CA11 = 1時表示訪問oob資料,一般列地址都為0,表示從頁面內偏移0開始訪問整個頁面。復位操作RESET是NAND Flash器件繁忙時可以發出的兩個命令之一。如果裝置正忙於處理先前的命令,則發出RESET命令會中止前一個操作。如果之前的操作是ERASE或PROGRAM命令,則發出RESET命令會過早地中止該命令,並且所需的操作不會完成。ERASE和PROGRAM可以是耗時的操作; 發出RESET命令可以中止或稍後重新發出命令。

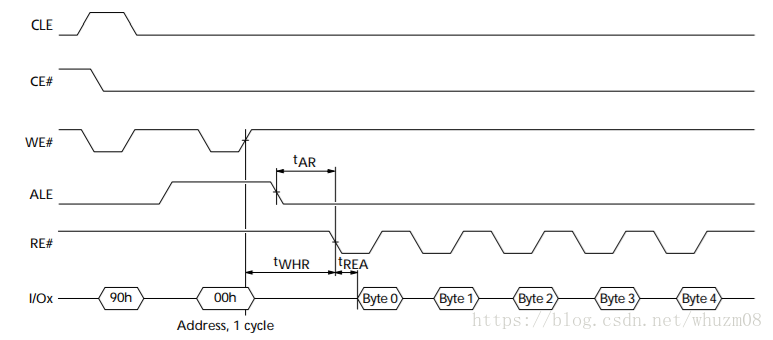

CE先拉低選中晶片,在io [8:0]上放置FFh,然後CLE拉高,將io [8:0]與命令鎖存器相連,然後將WE拉低,接著拉高,在上升沿完成命令的寫操作,延時TWB後查詢R / B腳的狀態,當為1時表示RESET完成。READ ID操作READ ID(90h)命令需要一個虛擬地址週期(00h),但不需要第二個命令週期。在發出命令和虛擬地址後,通過保持CLE和ALE為低電平並讀取ID的每個位元組的RE#訊號,可以讀出ID資料。

CE先拉低選中chip,在io [8:0]上放置90h,然後CLE拉高,將io [8:0]與命令鎖存器相連,然後將WE拉低,接著拉高,在上升沿完成命令的寫操作,然後拉低CLE,拉高ALE,將io [8:0]與地址鎖存器相連,在io [8:0]上放置00h,然後將WE拉低,然後拉高WE ,在上升沿完成addrees的寫操作,接著拉低ALE,適當的延時後拉低RE,(CLE和ALE都為低時,IO [8:0]與資料鎖存器相連,CLE和ALE都為高時為非法),chip將資料放置在io [8:0]上,nand controler從io [8:0]上讀取資料,讀完後RE拉高,然後拉低讀取下一個位元組。READ STATUS操作讀取狀態(70h)是NAND Flash器件忙時可以發出的第二個命令。該命令不需要地址或第二個命令週期。通過在READ STATUS命令之後發出RE#時鐘訊號,可以監控NAND快閃記憶體器件的狀態。如果使用READ STATUS命令監視器件的就緒狀態,則該命令只能發出一次,並且可以通過重新發出RE#時鐘來重新讀取狀態。或者,RE#訊號可以保持低電平,在繼續之前等待接收適當的狀態位。READ STATUS還會報告防寫訊號的狀態以及之前PROGRAM或ERASE操作的通過/失敗狀態。在PROGRAM或ERASE操作中必須達到合格狀態以確保資料完整性。

擦除操作BLOCK ERASE(60h)操作會擦除整個64頁的頁面,總共128KB。要發出BLOCK ERASE操作,使用WE#訊號在CLE置位時在ERASE(60h)命令中計時。接下來,在三個地址週期中的時鐘,保持每個位元組地址的ALE有效。(這三個地址週期是最重要的地址週期,包括塊地址和頁地址,如第9頁的表6所示。)頁地址部分(第三個地址週期的六個低位)被忽略,並且只使用三個最高有效位元組的塊地址部分。地址完全輸入後,發出D0h的第二個命令(命令週期2),當CLE置位時,它由WE#提供時鐘。這確認了ERASE操作,並且裝置忙了大約500μs。當裝置完成此操作時,它已準備好執行另一個命令。READ STATUS命令可以隨時發出,即使在ERASE操作過程中裝置處於繁忙狀態。微處理器或控制器可以通過READ STATUS命令監視裝置

提交70H命令查詢狀態後,RE一直為低,監控IO [5]引腳上的值,為0時表示擦除完成程式操作PROGRAM操作只能將位程式設計為0,並假定使用者以先前擦除的塊開始。如果使用者不想程式設計一個位(或一組位),則通過將該特定位/組設定為1,可以將位保持在擦除狀態。當接收到程式設計頁(80h)命令時,輸入暫存器被重置(內部)到全1。這支援只輸入要用0位程式設計的資料位元組。PROGRAM操作從80h命令開始(CLE置位 - 見圖8)。接下來,取消斷言CLE並斷言ALE輸入完整的五個地址週期。輸入命令和地址後,資料輸入到暫存器。