【 FPGA 】組合邏輯中的競爭與險象問題(四)

上篇博文:組合邏輯中的競爭與險象問題(三)講解了險象的定義,即競爭引起的非預期輸出,同時給出了分析,對什麼樣的競爭會引起險象。

這篇博文繼續講解險象問題,重要突出險象的分類。

上篇博文最後提出了化簡後具有多個半開關的電路,可能會導致險象的阻塞,縮小,傳遞或方法作用。這篇博文接著這個問題討論:

(1)一般說來,如果若干個與半開關被一個或半開關級聯,或者若干個或半開關被一個與半開關級聯,主要會對險象起放大作用;

(2)如果若干個與半開關被一個與半開關級聯,或者若干個或半開關被一個或半開關級聯,主要會對險象起到截止、縮小作用;

(3)如果若干個與半開關、或半開關被無論是一個與半開關還是或半開關級聯,主要會對險象起到傳遞、縮小的作用。

下面研究險象的一些具體表現形式,概括起來,險象可以分為靜態險象和動態險象,下面分別介紹:

靜態險象

靜態險象,指的是由於競爭,導致的原本輸出不應該發生變化的組合邏輯,出現了輸出變化現象。從靜態險象的定義,我們可以推出,如果一個組合邏輯,在某一種輸入條件下存在靜態險象,那麼其邏輯表示式在該條件下一定可以簡化為F = 1或F = 0。

按其所應保持的電平,又可以將這類險象細分為0險象和1險象。

(1)0 險象

0險象指的是組合邏輯的初識輸出為0,當其輸入改變時,若新輸入對應的輸出仍應該是0,卻在輸出端出現了短暫的不為0的情況。(這種情況很常見,上篇博文中,一個兩輸入的與門半開關就是如此,當輸入從1變為0時,就會出現短暫的1邏輯,這種險象就是0 險象。)

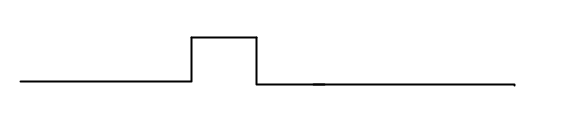

下圖為典型的0險象的波形:

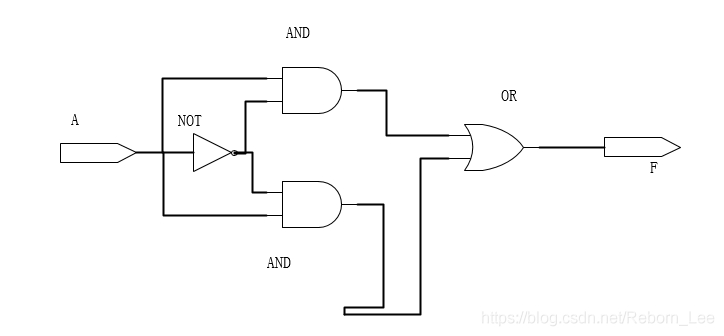

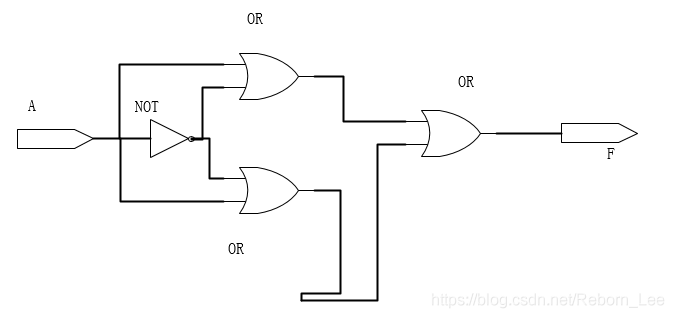

當出現半開關級聯的情況,0險象中1的脈衝個數可能不只一個,例如,若簡化後的電路如下圖,則疊加後的0險象可能會出現兩個1脈衝,當然也可能是一個更寬的1脈衝。

上圖是兩個與門半開關和一個或門半開關級聯的情況,如開頭所說,這種級聯會導致險象的放大。

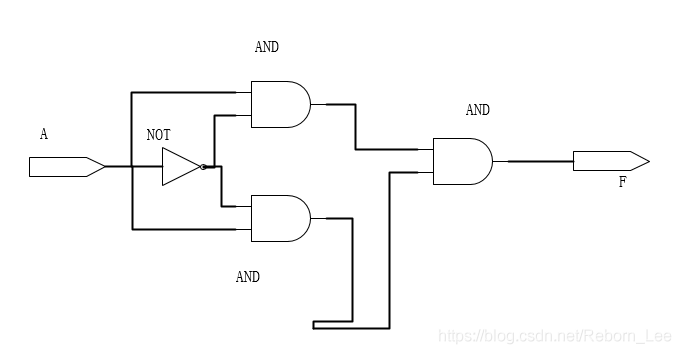

下圖是兩個與門半開關和一個與門半開關級聯的情況,如開頭所說,這種級聯會縮小險象,如下:

上圖的這種級聯會消減1脈衝的寬度,甚至會完全阻止1脈衝。

(2)1 險象

1險象是指組合邏輯的輸出初始值為1,當其輸入改變時,若新輸入對應的輸出仍應該是1,卻出現了短暫不為1的情況。

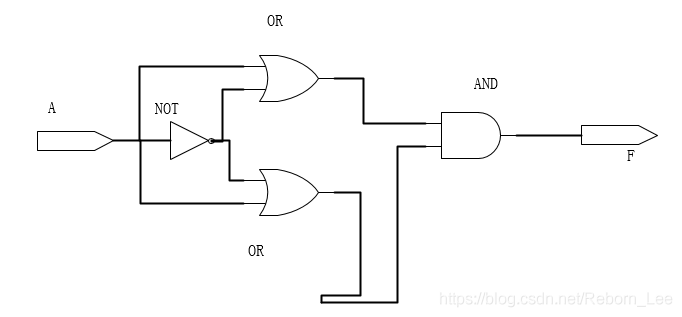

這種情況和0險象的情況完全對偶,我們可以給出如下兩個級聯的例子:

上圖這種,兩個或半開關和一個與門半開關的級聯,會使0脈衝變大,或者出現兩個0脈衝。

而下圖這種級聯會使0脈衝縮小,或完全阻塞。

動態險象

動態險象,指的是由於競爭,導致原本輸出只應該發生一次變化的組合邏輯,出現了輸出多次變化的現象。

如果一個組合邏輯在某一種輸入條件下存在動態險象,那麼其邏輯表示式在該條件下一定可以化簡為 F = A 或 F = 。經過前面的分析,我們得知只有當半開關的M個輸入中有0也有1時,競爭才可能導致險象。因此,對於單個半開關來說,它的表示式只能化簡為F = 1(或型別半開關)或F = 0(與型別半開關),因此動態險象發生的前提是電路中一定存在半開關的級聯,且前級的半開關先導致靜態險象。

按其初始和穩定時所對應的邏輯電平,又可將這類險象細分為01險象和10險象。

(1)01 險象

01 險象,是指組合邏輯初始輸出為0,當其輸入改變時,對應新的輸出應該為1,本來輸出只應該出現一次從0到1的翻轉,但實際中卻出現了多次的0,1翻轉情況。

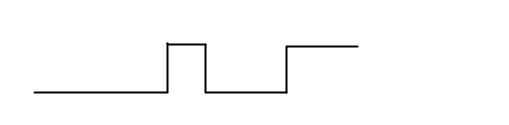

典型的 01 險象如下圖:

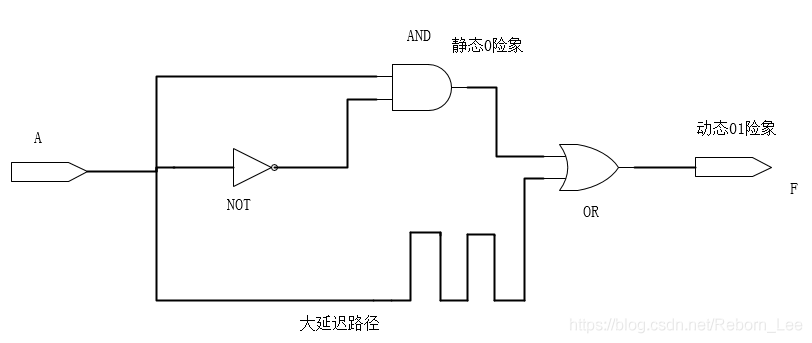

例如,若簡化後的電路圖如下圖,就會出現上述典型的01險象:

上述電路中,當輸入端A從0變化到1時,由於下半部分路徑延遲比較大,導致或型別半開關先傳遞了上半部分的靜態0險象後輸出恆為1,因此形成了動態01險象。如果簡化電路再複雜一些,則01險象的翻轉次數也可能會更加多一些,例如若本例或型別半開關上半部分輸入的是一個疊加後成雙1脈衝的0險象,那麼輸出就可能翻轉3次。

(2)10 險象

上面的討論分析了01險象,有了01險象,那麼10險象就很容易了。

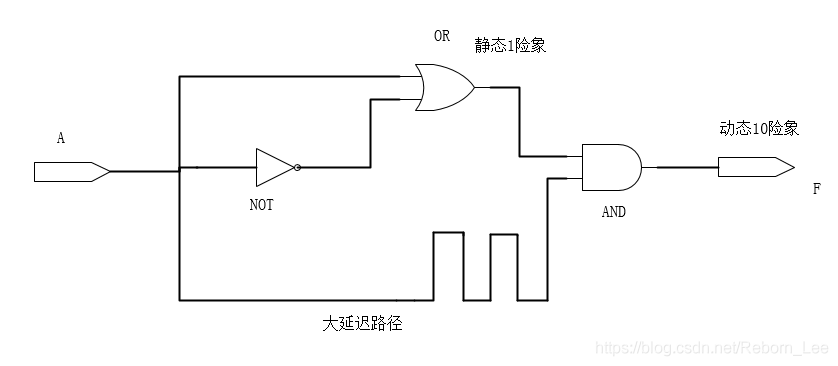

如下電路:

當輸入端從1變化到0時候,由於下半部分延遲較大,所以與型別半開關先傳遞了上半部分的靜態1險象後,再傳遞下半部分,輸出恆為0,形成了10險象。

這篇博文暫時到這裡,下篇博文講解險象對數位電路的影響以及如何對待險象。