二、處理器

阿新 • • 發佈:2019-01-26

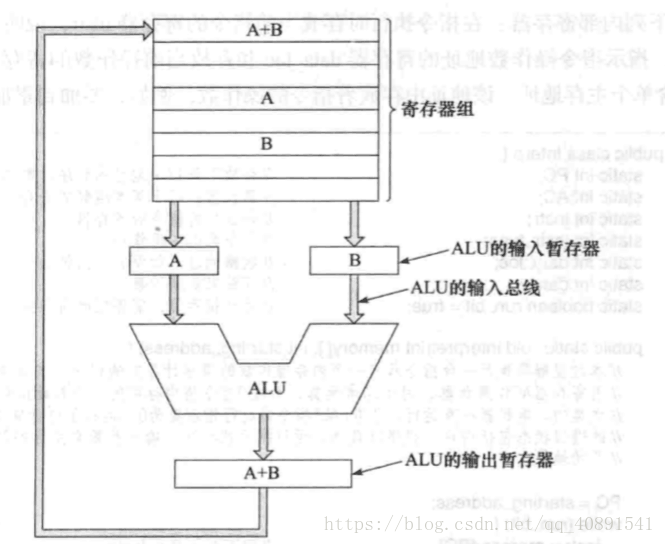

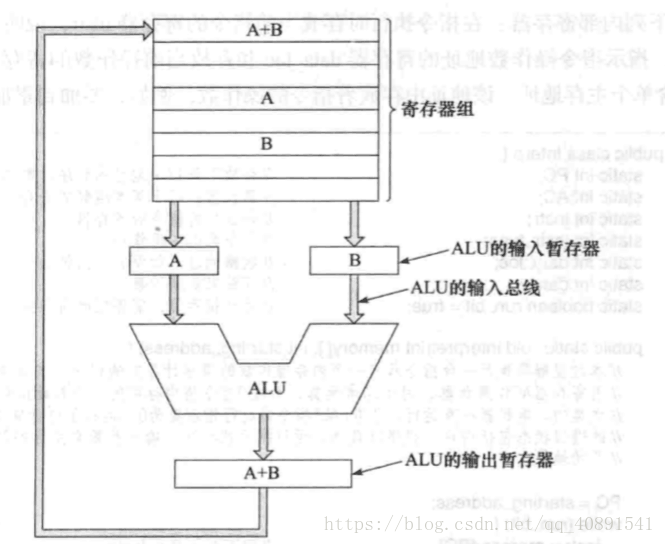

1.概念①中央處理部件(Central Processing Unit,CPU)可以說是計算機的“大腦”,其功能是通過從主儲存器中逐條進行 取指令、分析指令和執行指令的過程來執行計算機程式。②程式計數器(Program Counter,PC)它用於指向下一條將要被取出用於執行的指令。③指令暫存器(Instruction Register,IR)其中存放著當前正執行的執行。④算術邏輯部件(Arithmetic Logic Unit,ALU)⑤資料通路:一般包括 暫存器、ALU和連線它們的內部匯流排。、2.CPU組 上圖是一個CPU的資料通路圖①如上圖,ALU有兩個輸入暫存器,一個輸出暫存器。暫存器的功能是在ALU進行計算時維持ALU的輸入資料。

上圖是一個CPU的資料通路圖①如上圖,ALU有兩個輸入暫存器,一個輸出暫存器。暫存器的功能是在ALU進行計算時維持ALU的輸入資料。

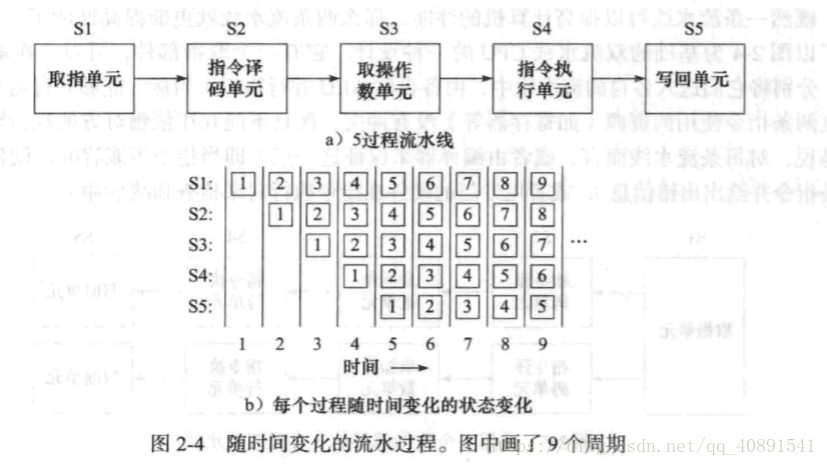

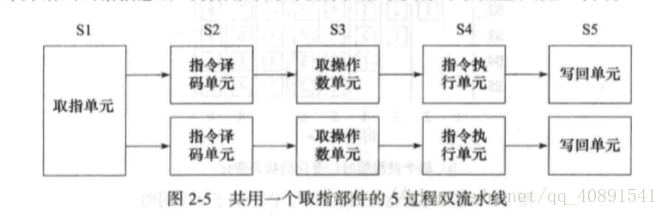

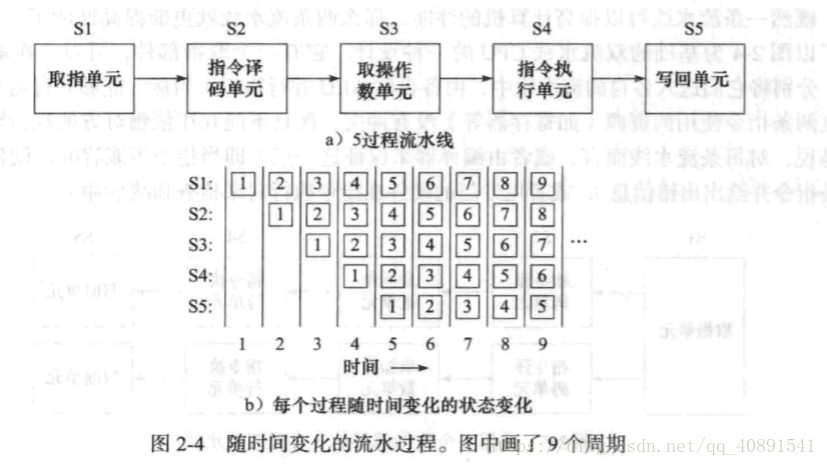

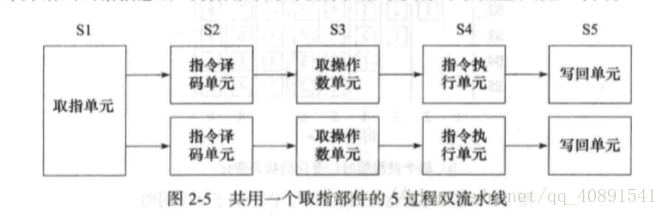

圖中的例子裡,將指令執行劃為了5個部分(現實中通常為12個或者更多),每個部分由精心設計的硬體分別執行,讓他們並行執行。  ①指令級並行固然可以提高效率,可是傳輸的速度是有物理極限的,並且,晶片越多,其產生的熱量也會越多,散熱就很成問題。②對於那些高度規則的資料結構進行相同的資料運算,加速它們相對容易。我們主要有兩種方式來可快速並高效的執行這類高度規則的程式:SIMD處理器和向量處理器。前者被看成是平行計算機,後者被當成單處理器的擴充套件。③單指令流多資料流處理器(Single Instruction-stream Multiple Data-stream,SIMD):這種處理器由許多在不同資料集合上執行同樣的指令序列的王權相同的處理器組成。 現代的GPU(圖形處理器)嚴重依賴SIMD處理器使用較少的電晶體來提供巨大的處理能力。④多處理器系統:除了增加處理器的效能和資料的規整程度外,還可以增加多處理器

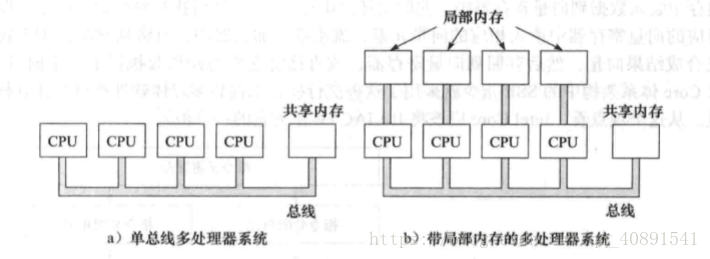

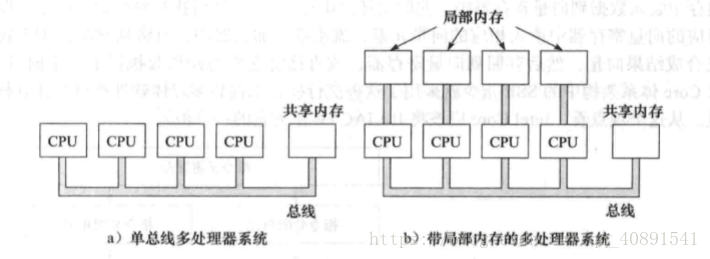

①指令級並行固然可以提高效率,可是傳輸的速度是有物理極限的,並且,晶片越多,其產生的熱量也會越多,散熱就很成問題。②對於那些高度規則的資料結構進行相同的資料運算,加速它們相對容易。我們主要有兩種方式來可快速並高效的執行這類高度規則的程式:SIMD處理器和向量處理器。前者被看成是平行計算機,後者被當成單處理器的擴充套件。③單指令流多資料流處理器(Single Instruction-stream Multiple Data-stream,SIMD):這種處理器由許多在不同資料集合上執行同樣的指令序列的王權相同的處理器組成。 現代的GPU(圖形處理器)嚴重依賴SIMD處理器使用較少的電晶體來提供巨大的處理能力。④多處理器系統:除了增加處理器的效能和資料的規整程度外,還可以增加多處理器 ⑤ 多計算機系統:才用多個計算機互聯組成多計算機系統。

⑤ 多計算機系統:才用多個計算機互聯組成多計算機系統。

上圖是一個CPU的資料通路圖①如上圖,ALU有兩個輸入暫存器,一個輸出暫存器。暫存器的功能是在ALU進行計算時維持ALU的輸入資料。

上圖是一個CPU的資料通路圖①如上圖,ALU有兩個輸入暫存器,一個輸出暫存器。暫存器的功能是在ALU進行計算時維持ALU的輸入資料。

圖中的例子裡,將指令執行劃為了5個部分(現實中通常為12個或者更多),每個部分由精心設計的硬體分別執行,讓他們並行執行。

①指令級並行固然可以提高效率,可是傳輸的速度是有物理極限的,並且,晶片越多,其產生的熱量也會越多,散熱就很成問題。②對於那些高度規則的資料結構進行相同的資料運算,加速它們相對容易。我們主要有兩種方式來可快速並高效的執行這類高度規則的程式:SIMD處理器和向量處理器。前者被看成是平行計算機,後者被當成單處理器的擴充套件。③單指令流多資料流處理器(Single Instruction-stream Multiple Data-stream,SIMD):這種處理器由許多在不同資料集合上執行同樣的指令序列的王權相同的處理器組成。 現代的GPU(圖形處理器)嚴重依賴SIMD處理器使用較少的電晶體來提供巨大的處理能力。④多處理器系統:除了增加處理器的效能和資料的規整程度外,還可以增加多處理器

①指令級並行固然可以提高效率,可是傳輸的速度是有物理極限的,並且,晶片越多,其產生的熱量也會越多,散熱就很成問題。②對於那些高度規則的資料結構進行相同的資料運算,加速它們相對容易。我們主要有兩種方式來可快速並高效的執行這類高度規則的程式:SIMD處理器和向量處理器。前者被看成是平行計算機,後者被當成單處理器的擴充套件。③單指令流多資料流處理器(Single Instruction-stream Multiple Data-stream,SIMD):這種處理器由許多在不同資料集合上執行同樣的指令序列的王權相同的處理器組成。 現代的GPU(圖形處理器)嚴重依賴SIMD處理器使用較少的電晶體來提供巨大的處理能力。④多處理器系統:除了增加處理器的效能和資料的規整程度外,還可以增加多處理器 ⑤ 多計算機系統:才用多個計算機互聯組成多計算機系統。

⑤ 多計算機系統:才用多個計算機互聯組成多計算機系統。