Verilog基礎知識5(ASIC設計中各個階段的關鍵問題彙總)

需求說明:Verilog設計

內容 :ASIC設計關鍵問題

來自 :時間的詩

ASIC的複雜性不斷提高,同時工藝在不斷地改進,如何在較短的時間內開發一個穩定的可重用的ASIC晶片的設計,並且一次性流片成功,這需要一個成熟的ASIC的設計方法和開發流程。本文結合NCverilog,DesignCompile,Astro等ASIC設計所用到的EDA軟體,從工藝獨立性、系統的穩定性、複雜性的角度對比各種ASIC的設計方法,介紹了在編碼設計、綜合設計、靜態時序分析和時序模擬等階段經常忽視的問題以及避免的辦法,從而使得整個設計具有可控性。

1.基本的ASIC設計流程

ASIC設計流程可以粗分為前端設計和後端設計,如果需要更細的劃分,可以分成如下幾個步驟:

1.包括系統結構分析設計、RTL編碼以及功能驗證;

2.邏輯綜合、PreLayoutSTA以及形式驗證(RTL程式碼與邏輯綜合生成的Netlist之間);

3.Floorplan、Placement、ClockTree插入以及全域性佈線(GlobalRouting)

4.形式驗證(邏輯綜合的Netlist與帶有CT資訊的Netlist之間)、STA;

5.DetailedRouting,DRC;

6.PostlayoutSTA,帶有反標延遲資訊的門級模擬;

7.Tape-Out

當然,這還是一個比較粗的流程,其中每個步驟還可以分得更細,通常所說的前端設計主要包括上述流程中的1,2,4,6這幾個部分。同時,這個流程是一個迭代的過程。對於一些通常的問題以及其中的一些方法,已經有大量的文獻中提到,本文將不再贅述,因此本文著力於討論在設計各個階段中一些容易被忽視的或者可能帶來潛在危險的地方。

2.結構分析設計、RTL編碼

這一階段在整個ASIC設計中佔非常重要的地位,結構分析設計階段主要是從產品的功能定義出發,對產品採用的工藝、功耗、面積、效能以及代價進行初步的評估,從而制定相應的設計規劃,對於規模很大的ASIC設計,在這一階段估算晶片的功耗面積非常困難。在這裡引入一個ASIC設計中很重要的概念:劃分(Partitioning),在不同的設計階段這個概念都將提到。首先,必須在晶片的Top-1級進行功能劃分,Top-1級通常可以分為4個大的功能模組,IOPads、邊界掃描邏輯、核心功能邏輯,以及PLL時鐘模組,然後再對核心功能邏輯依據功能進一步細化。核心功能部分將是RTL編碼設計的重點部分,下面就這一部分展開說明。

2.1良好的編碼風格

編碼風格對晶片的正確性、可讀性、可維護性以及綜合後晶片的效能、面積都有很大的影響。自然,對於編碼中遇到的所有問題一一闡述不是一篇論文所能做到的,下面只對一些經常遇到的可能產生錯誤的地方進行重點說明。無論從可重用設計的角度還是程式碼模擬行為與實際晶片的行為一致性的角度來說,採用工藝獨立的設計是必要的,一些工程師在編碼時可能用到一些延遲單元或者延遲線,來生成一個脈衝來操作,由於延遲單元對溫度、電壓以及製造工藝敏感,這些因素的改變也會改變生成的脈衝的寬度,因此,可能在模擬的時候沒有問題,或者在某些操作條件下沒有問題,而實際晶片工作時或者工作條件改變時晶片就沒有按照設計目標工作了。

在RTL級編碼時應該儘量避免採用例化標準單元門的方式編碼,這不僅降低程式碼的可讀性,當採用新的單元庫或者新的工藝時,這些程式碼就需要反覆的修改,綜合工具也不會對這些程式碼進行邏輯優化。

其他問題如:由於沒有對所有的條件分支賦值引起潛在的Latch問題、always塊中的敏感列表問題,以及阻塞賦值與非阻塞賦值的選擇問題很多文獻中都提到,就不再贅述。下面提到一個容易被忽視的問題,在定義時序塊時,有些訊號是需要復位的,有些不需要復位,如果編碼時把它們寫在一個always塊中,綜合出來的電路就不是我們設想的。對於那些不需要復位的訊號,綜合後可能把復位訊號連到對應的觸發器使能端,這樣導致RTL程式碼和Netlist的行為不一致,而這類問題在形式驗證時也沒法發現,需要通過大量的門級模擬才可能發現。

ASIC設計應該儘量避免採用Latch作為時序單元,Latch設計潛在的問題,如:如果使能輸入端有Glitch,就會導致鎖存噪聲資料。或者你能夠保證資料穩定時間可以包住使能訊號,可你很難保證在使能關閉的瞬間D輸入端沒有Glitch,尤其在接收匯流排資料的時候。同時,Latch設計還帶來STA和DFT的困難,而採用觸發器的設計,通過Setup/Hold時間的檢查報出這些問題。因此,儘管Latch設計有面積、低功耗等方面的優勢,由於這些潛在的風險使得設計變得不可控,因此不推薦使用。

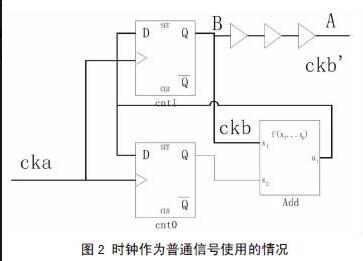

儘量避免把時鐘當作訊號使用,在RTL驗證時不會出現什麼問題,但是,如果在後端設計的時候忽略了對這些點的時鐘skew控制,就會產生意想不到的結果。例如:例1:

module gen_clk(cka,rst_n,ckb);

input cka,rst_n;

output ckb;

reg[1:0] ck_cnt;

[email protected](posedgecka)begin

if(!rst_n) ck_cnt

else ck_cnt

end

assign ckb=ck_cnt;

endmodule這個程式碼在RTL級模擬時是不會有任何問題的,其中潛在的問題留待後面討論。

2.2同步設計和跨時鐘域資料傳輸

儘管非同步系統有很多優勢,如低功耗,也沒有同步系統中讓工程師頭疼的時鐘分佈以及skew問題,但是其複雜的各種握手協議,以及非同步電路在測試上的困難,使得同步系統還是數位電路設計的首選。同步設計的一個特點就是所有的時序單元都是對統一的時鐘邊沿敏感。要使整個晶片只採用一個時鐘並不現實,因此,非同步時鐘域之間的資料傳輸以及其中的一些問題將是本節討論的重點。通常,為了能夠更好的綜合和STA,需要對設計進行劃分,一般的原則是將非同步時鐘域之間有資料交換的部分獨立出來單獨處理,其他的模組都在單一的同步時鐘域中工作。對於這些模組如何在綜合過程中特殊處理在下面的章節中討論,本節主要討論在程式碼設計中需要考慮的問題。

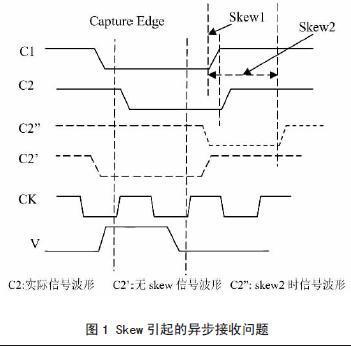

非同步時鐘之間的亞穩態(Metastability)問題,亞穩態主要是由於被取樣資料的變化十分靠近取樣時鐘的邊沿引起的,這樣接收(取樣)觸發器的輸出就是亞穩態,並在傳輸過程中發散而引發邏輯錯誤,也就是通常所說的同步失敗。在同步時鐘域中的這種問題是Hold問題,可以通過EDA工具或插入buffer消除,因為EDA工具可以檢測到這種問題。那麼在非同步接收設計中通過兩級Flipflop來消除這種可能出現的亞穩態。現在也有工具檢測程式碼中可能出現的亞穩態問題。多位接收控制訊號之間的skew引起的問題如圖1,如果其中一位如C2延遲大於C1,Ck取樣的資料就變成了C2=1,C1=0,如果按照無skew傳輸的波形是C2’的樣子,應該是00才對。而skew是不可避免的,可能是由於C2C1訊號的Launch時鐘本身的skew引起,也可能是傳輸延遲引起。對於簡單的情況,我們可以通過簡化邏輯,儘量讓控制訊號是1位寬。而這樣的問題同樣出現在多位寬的資料接收情況。這時通常推薦使用非同步FIFO接收,或者通過握手協議接收。有的系統設計資料交換協議約定,非同步接收過程中,當某個事件發生後(如圖1中取樣到V訊號為1後)的1個Cycle後(也可以約定多個Cycle)資料肯定是正確的;也可以消除這種skew問題,但是,這種實現需要後端設計時保證這些相關訊號的skew不會超過約定的週期,同時傳送方的資料也要保持足夠的週期數。如圖1中C2”訊號,如果skew2>Period(一個CKCycle),則收到V訊號一個Cycle後取樣資料還是錯誤的。

2.3復位策略

復位訊號中最主要的問題是Removal,也就是要保證所有的觸發器必須在同一節拍內離開Reset狀態,另外,Reset訊號完成的時刻不能與時鐘邊沿太靠近,以防止觸發器進入亞穩態(Metastability)。同步復位和非同步復位各有利弊,很難說哪種更有優勢。除了在編碼風格時講到的一個問題,在這裡再對兩種策略中可能出現的問題進行分析說明。同步復位有一個好處就是復位的時刻發生在時鐘的邊沿,這樣可以防止復位訊號的Glitch。如果是內部生產的Reset訊號,就必須保證Reset脈衝有足夠的寬,至少2個Cycles,能夠讓時鐘取樣到。同時,這也是它的缺點,因為它需要一個活動的時鐘,在加電時無法對一些電路產生復位。另外,綜合可能把同步復位的邏輯移到觸發器的D輸入端,作為普通的訊號處理,由於Reset訊號通常有傳輸負載和延遲,這樣處理會導致DataPath上較長的延遲。

非同步復位的最大好處就是不需要活動的時鐘,對於一些需要加電覆位的電路,如匯流排,是很必要的;同時,不像同步復位那樣,復位訊號會被用作D端的輸入邏輯,使得整個DataPath非常乾淨。如果非同步復位有Glitch可能使晶片進入復位狀態,這時可以通過兩級DFF接收Reset,再通過tree給復位觸發器使用,這樣可以消除輸入引起的Glitch,如果設計中有多個時鐘域,可以對每個時鐘分配兩個DFF接收Reset訊號。

2.4門控時鐘

GatedClock主要的優點在於能夠降低功耗面積,也可以簡化邏輯從而提高頻率。在編碼時需要考慮無Glitch的門控訊號設計。同時,在DFT設計時,由於觸發器的時鐘是前一級邏輯的輸出(其他派生時鐘也有同樣的問題),為了測試這類觸發器,需要為時鐘增加一級Mux,在正常工作模式下,採用派生時鐘,在掃描測試時採用正常的時鐘。門控時鐘的主要問題出現在綜合、CTS插入以及STA分析的時候,在後面將進行特別的分析討論。2.5匯流排實現

在這裡只討論匯流排實現的方式,不涉及匯流排的協議。在設計匯流排時將面臨著兩種基本方式的選擇,是採用三態匯流排還是採用多路選擇結構的匯流排。在全定製設計時,設計者似乎更喜歡採用三態,掛在總線上的各個部件可以分佈在晶片的各個部分。同時,由於可以減少連線的數量,它必須保證在任何時候,不發生匯流排衝突,如果多個驅動匯流排可能導致嚴重的錯誤,需要通過一些措施消除這種隱患,比如三態的使能通過解碼器產生Onehot的編碼,防止多驅動引起的邏輯錯誤和對晶片的損害;同時,三態匯流排需要連到上拉電阻上,以防止在一段時間內不驅動匯流排產生匯流排資料不確定,而DC等綜合並不支援。另外,三態匯流排的電容負載也是一個不可忽視的問題,對效能和麵積造成不利的影響,其負載主要來自匯流排連線的多個電路單元,匯流排佈局本身帶來一定的負載;最後,三態匯流排給DFT設計也帶來困難。基於這些理由,在非定製ASIC設計時,我們實在不必要選擇三態匯流排的方式。相比之下,採用多路選擇器的問題是較多連線帶來的佈線擁塞問題,選擇器的延遲問題基本上不是什麼問題,深亞微米設計中,門的延遲差別已經變少,同時多層金屬也帶來了足夠的佈線資源。3.邏輯綜合以及後端設計相關問題

3.1編碼風格檢查

DC對編碼風格的檢查提供良好的支援,在進行邏輯綜合之前最好先分析一下DC的log檔案,看是否有上述的或其他的一些編碼風格問題。通過set_dont_use命令可以禁止使用一些工藝相關的單元,all_registers帶引數也可以報告出設計中所用到的Latch。下面主要討論前面提到的一些情況在綜合以及後端實現時的特殊處理。同時,還有很多EDA工具提供編碼風格進行檢查。3.2非同步時鐘域

在編碼設計中我們通過劃分,將非同步時鐘域接收模組分離成獨立的模組,其他模組都採用單獨的時鐘,綜合約束相對簡單。對於那些帶有非同步時鐘域的模組,如果不進行約束,DC總是試圖去滿足取樣時鐘的setup/hold時間,事實上,設計者並不關心非同步時鐘域之間的這些問題,而其Metastability問題在編碼階段已經解決。通常,可以設定非同步時鐘域之間的Path為false_path。如:set_false_path-from[get_clocksCLKB]-to[get_clocksCLKA]

如果非同步介面資料的控制按照最後一種方式(也就是在約定的節拍內讀取資料),也就需要傳送方的資料skew控制在一定範圍內。由於沒有對這些路徑進行約束(雖然可以設定這些path的Maxdelay,但是這種約束對於skew的控制並不能取得好的效果),工具無法對這些路徑進行自動優化。因此最好採用手工佈局的方法,讓這些skew在一個可控的範圍內,在STA階段,也需要對這些skew進行單獨的分析。

3.3特殊時鐘訊號處理

門控時鐘像所有的內部時鐘一樣,時鐘的skew可能引起一些保持時間問題,預設條件下,時鐘樹綜合工具並不把邏輯閘相連的時鐘訊號連到時鐘樹上,非門控的觸發器上的時鐘是連在時鐘樹上,這個時鐘延遲是相當可觀的,為了控制門控時鐘與非門控時鐘的skew,通常從時鐘樹葉子節點的上一級引出時鐘訊號作為控制門的時鐘輸入。在STA階段需要對門控時鐘的Setup/Hold時間進行特殊分析,以及Glitch檢查。然後,我們再回顧一下例1的程式碼中的情況,可以用圖2的示意圖表示。

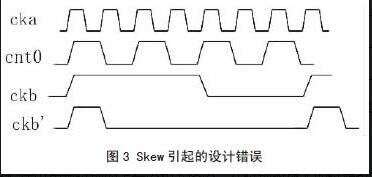

為了方便討論,時鐘樹插入以後,假設A與B之間有1個ckaCycle的skew;從圖3可以看到如果採用A點作加法器的輸入時產生的波形是ckb’,採用B點作為輸入時的波形是ckb,顯然,從例1的程式碼來看,ckb才是正確的。因此必須注意到,如果時鐘當作普通的訊號使用時可能帶來的問題,這類問題並沒有一個通用的解決辦法。在這個例子中,不採用時鐘樹上的訊號才是正確的,但是在另外一些應用中,就必須採用時鐘樹上的訊號。比如,時鐘是CK的兩個觸發器中鎖存的資料再由CK的高電平和低電平選擇輸出,那麼,這個時候就需要作為選擇訊號的CK從時鐘樹上拉過來。因此,如果設計中用到了時鐘訊號作為普通訊號的情況,在後端設計時就必須特殊處理。

如果設計中用到時鐘的上升沿和下降沿,在時鐘樹插入的時候也需要注意採用能夠平衡上升沿和下降沿的buffer,以保證較好的佔空比。

3.4復位訊號

復位中的Removal問題,對於非同步復位訊號,需要tree來平衡各個負載點上的skew,但是,Reset訊號的skew控制不像時鐘那麼嚴格,只要滿足Removal檢查就可以,PT等STA工具支援Removal的檢查。4.帶Post-Layout延遲資訊的門級模擬

門級模擬非常重要,它是最後一道關卡,可以從兩個方面入手,功能性驗證和時序驗證,最主要的是時序驗證,功能性驗證基本上由RTL級已經做了很多充分的工作,如果等價性驗證通過,功能性基本沒問題。時序模擬需要了解到一些模擬工具所採用的延遲模型,模擬工具的延遲計算都是基於一種簡單延遲模型: CircuitDelay=TransportDelayInertialDelay

時序模擬的目標是通過反標SDF檔案中延遲資訊,模擬一些在RTL級無法出現的一些情況,如復位,狀態機的翻轉。充分的驗證應該包括在bestcase下檢查短路徑的hold時間,在worstcase下檢查長路徑的setup時間。這些問題雖然在STA也作了檢查,門級模擬還是很必要的,尤其在用到時鐘雙邊沿的設計中;另外,對於有非同步時鐘介面的設計,需要調整非同步時鐘的相位關係,檢查是否存在著同步失敗問題;3.3中特殊時鐘問題,都可以通過門仿驗證其正確性;一些窄脈衝是否能通過IOBuffer。總之,這是一個非常重要的過程,需要花大量的時間去分析一些關鍵訊號的波形與設想的是否一致。

5.結束語

ASIC設計是一個複雜和全域性的過程,從結構設計、程式碼設計、綜合以及物理設計、時序分析、門級模擬,整個過程週期長,每個環節都不能孤立的思考。需要設計人員大量的時間去降低或消除設計中潛在的風險,才能設計出功能正確,效能滿足要求的產品。附加 典型ASIC設計具有下列相當複雜的流程:

1) 、結構及電氣規定。

2)、RTL級 典型ASIC設計具有下列相當複雜的流程:

1) 、結構及電氣規定。

2)、RTL級程式碼設計和模擬測試平臺檔案預備。

3)、為具有儲存單元的模組插進BIST(Design For test 設計)。

4)、為了驗證設計功能,進行完全設計的動態模擬。

5)、設計環境設定。包括使用的設計庫和其他一些環境變數。

6)、使用 Design Compiler工具,約束和綜合設計,並且加進掃描鏈(或者JTAG)。

7)、使用 Design Compiler自帶靜態時序分析器,進行模組級靜態時序分析。

8)、使用 Formality工具,進行 RTL級和綜合後門級網表的 Formal VerificatiON。

9)、版圖佈局佈線之前,使用PrimeTime工具進行整個設計的靜態時序分析。

10)、將時序約束前標註到版圖天生工具。

11)、時序驅動的單元佈局,時鐘樹插進和全域性佈線。

12)、將時鐘樹插進到DC的原始設計中。

13)、使用 Formality,對綜合後網表和插進時鐘樹網表進行 Formal Verification。

14)、從全域性佈線後的版圖中提取出估算的時間延時資訊。

15)、將估算的時間延時資訊反標註到Design Compiler或者 Primetime。

16)、在Primetime中進行靜態時序分析。

17)、在Design Compiler中進行設計優化。

18)、設計的具體佈線。

19)、從具體佈線的設計中提取出實際時間延時資訊。

20)、將提取出的實際時間延時資訊反標註到Design Compiler或者Primetime中。

21)、使用Primetime進行版圖後的靜態時序分析。

22)、在 Design Compiler中進行設計優化(假如需要)。

23)、進行版圖後帶時間資訊的門級模擬。

24)、 LVS和DRC驗證,然後流片。設計和模擬測試平臺檔案預備。

3)、為具有儲存單元的模組插進BIST(Design For test 設計)。

4)、為了驗證設計功能,進行完全設計的動態模擬。

5)、設計環境設定。包括使用的設計庫和其他一些環境變數。

6)、使用 Design Compiler工具,約束和綜合設計,並且加進掃描鏈(或者JTAG)。

7)、使用 Design Compiler自帶靜態時序分析器,進行模組級靜態時序分析。

8)、使用 Formality工具,進行 RTL級和綜合後門級網表的 Formal Verification。

9)、版圖佈局佈線之前,使用PrimeTime工具進行整個設計的靜態時序分析。

10)、將時序約束前標註到版圖天生工具。

11)、時序驅動的單元佈局,時鐘樹插進和全域性佈線。

12)、將時鐘樹插進到DC的原始設計中。

13)、使用 Formality,對綜合後網表和插進時鐘樹網表進行 Formal Verification。

14)、從全域性佈線後的版圖中提取出估算的時間延時資訊。

15)、將估算的時間延時資訊反標註到Design Compiler或者 Primetime。

16)、在Primetime中進行靜態時序分析。

17)、在Design Compiler中進行設計優化。

18)、設計的具體佈線。

19)、從具體佈線的設計中提取出實際時間延時資訊。

20)、將提取出的實際時間延時資訊反標註到Design Compiler或者Primetime中。

21)、使用Primetime進行版圖後的靜態時序分析。

22)、在 Design Compiler中進行設計優化(假如需要)。

23)、進行版圖後帶時間資訊的門級模擬。

24)、 LVS和DRC驗證,然後流片。

相關推薦

Verilog基礎知識5(ASIC設計中各個階段的關鍵問題彙總)

需求說明:Verilog設計 內容 :ASIC設計關鍵問題 來自 :時間的詩 ASIC的複雜性不斷提高,同時工藝在不斷地改進,如何在較短的時間內開發一個穩定的可重用的ASIC晶片的設計,並且一次性流片成功,這需要一個成熟的ASIC的設計方

Verilog基礎知識9(常見數字IC設計、FPGA工程師面試題 )

需求說明:Verilog設計 內容 :面試必備知識 來自 :時間的詩 1:什麼是同步邏輯和非同步邏輯? 同步邏輯是時鐘之間有固定的因果關係。非同步邏輯是各時鐘之間沒有

python基礎知識5(集合,高級特性,高階函數)

python** 刪除列表中重復的元素:l = [1,2,3,1,2,3]- 強制轉化列表為集合類型:list(set(l))- 將列表轉化為字典,拿出裏面的所有key值: dict.fromkeys(l).keys()** 實現switch的兩種方法:- if...elif...else...- 通過字典實

矩陣論基礎知識5(病態矩陣與條件數 )

1. 病態系統 現在有線性系統: Ax = b, 解方程 很容易得到解為: x1 = -100, x2 = -200. 如果在樣本採集時存在一個微小的誤差,比如,將 A 矩陣的係數 400 改變成 401: 則得到一個截然不同的解: x1 = 40000, x2 = 79800. 當解集 x 對 A 和

Verilog基礎知識0(`define、parameter、localparam三者的區別及舉例)

1、概述 `define:作用 -> 常用於定義常量可以跨模組、跨檔案; 範圍 -> 整個工程; pa

工作中能用到的基礎知識總結(二)

protected 構造函數 blog 繼承鏈 附加 調用 初始化 傳統 -s 簡介 繼承、封裝和多態是面向對象編程的重要特性。要想運用好,就必須熟悉這三種特性,本篇說說我對封裝、繼承和多態相關的知識總結。 知識點 一、訪問修飾符 C#中類及

老男孩python基礎知識練習題(一)中

rem python () 計算 輸出 長度 end 2個 下列表 20、字符串是否可叠代?如可以請使用for循環每一個元素? >>> name = " aleX ">>> for i in name:... print(i) 2

基礎知識漫談(2):從設計UI框架開始

說UI能延展出一丟丟的東西來,光java就有swing,swt/jface乃至javafx等等UI toolkit,在桌面上它們甚至都不是主流,在web端又有canvas、svg等等。 基於這些UI工具包\框架,又產生了大量通用的或者業務性的UI框架,比如Draw2d、GEF、easyUI乃至國

CCNA學習筆記 基礎知識回顧(5)

CCNA總結(簡) 一、 OSI參考模型 七層 應用層 抽象語言---->編碼 表示層 編碼---->二進位制 會話層 應用程式提供會話地址 類似:QQ號碼 *上三層就是應用程式對資訊程序加工處理,直到可以被傳輸(相當於OSI"工廠"生產貨物的車間);

Java基礎知識複習(九) -- 刪除ArrayList中的資料

首先初始化一個Hero集合,裡面放100個String物件,名稱分別是從 str 0 str 1 str 2 … str 99. 通過遍歷的手段,刪除掉名字編號是8的倍數的物件 若最簡單的使用位置查詢的方式來刪除對應物件會發現,若每次查詢並刪除,後面的物件會自動前移

深度學習FPGA實現基礎知識5(網友一致認可的----Deep Learning(深度學習)學習筆記整理及完整版下載)

需求說明:深度學習FPGA實現知識儲備 來自:http://blog.csdn.net/zouxy09/article/details/8775360/ Deep Learning(深度學習)

[基礎知識]5.C++中class與struct的區別

C++中class與struct的區別? 如果沒有標明成員函式或者成員變數的訪問許可權級別,那麼在struct中預設的是public,而在class中預設的是private。 相關知識點: 結構體是C語言的一種自定義的資料型別,在結構體中可以含有各種不同

linux基礎知識5——安裝、解除安裝軟體(rpm、yum)

rpm包 基本格式 firefox-52.7.2-1.el7.centos.x86_64 52.7.2-1 版本號 el7.centos.x86_64適用系統

javascript基礎知識整理(不定時更新)

nsh firefox 可用 splice mage true size -1 對數 1.js中真與假的定義: 真:true,非零數字,非空字符串,非空對象 假:false,數字零,空字符串,空對象(null),undefined 2.使用for循環對json進

操作系統基礎知識總結(一)

一個 快速 會有 處理死鎖 b2c fcm 死鎖 空間 存儲系統 1. 進程和線程的區別 進程 進程,即正在運行的程序,程序從硬盤載入到內存就變成進程。進程是資源的擁有者,每個進程都擁有著自己的內存空間與多個線程。 線程 線程是指令的執行者,是計算機執行指令的基本單元,一個

Java基礎知識整理(一)

顯式 sys 轉換 強制 print pri 字符 parse ger Java開發環境JDK(Java編輯器、Java運行工具(JRE作用)、Java文檔生成工具、Java打包工具) 1.Java是嚴格區分大小寫的。2.Java程序中一句連續的字符串不能分開在兩行書寫,

數據庫基礎知識:數據庫中的約束和三大範式

設計 一個 生效 訂單 詳細介紹 求長 山東 英文名稱 相關 一.數據庫中的範式: 範式, 英文名稱是 Normal Form,它是英國人 E.F.Codd(關系數據庫的老祖宗)在上個世紀70年代提出關系數據庫模型後總結出來的,範式是關系數據庫理論的基礎,也是我們在設計

linux雲自動化運維基礎知識2(系統的基本操作)

linux運維切換用戶 如圖所示:在命令提示符之後輸入su - username 註意:高級用戶切換到低級用戶不需要密碼,低級用戶切換身份需要密碼。註意:此處密碼無回顯。2.虛擬控制臺:Ctrl+Alt+F(1|7) 進入圖形 Ctrl+Alt+F(2~6) 進入虛擬控制

linux雲自動化運維基礎知識3(系統的基本命令)

linux運維1 datewatch -n 1 date ###讓date命令每秒執行一次,ctrl +c 推出監控模式date 11181115 ###把系統時間設定為11月18日11:15 格式:月月天天小時分鐘date 111811152016.55 ##2016表示年(可以

linux雲自動化運維基礎知識5.6(用戶管理及文件權限)

linux運維用戶理解用戶就是系統使用者的身份在系統中用戶存儲為若幹竄字符+若幹個系統配置文件用戶信息涉及到的系統配置文件:/etc/passwd ###用戶信息用戶:密碼:uid:gid:說明:家目錄:用戶使用的shell/etc/shadow ###用戶認證信息用戶:密碼:最後