分段,分頁與段頁式儲存管理

一. 分頁儲存管理

1.基本思想

使用者程式的地址空間被劃分成若干固定大小的區域,稱為“頁”,相應地,記憶體空間分成若干個物理塊,頁和塊的大小相等。可將使用者程式的任一頁放在記憶體的任一塊中,實現了離散分配。

1) 等分記憶體

頁式儲存管理將記憶體空間劃分成等長的若干物理塊,成為物理頁面也成為物理塊,每個物理塊的大小一般取2的整數冪。記憶體的所有物理塊從0開始編號,稱作物理頁號。

2) 邏輯地址

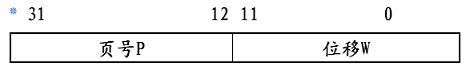

系統將程式的邏輯空間按照同樣大小也劃分成若干頁面,稱為邏輯頁面也稱為頁。程式的各個邏輯頁面從0開始依次編號,稱作邏輯頁號或相對頁號。每個頁面內從0開始編址,稱為頁內地址。程式中的邏輯地址由兩部分組成:頁號P和頁內位移量W。

在執行一個程式之前,記憶體管理器需要的準備工作:

1) 確定程式的頁數

2) 在主存中留出足夠的空閒頁面

3) 將程式的所有頁面載入主存裡。(靜態的分頁,頁面無需連續)

2. 分頁儲存管理的地址機構

頁號x位,每個作業最多2的x次方頁,頁內位移量的位數表示頁的大小,若頁內位移量y位,則2的y次方,即頁的大小,頁內地址從000000000000開始到2的y次方

若給定一個邏輯地址為A,頁面大小為L,則

頁號P=INT[A/L],頁內地址W=A MOD L

3.記憶體分配

相鄰的頁面在記憶體中不一定相鄰,即分配給程式的記憶體塊之間不一定連續。對程式地址空間的分頁是系統自動進行的,即對使用者是透明的。由於頁面尺寸為2的整數次冪,故相對地址中的高位部分即為頁號,低位部分為頁內地址。

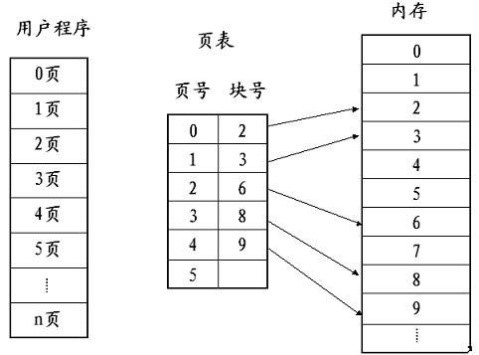

4. 頁表

分頁系統中,允許將程序的每一頁離散地儲存在記憶體的任一物理塊中,為了能在記憶體中找到每個頁面對應的物理塊,系統為每個程序建立一張頁表,用於記錄程序邏輯頁面與記憶體物理頁面之間的對應關係。頁表的作用是實現從頁號到物理塊號的地址對映,地址空間有多少頁,該頁表裡就登記多少行,且按邏輯頁的順序排列,形如:

5. 地址變換

頁式虛擬儲存系統的邏輯地址是由頁號和頁內地址兩部分組成,地址變換過程如圖7-3所示。假定頁面的大小為4K,圖7-3中所示的十進位制邏輯地址8203經過地址變換後,形成的實體地址a應為十進位制。

頁號: 8203/4096 = 2;頁內偏移:8203%4096= 11;實體地址:物理塊號*頁面大小+ 頁內偏移= 28683。

6. 具有快表的地址變換機構

分頁系統中,CPU每次要存取一個數據,都要兩次訪問記憶體(訪問頁表、訪問實際實體地址)。為提高地址變換速度,增設一個具有並行查詢能力的特殊高速緩衝儲存器,稱為“聯想儲存器”或“快表”,存放當前訪問的頁表項。

7.頁面的共享與保護

當多個不同程序中需要有相同頁面資訊時,可以在主存中只保留一個副本,只要讓這些程序各自的有關項中指向記憶體同一塊號即可。同時在頁表中設定相應的“存取許可權”,對不同程序的訪問許可權進行各種必要的限制。

二.分段儲存管理

1.基本思想

頁面是主存物理空間中劃分出來的等長的固定區域。分頁方式的優點是頁長固定,因而便於構造頁表、易於管理,且不存在外碎片。但分頁方式的缺點是頁長與程式的邏輯大小不相關。例如,某個時刻一個子程式可能有一部分在主存中,另一部分則在輔存中。這不利於程式設計時的獨立性,並給換入換出處理、儲存保護和儲存共享等操作造成麻煩。

另一種劃分可定址的儲存空間的方法稱為分段。段是按照程式的自然分界劃分的長度可以動態改變的區域。通常,程式設計師把子程式、運算元和常數等不同型別的資料劃分到不同的段中,並且每個程式可以有多個相同型別的段。

段表本身也是一個段,可以存在輔存中,但一般是駐留在主存中。

將使用者程式地址空間分成若干個大小不等的段,每段可以定義一組相對完整的邏輯資訊。儲存分配時,以段為單位,段與段在記憶體中可以不相鄰接,也實現了離散分配。

2. 分段地址結構

作業的地址空間被劃分為若干個段,每個段定義了一組邏輯資訊。例程式段、資料段等。每個段都從0開始編址,並採用一段連續的地址空間。段的長度由相應的邏輯資訊組的長度決定,因而各段長度不等。整個作業的地址空間是二維的。

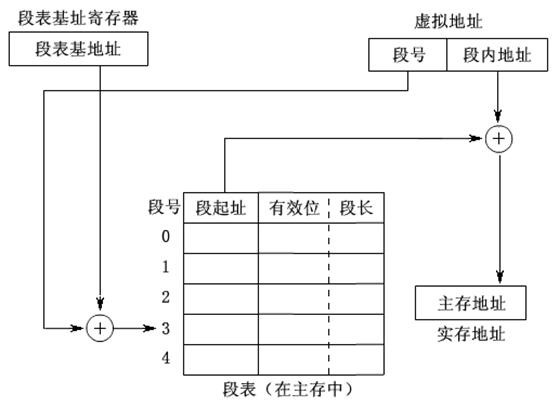

在段式虛擬儲存系統中,虛擬地址由段號和段內地址組成,虛擬地址到實存地址的變換通過段表來實現。每個程式設定一個段表,段表的每一個表項對應一個段,每個表項至少包括三個欄位:有效位(指明該段是否已經調入主存)、段起址(該段在實存中的首地址)和段長(記錄該段的實際長度)。

3. 地址變換

針對每一個虛擬地址,儲存管理部件首先以段號S為索引訪問段表的第S個表項。若該表項的有效位為1,則將虛擬地址的段內地址D與該表項的段長欄位比較;若段內地址較大則說明地址越界,將產生地址越界中斷;否則,將該表項的段起址與段內地址相加,求得主存實地址並訪存。如果該表項的有效位為0,則產生缺頁中斷,從輔存中調入該頁,並修改段表。段式虛擬儲存器虛實地址變換過程如圖所示。

絕對地址=根據段號找到段表中的起始地址+段內地址 (如果段內地址超過限長則產生“地址越界”程式性中斷事件達到儲存保護)

4. 分段儲存方式的優缺點

分頁對程式設計師而言是不可見的,而分段通常對程式設計師而言是可見的,因而分段為組織程式和資料提供了方便。與頁式虛擬儲存器相比,段式虛擬儲存器有許多優點:

(1) 段的邏輯獨立性使其易於編譯、管理、修改和保護,也便於多道程式共享。

(2) 段長可以根據需要動態改變,允許自由排程,以便有效利用主存空間。

(3) 方便程式設計,分段共享,分段保護,動態連結,動態增長

因為段的長度不固定,段式虛擬儲存器也有一些缺點:

(1) 主存空間分配比較麻煩。

(2) 容易在段間留下許多碎片,造成儲存空間利用率降低。

(3) 由於段長不一定是2的整數次冪,因而不能簡單地像分頁方式那樣用虛擬地址和實存地址的最低若干二進位制位作為段內地址,並與段號進行直接拼接,必須用加法操作通過段起址與段內地址的求和運算得到實體地址。因此,段式儲存管理比頁式儲存管理方式需要更多的硬體支援。

三.段頁式儲存

1. 段頁式儲存管理的基本思想

段頁式儲存組織是分段式和分頁式結合的儲存組織方法,這樣可充分利用分段管理和分頁管理的優點。

(1) 用分段方法來分配和管理虛擬儲存器。程式的地址空間按邏輯單位分成基本獨立的段,而每一段有自己的段名,再把每段分成固定大小的若干頁。

(2) 用分頁方法來分配和管理實存。即把整個主存分成與上述頁大小相等的儲存塊,可裝入作業的任何一頁。程式對記憶體的調入或調出是按頁進行的。但它又可按段實現共享和保護。

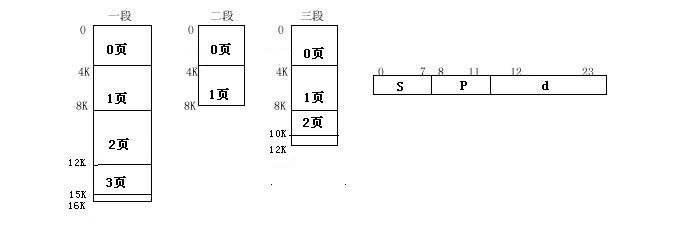

地址空間圖

(3) 邏輯地址結構。一個邏輯地址用三個引數表示:段號S;頁號P;頁內地址d。

邏輯地址結構

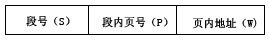

(4)段表、頁表、段表地址暫存器。為了進行地址轉換,系統為每個作業建立一個段表,並且要為該作業段表中的每一個段建立一個頁表。系統中有一個段表地址暫存器來指出作業的段表起始地址和段表長度。

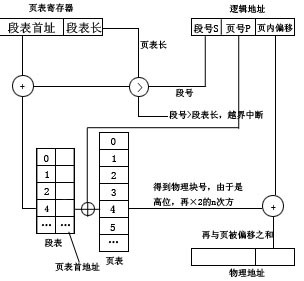

2.地址變換過程

1) 慢速地址轉換過程

一個邏輯地址為:基地址x、段號s、頁號p和頁內地址d,求實體地址(((x)+s)+p)*2^(11)+d

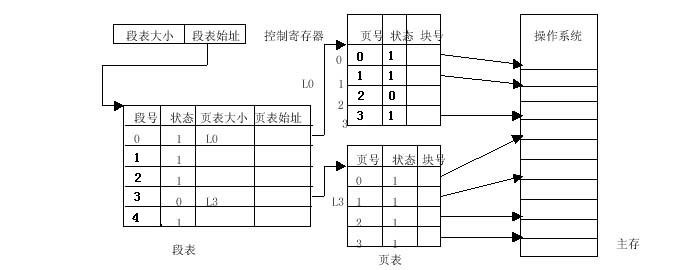

在段頁式系統中,為了便於實現地址變換,須配置一個段表暫存器,其中存放段表始址和段表長TL。

1) 進行地址變換時,首先利用段號S,將它與段表長TL進行比較。若S<TL,表示未越界

2) 於是利用段表始址和段號來求出該段所對應的段表項在段表中的位置,從中得到該段的頁表始址

3) 利用邏輯地址中的段內頁號P來獲得對應頁的頁表項位置,從中讀出該頁所在的物理塊號b

4) 再利用塊號b和頁內地址來構成實體地址。

上圖示出了段頁式系統中的地址變換機構。在段頁式系統中,為了獲得一條指令或資料,須三次訪問記憶體。第一次訪問是訪問記憶體中的段表,從中取得頁表始址;第二次訪問是訪問記憶體中的頁表,從中取出該頁所在的物理塊號,並將該塊號與頁內地址一起形成指令或資料的實體地址;第三次訪問才是真正從第二次訪問所得的地址中,取出指令或資料。

顯然,這使訪問記憶體的次數增加了近兩倍。為了提高執行速度,在地址變換機構中增設一個高速緩衝暫存器。每次訪問它時,都須同時利用段號和頁號去檢索快取記憶體,若找到匹配的表項,便可從中得到相應頁的物理塊號,用來與頁內地址一起形成實體地址;若未找到匹配表項,則仍須再三次訪問記憶體。

3.段頁式儲存管理的優缺點

優點

(1) 它提供了大量的虛擬儲存空間。

(2) 能有效地利用主存,為組織多道程式執行提供了方便。

缺點:

(1) 增加了硬體成本、系統的複雜性和管理上的開消。

(2) 存在著系統發生抖動的危險。

(3) 存在著內碎片。

(4) 還有各種表格要佔用主存空間。

段頁式儲存管理技術對當前的大、中型計算機系統來說,算是最通用、最靈活的一種方案。