Verilog十大基本功0(阻塞賦值與非阻塞賦值)

需求說明:Verilog設計基礎

內容 :阻塞賦值和非阻塞賦值

來自 :時間的詩

前言:

阻塞與非阻塞賦值是 Verilog 語言中最基本的部分,也是讓大部分 Verilog 新手最困惑的地方。

關於阻塞與非阻塞的著作文章可謂汗牛充棟,這些文章對阻塞與非阻塞賦值的原理進行了非常詳細的講

解,但新手讀了之後依然有種似懂非懂的感覺,編碼過程中一如既往的犯錯。所以,本文的目的立足於

提供一種實用化的解決方案,用最簡單的語言和形象的類比讓新手能夠一目瞭然的明白正確的編碼方式

以及相應的電路行為邏輯,關於模擬細節的講解不是本文重點,需要了解更多細節的朋友可以參考文後

列舉的參考文獻。

本文共分為三部分:

第一部分是正確使用阻塞與非阻塞賦值的基本原則。

第二部分是阻塞與非阻塞賦值對應的電路行為邏輯。

第三部分是阻塞與非阻塞賦值的原理簡介。

第一部分 正確使用阻塞與非阻塞賦值的基本原則(Golden Rule)

編碼原則很多,就阻塞非阻塞賦值而言,新手最需要牢記的是其中三條:

1、時序邏輯一定用非阻塞賦值”<=”,一旦看到敏感列表有 posedge 就用”<=”。

2、組合邏輯一定用”=” ,一旦敏感列表沒有 posedge 就用”=”,一旦看到 assign 就用”=”。

3、時序邏輯和組合邏輯分成不同的模組,即一個 always 模組裡面只能出現非阻塞賦值”<=”或者”=”。如

果發現兩種賦值並存,一個字”改”,心存僥倖可能會給後續工作帶來更多麻煩。

以上三條,對新手而言不必追求為什麼,需要的就是條件反射的照章辦事。最後說一句,新手可能記不

住哪個符號是阻塞賦值,哪個是非阻塞賦值,大家可以數數, ”非阻塞賦值”一共 5 個字,“阻塞賦值“ 4

個字,所以非阻塞用的符號”<=”比阻塞賦值用的符號”=”長。

第二部分 阻塞與非阻塞賦值對應的電路行為邏輯

第一節給出了三條最基本的編碼原則,有個朋友可能會想,按照這三條編碼原則寫出來的程式碼會按怎樣的邏輯工作呢?這一節就是回答這個問題。

首先解釋一下阻塞賦值與非阻塞賦值的含義。

所謂的阻塞賦值”=”就是說, 在這個語句沒有執行完之前,後面的語句是不執行的。

這裡執行的含義是指完成變數值的更新。

非阻塞賦值”<=”是指, 所有的語句可以併發執行,而前面的值是否執行完畢不會影響後面的語句,

換句話說,語句的順序是無關緊要的。

舉個例子,假設一個模組,有 2 個暫存器, b 和 c,初值都是 1。 a 為輸入訊號線。在某個時刻,因為某

種原因,模組被觸發執行。對於組合邏輯而言,一般是輸入訊號值變了,對於時序邏輯而言,一般是時

鍾沿到了。

首先看組合邏輯:假設輸入 a = 2;

[email protected](a ,b)

begin

b = a;

c = b;

end由於是阻塞賦值,所以首先執行完第一句 b=a,執行完成之後 b=2。接著執行 c=b,執行完成後 c=2,一

次模擬結束後 b=c=2;

對於時序邏輯而言,依然假設 a =2;

[email protected](posedge clk)

begin

b <= a;

c <= b;

end由於是非阻塞賦值,首先執行第一句 b<=a,這時候 a = 2,但是還沒有執行完第一句的時候,第二句 c<=b

也執行了,由於第一句沒有執行完, b 的值還是 1,這時候賦值給 c 的值也是 1。執行完畢的結果就是

c=1,b=2.等到模組再次被觸發的時候 c 的值更新為 2。

第三部分 阻塞與非阻塞賦值的原理簡介

有個朋友可能就會問了,憑啥第一句執行到一半就該第二句執行呢?到底是第一句先完成賦值呢還是第二句

先完成賦值?答案是,誰先完成賦值都沒關係,結果是一樣的。

為什麼說結果一樣呢? 因為兩種賦值方式分別是按照下面的順序執行的。

阻塞賦值,就跟 C 語言一樣,嚴格按照程式碼書寫的先後順序執行,所有值都是立即更新,並且在下面的

語句中按照新值執行。

而時序電路就不一樣了,大家可以這麼理解時序邏輯的程式碼行為,一次執行分為兩輪:

第一輪是所有的左值都先賦給臨時變數,

第二輪用輸入值以及和右值同名的臨時變數值去更新左值。

比如上面的例子,第一輪,賦給臨時變數: tempc=c;tempb=b。

第二輪,臨時變數更新左值, b = a;c = tempb;output = tempc。

從上面的分析也可以看出,組合邏輯的結果與程式碼順序直接相關,而時序邏輯與程式碼順序沒有關係。這就是所

謂的順序執行(組合邏輯)與併發執行(時序邏輯)。

為了進一步理解這兩種賦值方式的行為,下面用對應的電路進行說明,以前面的程式碼為例。大家首先閉

上眼睛想想,對應的電路是什麼樣子的呢?

其實答案很簡單,對於阻塞賦值來說,如圖一所示,綜合的結果就是一根導線,當然,可能有反相器,

buf 什麼的,反正還是可以看作一根線。

到這裡,應該就很容易理解順序執行的行為方式了。

有細心的朋友可能會問,如果換種寫法呢?

[email protected](a,b)

begin

c = b;

b = a;

end很顯然,這種電路的行為跟之前是不一樣的,從邏輯來看會產生類似於非阻塞賦值的結果,但很顯然不

滿足非阻塞賦值併發執行的特點。如果把輸入電平 a 觸發改成時鐘邊沿觸發 posedge clk,出來的就是寄

存器,但這違反了時序邏輯不用阻塞賦值的原則,所以嚴重不推薦。至於這種組合邏輯描述方式出來的

電路是啥我也不知道,大家可以自己綜合看看,或者哪位高人補上~~應該注意的是,如果想象不出這種

怪異的 coding 方式會產生何種電路,就不要這麼寫,因為實現這種邏輯最好的辦法是採用非阻塞方式描

述。

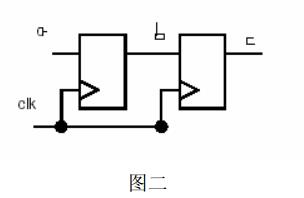

而對於非阻塞賦值而言,如圖二所示,綜合出來的結果就是 2 個暫存器。對 b,c 賦值的過程就是暫存器

輸入取樣的過程,很顯然兩個取樣是同時進行的,而且一次時鐘沿只會取樣一次,所以輸入值 a 會首先

被取樣到 b,再在下一個時鐘被取樣到 c.

總結一下:

關於兩種賦值方式,首先講述了程式碼執行的過程,然後用直連線和暫存器分別對應了兩種描

述方式。應該指出的是,非阻塞賦值用暫存器的類比是完全準確的,而阻塞賦值用直連線的類比卻未必

準確,只不過因為一般認為直連線是從輸入到輸出依次更新的,而且沒有傳輸以外的延遲,所以這種類

比有助於新人理解,雖然不夠嚴密。大家熟悉了之後就應該按照更嚴謹的方式去理解。

補充一下,如果寫出下面這樣的程式碼,在時序電路中使用阻塞賦值的話,綜合出來就只有一個暫存器,不是兩個,寄

存器的輸入 D 端是 a,輸出 Q 端是 b 和 c,兩個訊號在同一根線上

[email protected](posedge clk)

begin

b = a;

c = b;

end所以這樣的寫法很容易造成設計和綜合結果不匹配的情況,即使不是要設計兩級暫存器,也最好不要用阻塞賦值。

另外一個就是,腦袋裡面需要有時序邏輯和組合邏輯的框圖。

將組合邏輯和時序邏輯分開寫,組合邏輯用=,時序邏輯用<=,

時序邏輯內的判斷越簡單越好,儘量都放在組合邏輯裡面做,時序邏輯只負責 flop 一下。

所以,最重要的是, 新手應該嚴格按照規則來,見到 posedge 就寫 <= ,而根本不考慮 = ,免得綜合出怪東西來。

這種程式碼應該嚴格杜絕,呵呵~~

相關推薦

Verilog十大基本功0(阻塞賦值與非阻塞賦值)

需求說明:Verilog設計基礎 內容 :阻塞賦值和非阻塞賦值 來自 :時間的詩 前言: 阻塞與非阻塞賦值是 Verilog 語言中最基本的部分,也是讓大部分 Verilog 新手最困惑的地方。 關於阻塞與非阻塞的著作文章可謂汗牛充棟,

Verilog十大基本功1(流水線設計Pipeline Design)

需求說明:Verilog設計基礎 內容 :流水線設計 來自 :時間的詩 流水線設計 前言: 本文從四部分對流水線設計進行分析,具體如下:

Verilog十大基本功2(testbench的設計 檔案讀取和寫入操作 原始碼)

需求說明:Verilog設計基礎 內容 :testbench的設計 讀取檔案 寫入檔案 來自 :時間的詩 十大基本功之 testbench 1. 激勵的產生 對於 testbench 而言,埠應當和被測試的 module 一一對應。 埠分

Verilog十大基本功7 (IC設計經典書籍)

來自:https://blog.csdn.net/limanjihe/article/details/52674827 學習數字IC設計一段時間,總結一下自己學習期間遇到的比較好的書籍,希望能給大家一個指導和借鑑,同時也希望大家相互學習交流。 1 《V

Verilog十大基本功6 (關於Verilog的可綜合性)

來自:https://blog.csdn.net/a8039974/article/details/43635425 可綜合模型的結構 如果程式只用於模擬,那麼幾乎所有的語法和程式設計語句都可以使用。但如果程式是用於硬體實現,那麼我們就

Verilog十大基本功5 (關於verilog中的signed型別)

來自:https://www.cnblogs.com/lianjiehere/p/3968103.html 在數位電路中,出於應用的需要,我們可以使用無符號數,即包括0及整數的集合;也可以使用有符號數,即包括0和正負數的集合。在更加複雜的系統中,也許這兩種型別的數,我們都會用到

verilog中阻塞賦值與 非阻塞賦值的區別

非阻塞(Non_Blocking)賦值方式( 如 b <= a; ), 塊結束後才完成賦值操作,值並不是立刻就改變的, 這是一種比較常用的賦值方法。(特別在編寫可綜合模組時)。 阻塞(Blocking)賦值方式( 如 b = a; ), 賦值語句執行完後,塊才

Verilog堵塞賦值與非堵塞賦值

解決 ont mark con 原理 inpu 特點 全部 cal verilog設計進階 時間:2014年5月6日星期二 主要收獲: 1.堵塞賦值與非堵塞賦值; 2.代碼測試; 3.組合邏輯電路和時序邏輯電路。

RTL基本知識:阻塞賦值與非阻塞賦值

ini 規則 rac init 基本知識 monitor 當前 並且 ima 0 醜話說在前邊 RHS:運算符(= or <=)右側的表達式 LHS:運算符(= or <=)左側的表達式 競爭(Race Condition):在同一仿真時間槽(time-slot

JAVA NIO(四)阻塞式IO與非阻塞式IO

1.阻塞與非阻塞IO模型:由於程序是不可直接訪問外部裝置的,所以只能呼叫核心去呼叫外部的裝置(上下文切換),然後外部裝置比如磁碟,讀出儲存在裝置自身的資料傳送給核心緩衝區,核心緩衝區在copy資料到使用者程序的緩衝區。包含兩個步驟:一將資料讀到核心,二將資料從核心copy使用

阻塞賦值與非阻塞賦值的再分析

在Verilog HDL設計中,經常會遇到阻塞賦值與非阻塞賦值,這是學習邏輯設計時最基礎的知識點。設計者經常會在書中看到一些建議:什麼時候該用阻塞賦值,什麼情況下使用非阻塞賦值。可是,如果僅僅按照這樣的設計推薦來進行設計的話,經常會碰到一頭霧水的情況。本文就對阻塞賦值和非阻

復制目錄下所有文件(隱藏文件與非隱藏文件)

分享 info bubuko img inf dir .com png mage cp /source-dirname/. /target-dirname(用.表示自己) 復制目錄下所有文件(隱藏文件與非隱藏文件)

React 學習筆記(二) (事件、約束與非約束性元件)

事件物件 方法一 方法二 方法三 表單取值 鍵盤事件 react實現雙向資料繫結 約束性元件和非約束性元件 非約束性元件 defaultValue:<input type="text" defaultValue=‘111’/>

同步與阻塞,非同步與非阻塞的區別

同步與非同步是對應的,它們是執行緒之間的關係,兩個執行緒之間要麼是同步的,要麼是非同步的。 阻塞與非阻塞是對同一個執行緒來說的,在某個時刻,執行緒要麼處於阻塞,要麼處於非阻塞。 阻塞是使用同步機制的結果,非阻塞則是使用非同步機制的結果。 處理大併發之一 對非同步

深入理解併發/並行,阻塞/非阻塞,同步/非同步 同步與阻塞,非同步與非阻塞的區別

同步與非同步是對應的,它們是執行緒之間的關係,兩個執行緒之間要麼是同步的,要麼是非同步的。阻塞與非阻塞是對同一個執行緒來說的,在某個時刻,執行緒要麼處於阻塞,要麼處於非阻塞。阻塞是使用同步機制的結果,非阻塞則是使用非同步機制的結果。 深入理解併發/並行,阻塞/非阻塞,同步/非同步 1. 阻塞,非

同步與阻塞,非同步與非阻塞的區別轉載

同步與阻塞,非同步與非阻塞的區別 同步與非同步是對應的,它們是執行緒之間的關係,兩個執行緒之間要麼是同步的,要麼是非同步的。 阻塞與非阻塞是對同一個執行緒來說的,在某個時刻,執行緒要麼處於阻塞,要麼處於非阻塞。 阻塞是使用同步機制的結果,非阻塞則是使用非同步機制的結果。 處理大併發之

阻塞執行緒與非阻塞執行緒

阻塞執行緒:A,B執行緒有一個公共的資源,比如說變數params,當A訪問params時,給params加鎖,而這時B要訪問params時,它只有等待A釋放params鎖時,才可以訪問; 非阻塞執行緒:A,B執行緒有一個公共的資源,比如說變數params,當A訪問param

關於JVM記憶體(執行緒共享與非執行緒共享)

大多數 JVM 將記憶體區域劃分為 Method Area(Non-Heap)(方法區) ,Heap(堆) , Program Counter Register(程式計數器) , VM Stack(虛擬機器棧,也有翻譯成JAVA 方法棧的),Native M

Verilog HDL 初級入門知識簡單講解(wire 和 reg 型別的區別, always 和 assign 的區別,“阻塞”賦值 和 “非阻塞賦值”的區別 )

本文轉載自原作者:姚紀元,原文地址已失效 很多剛學Verilog HDL (硬體描述語言)的朋友肯定會對阻塞賦值和非阻塞賦值比較疑惑,那我們就一起來拋開這層迷霧吧。首先我們要理解兩種變數型別 Net Type(連線型)和

Verilog 初級入門概念講解(wire 和 reg 型別的區別, always 和 assign 的區別,“阻塞”賦值 和 “非阻塞賦值”的區別 )

很多剛學Verilog HDL (硬體描述語言)的朋友肯定會對阻塞賦值和非阻塞賦值比較疑惑,那我們就一起來拋開這層迷霧吧。 首先我們要理解兩種變數型別 Net Type(連線型)和 Register Type (暫存器型)。(有些參考書上有分為3種類型,這個無關緊要) Net Ty