簡單介紹I2C匯流排

阿新 • • 發佈:2019-01-31

轉自 《I2C匯流排協議應用指導書》 魏芬 編著

說的簡單通俗,所以轉載了。

7.2 I2C匯流排的訊號線

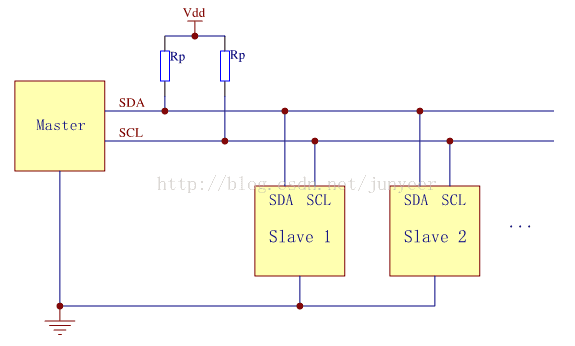

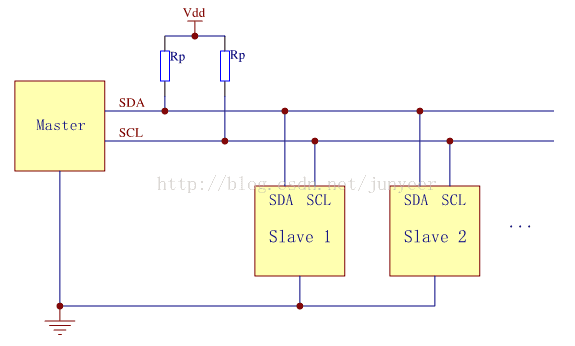

I2C匯流排只需要由兩根訊號線組成,一根是序列資料線SDA,另一根是序列時鐘線 SCL。一般具有I2C匯流排的器件其SDA和SCL引腳都是漏極開路(或集電極開路)輸出結構。因此實際使用時,SDA和SCL訊號線都必須要加上拉電阻(Rp,Pull-Up Resistor)。上拉電阻一般取值3~10KΩ。開漏結構的好處是:當匯流排空閒時,這兩條訊號線都保持高電平,幾乎不消耗電流;電氣相容性好,上拉電阻接5V電源就能與 5V 邏輯器件介面,上拉電阻接3V電源又能與 3V邏輯器件介面;因為是開漏結構,所以不同器件的SDA與SDA之間、SCL與 SCL之間可以直接相連,不需要額外的轉換電路。

(2) 接收器(Receiver):從匯流排接收資料的器件;

(3) 主機(Mater):初始化傳送、產生時鐘訊號和終止傳送的器件;

(4) 從機(Slave):被主機定址的器件。

I2C 匯流排是雙向傳輸的匯流排,因此主機和從機都可能成為傳送器和接收器。如果主機向從機發送資料,則主機是傳送器,而從機是接收器;如果主機從從機讀取資料,則主機是接收器,而從機是傳送器。

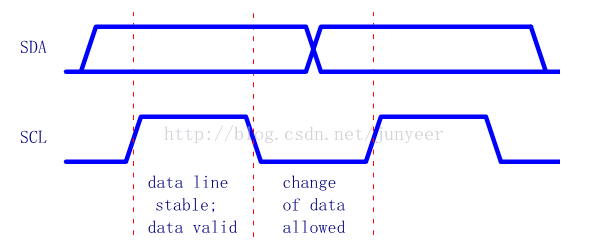

某些其它的序列匯流排協議可能規定資料在時鐘訊號的邊沿(上升沿或下降沿)有效,而I2C匯流排則是電平有效。

停止條件:當SCL處於高電平期間時,SDA從低電平向高電平跳變時產生停止條件。匯流排在停止條件產生後處於空閒狀態。停止條件簡記為 P。

在圖 7.4 和圖 7.5 中,各種符號的意義為:

S:起始位(START);

SA:從機地址(Slave Address),7位從機地址;

W:寫標誌位(Write),1位寫標誌;

R:讀標誌位(Read),1位讀標誌;

A:應答位(Acknowlege),1位應答;

A:非應答位(Not Acknowledge) ,1位非應答;

D:資料(Data),每個資料都必須是8位;

P:停止位(STOP);

陰影:主機產生的訊號;

無陰影:從機產生的訊號。

應當注意的是,與圖7.5中的情況不同的是,在圖7.4 中,主機向從機發送最後一個位元組的資料時,從機可能應答也可能非應答,但不管怎樣主機都可以產生停止條件。如果主機在向從機發送資料(甚至包括從機地址在內)時檢測到從機非應答,則應當及時停止傳輸。

主機連續向從機發送或從從機接收多個位元組資料的情況也很容易理解,下面直接給出相關時序圖。

圖 7.10 給出了帶有重複起始條件的多位元組資料傳輸格式示意圖,圖中的各種符號的意義與第 7.10 節中的相同。要特別注意圖中重複起始條件Sr的用法。如果讀者有興趣的話,可以自行畫出其對應的時序圖。

在第8章的I2C匯流排軟體包中,已經同時考慮到了無子地址器件和有子地址器件的情況。

第7章 I2C 匯流排簡介

ZLG7290B與微控制器的介面形式是I2C序列匯流排,因此有必要簡要地介紹一下I2C匯流排協議標準。第8章還給出了用C51編寫的I2C匯流排軟體包,以供參考學習。7.1 I2C匯流排概述

飛利浦(Philips)於20多年前發明了一種簡單的雙向二線制序列通訊匯流排,這個匯流排被稱為Inter-IC或者I2C匯流排。目前I2C匯流排已經成為業界嵌入式應用的標準解決方案,被廣泛地應用在各式各樣基於微控器的專業、消費與電信產品中,作為控制、診斷與電源管理匯流排。多個符合I2C匯流排標準的器件都可以通過同一條I2C匯流排進行通訊,而不需要額外的地址譯碼器。由於I2C是一種兩線式序列匯流排,因此簡單的操作特性成為它快速崛起成為業界標準的關鍵因素。7.2 I2C匯流排的訊號線

I2C匯流排只需要由兩根訊號線組成,一根是序列資料線SDA,另一根是序列時鐘線 SCL。一般具有I2C匯流排的器件其SDA和SCL引腳都是漏極開路(或集電極開路)輸出結構。因此實際使用時,SDA和SCL訊號線都必須要加上拉電阻(Rp,Pull-Up Resistor)。上拉電阻一般取值3~10KΩ。開漏結構的好處是:當匯流排空閒時,這兩條訊號線都保持高電平,幾乎不消耗電流;電氣相容性好,上拉電阻接5V電源就能與 5V 邏輯器件介面,上拉電阻接3V電源又能與 3V邏輯器件介面;因為是開漏結構,所以不同器件的SDA與SDA之間、SCL與 SCL之間可以直接相連,不需要額外的轉換電路。

圖7.1 I2C匯流排訊號連線示意圖

7.3 I2C匯流排基本概念

(1) 傳送器(Transmitter):傳送資料到匯流排的器件;(2) 接收器(Receiver):從匯流排接收資料的器件;

(3) 主機(Mater):初始化傳送、產生時鐘訊號和終止傳送的器件;

(4) 從機(Slave):被主機定址的器件。

I2C 匯流排是雙向傳輸的匯流排,因此主機和從機都可能成為傳送器和接收器。如果主機向從機發送資料,則主機是傳送器,而從機是接收器;如果主機從從機讀取資料,則主機是接收器,而從機是傳送器。

7.4 I2C匯流排資料傳送速率

I2C匯流排的通訊速率受主機控制,能快能慢。但是最高速率是有限制的,I2C總線上資料的傳輸速率在標準模式(Standard-mode)下最快可達100Kb/s。7.5 I2C總線上資料的有效性(Data validity)

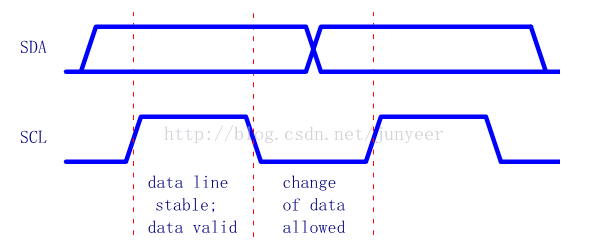

某些其它的序列匯流排協議可能規定資料在時鐘訊號的邊沿(上升沿或下降沿)有效,而I2C匯流排則是電平有效。

圖7.2 I2C總線上資料有效性的示意圖

7.6 起始條件和停止條件(START and STOP conditions)

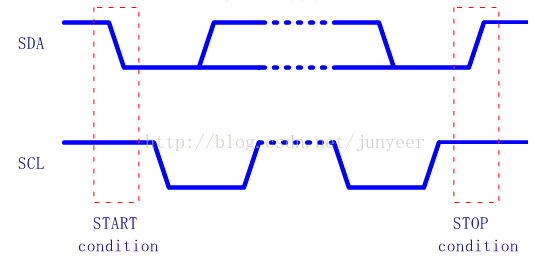

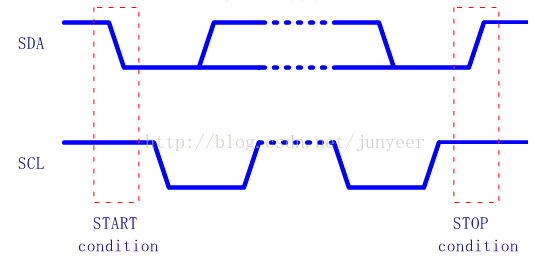

起始條件:當SCL處於高電平期間時,SDA從高電平向低電平跳變時產生起始條件。 匯流排在起始條件產生後便處於忙的狀態。起始條件常常簡記為S。停止條件:當SCL處於高電平期間時,SDA從低電平向高電平跳變時產生停止條件。匯流排在停止條件產生後處於空閒狀態。停止條件簡記為 P。

圖7.3 I2C起始條件和停止條件示意圖

7.7 從機地址(Slave Address)

I2C匯流排不需要額外的地址譯碼器和片選訊號。多個具有I2C匯流排介面的器件都可以連線到同一條I2C總線上,它們之間通過器件地址來區分。主機是主控器件,它不需要器件地址,其它器件都屬於從機,要有器件地址。必須保證同一條I2C總線上所有從機的地址都是唯一確定的,不能有重複,否則I2C匯流排將不能正常工作。一般從機地址由7位地址位和一位讀寫標誌(R/W)組成,7位地址佔據高7位,讀寫位在最後。讀寫位是0,表示主機將要向從機寫入資料;讀寫位是1,則表示主機將要從從機讀取資料。7.8 資料傳輸的基本格式

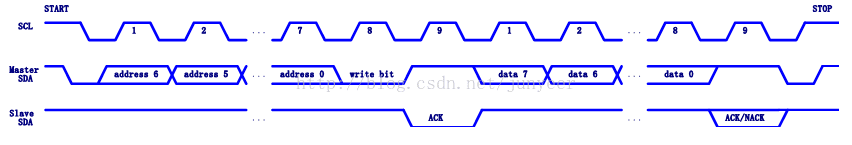

I2C匯流排以位元組為單位收發資料。傳輸到SDA線上的每個位元組必須為8位。每次傳輸的位元組數量不受限制。首先傳輸的是資料的最高位(MSB,第7位),最後傳輸的是最低位(LSB,第0位)。另外,每個位元組之後還要跟一個響應位,稱為應答。7.9 應答(Acknowledge)

在I2C匯流排傳輸資料過程中,每傳輸一個位元組,都要跟一個應答狀態位。接收器接收資料的情況可以通過應答位來告知傳送器。應答位的時鐘脈衝仍由主機產生,而應答位的資料狀態則遵循“誰接收誰產生”的原則,即總是由接收器產生應答位。主機向從機發送資料時,應答位由從機產生;主機從從機接收資料時,應答位由主機產生。I2C匯流排標準規定:應答位為0表示接收器應答(ACK),常常簡記為A;為1則表示非應答(NACK),常常簡記為A。傳送器傳送完LSB之後,應當釋放SDA線(拉高 SDA,輸出電晶體截止),以等待接收器產生應答位。如果接收器在接收完最後一個位元組的資料,或者不能再接收更多的資料時,應當產生非應答來通知傳送器。傳送器如果發現接收器產生了非應答狀態,則應當終止傳送。7.10 基本的資料傳輸格式示意圖

圖7.4 主機向從機發送資料的基本格式

圖7.5 主機從從機接收資料的基本格式

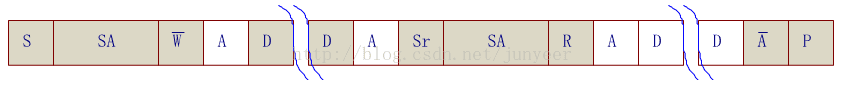

在圖 7.4 和圖 7.5 中,各種符號的意義為:

S:起始位(START);

SA:從機地址(Slave Address),7位從機地址;

W:寫標誌位(Write),1位寫標誌;

R:讀標誌位(Read),1位讀標誌;

A:應答位(Acknowlege),1位應答;

A:非應答位(Not Acknowledge) ,1位非應答;

D:資料(Data),每個資料都必須是8位;

P:停止位(STOP);

陰影:主機產生的訊號;

無陰影:從機產生的訊號。

應當注意的是,與圖7.5中的情況不同的是,在圖7.4 中,主機向從機發送最後一個位元組的資料時,從機可能應答也可能非應答,但不管怎樣主機都可以產生停止條件。如果主機在向從機發送資料(甚至包括從機地址在內)時檢測到從機非應答,則應當及時停止傳輸。

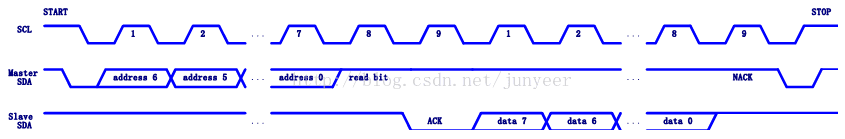

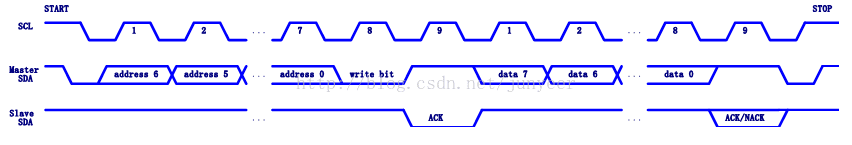

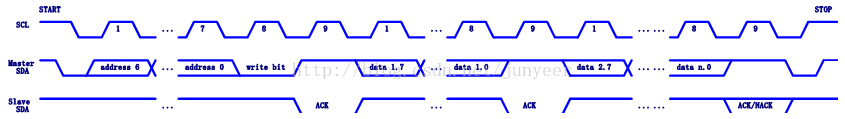

7.11 傳輸一個位元組資料的時序圖

為了更清楚地瞭解I2C 匯流排的基本資料傳輸過程,下面畫出了只傳輸1個位元組的時序圖,這是最基本的傳輸方式。在圖7.6和圖7.7中,SDA訊號線被畫成了兩個,一個是主機產生的,另一個是從機產生的。實際上主機和從機的SDA訊號線總是連線在一起的,是同一根SDA。畫成兩個SDA有助於進一步理解在I2C總線上主機和從機的不同行為。

圖7.6 主機向從機發送1位元組資料的時序圖

圖7.7 主機從從機接收1位元組資料的時序圖

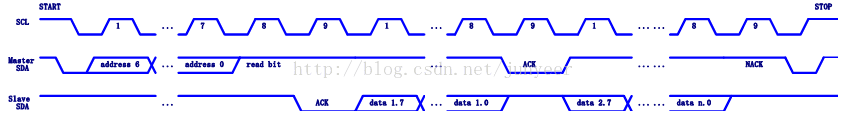

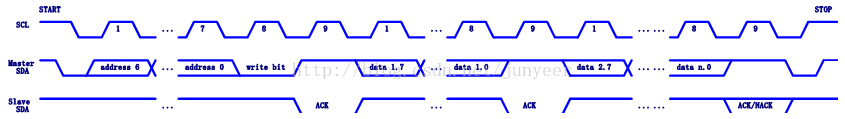

7.12 傳輸多個位元組資料的時序圖

主機連續向從機發送或從從機接收多個位元組資料的情況也很容易理解,下面直接給出相關時序圖。

圖7.8 主機向從機連續傳送多個位元組資料的時序圖

圖7.9 主機從從機連續接收多個位元組資料的時序圖

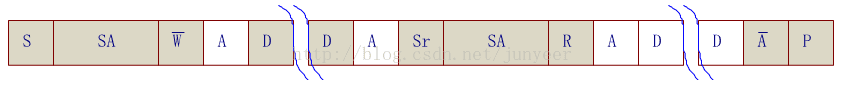

7.13 重複起始條件(Repeated START condition)

主機與從機進行通訊時,有時需要切換資料的收發方向,例如訪問某一具有I2C 匯流排介面的E2PROM儲存器時,主機先向儲存器輸入儲存單元的地址資訊(傳送資料),然後再讀取其中的儲存內容(接收資料)。在切換資料的傳輸方向時,可以不必先產生停止條件再開始下次傳輸,而是直接再一次產生開始條件。I2C匯流排在已經處於忙的狀態下,再一次直接產生起始條件的情況被稱為重複起始條件。重複起始條件常常簡記為Sr。正常的起始條件和重複起始條件在物理波形上並沒有什麼不同,區別僅僅是在邏輯方面。在進行多位元組資料傳輸過程中,只要資料的收發方向發生了切換,就要用到重複起始條件。

圖7.10 帶有重複起始條件的多位元組資料傳輸格式示意圖

圖 7.10 給出了帶有重複起始條件的多位元組資料傳輸格式示意圖,圖中的各種符號的意義與第 7.10 節中的相同。要特別注意圖中重複起始條件Sr的用法。如果讀者有興趣的話,可以自行畫出其對應的時序圖。

7.14 無子地址器件與有子地址器件

帶有I2C匯流排的器件除了有從機地址 (Slave Address)外,還可能有子地址(Sub-Address)。 從機地址是指該器件在I2C總線上被主機定址的地址,而子地址是指該器件內部不同部件或儲存單元的編址。例如,帶I2C匯流排介面的 E2PROM就是擁有子地址器件的典型代表。另外一些器件(只佔少數)內部結構比較簡單,可能沒有子地址,只有必須的從機地址。與從機地址一樣,子地址實際上也是像普通資料那樣進行傳輸的,傳輸格式仍然是與資料相統一的,區分傳輸的到底是地址還是資料要靠收發雙方具體的邏輯約定。子地址的長度必須由整數個位元組組成,可能是單位元組(8位子地址),也可能是雙位元組(16位子地址),還可能是3位元組以上,這要看具體器件的規定。在第8章的I2C匯流排軟體包中,已經同時考慮到了無子地址器件和有子地址器件的情況。