FPGA 學習筆記(十三)modelsim自動化模擬環境

阿新 • • 發佈:2019-01-31

搭建基於Modelsim的自動化模擬

我們之前通常進行Modelsim介面操作,這樣會很費時很麻煩。這裡我們介紹一種快捷的方法,通過do檔案快速搭建模擬環境,實現更高效的模擬過程。

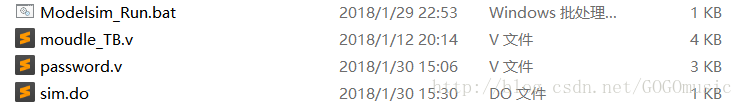

我們只需將sim.do中的程式碼寫好,然後點選一下modelsim_run.bat檔案,即可完成所有模擬過程。

批處理檔案modelsim_run.bat

只需要雙擊批處理檔案modelsim_run.bat,就可以自動呼叫Modelsim,並自動完成對Testbench和待驗證設計檔案的編譯和模擬,並且可以自動將要觀察的訊號新增到wave視窗。完全自動化!!

批處理檔案包含一條命令:

modelsim -do 這是一條DOS命令,意思就是呼叫Modelsim工具,並在Modelsim工具中執行sim.do這個檔案。

do檔案

sim.do檔案是由tcl指令碼語言編寫的

##create work library

vlib work

vlog "../src/*.v"

vsim -voptargs=+acc work.moudle_TB

# Set the window types

view wave

view structure

view signals

add wave -divider {moudle_TB}

add wave moudle_TB/*

.main clear

run 320 vlib work:建立work庫,相當於新建工程時所生成的work庫,後期我們編譯的結果資訊存放到work庫中。

vlog “../src/ * .v”:vlog相當於modelsim工具中的compile,”../src/ * .v”表示編譯/src路徑下所有的verilog檔案。

vsim -voptargs=+acc work moudle_TB :vsim表示啟動模擬功能,模擬檔案為moudle_TB 。

add wave -divider {moudle_TB} :將moudle_TB所有訊號線 劃線隔開

add wave moudle_TB/* : 將頂層檔案moudle_TB中左右的訊號線加到模擬波形視窗

.main clear :清除Transcript視窗

run 320us :執行時間320us