驅動除錯--SPI通訊深入解析

工作中除錯了高通平臺的幾個專案,解決了幾個圍繞spi的問題。結合網上資料,寫了篇spi除錯總結,希望能幫助大家。

SPI匯流排概述---SPI匯流排介面---SPI匯流排結構---SPI匯流排資料傳輸過程---SPI四種工作方式---SPI除錯案例

SPI匯流排概述

SPI全稱是序列外設介面(Serial PeripheralInterface),全雙工同步序列通訊介面。

優點:資料傳輸速率較高

缺點:沒有指定的流控制,沒有應答機制確認是否接收到資料

SPI匯流排介面

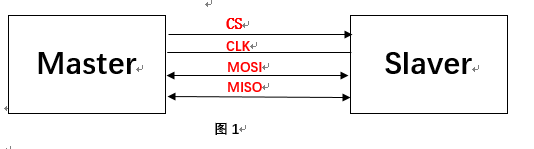

SPI匯流排只需四條線就可以完成MCU與各種外圍器件的通訊:

1)MOSI – Master資料輸出,Slave

2)MISO – Master資料輸入,Slave資料輸出

3)SCK – 時鐘訊號

4)CS – Slave使能訊號,由Master控制

SPI匯流排結構

SPI通訊採用主從模式(Master-Slave)架構,一般為一個Master和多個Slave的應用模式。SPI匯流排構成如圖所示。

SPI匯流排資料傳輸過程

SPI介面在Master控制下產生的從器件使能訊號和時鐘訊號,兩個雙向移位暫存器按位傳輸進行資料交換。傳輸資料以位元組為單位,每個位元組高位在前,低位在後(MSB first)。

在一個SPI時鐘週期內,會完成如下操作:

1)Master通過MOSI線傳送1位資料,同時Slave通過MOSI線讀取這1位資料

2)Slaver通過MISO線傳送1位資料,同時Master通過MISO線讀取這1位資料

Master和Slave各有一個移位暫存器,如圖4所示,而且這兩個移位暫存器連線成環狀。依照SCK的變化,資料以MSB first的方式依次移出Master暫存器和Slave暫存器,並且依次移入Slave暫存器和Master暫存器。當暫存器中的內容全部移出時,相當於完成了兩個暫存器內容的交換。

SPI四種工作方式

下圖是4種工作模式:(輸入指接收端取樣,輸出指傳送端輸出資料)

SPI四種工作方式本質上是區分 資料取樣的時間 和 資料輸出的時間 這兩個元素。

而這個時間區分是依靠sck訊號 ,故引出下面兩個概念。

CPOL:時鐘極性選擇,為0時SPI匯流排空閒為低電平,為1時SPI匯流排空閒為高電平

CPHA:時鐘相位選擇,為0時在SCK第一個跳變沿取樣,為1時在SCK第二個跳變沿取樣

SPI除錯案例

BUG 1

問題現象:

cpu接收到的資料均為0, 抓取spi 4個訊號波形,cs clk訊號正常,mosi資料正常,miso無資料(為低電位)

原因分析:

1.miso訊號線異常問題,故更換外設模組

2.pin腳網路連線問題,故核對引腳接線圖

分析驗證:

根據分析的1原因 ,更換幾個模組發現現象依舊,而模組是量產產品,一般不會都有問題,說明1可以忽略。

根據分析的2原因,核對原理圖 ,發現從cpu引出gpio pin網路時 ,MISO與MOSI接反了。然後飛線把順序換回來,spi通訊正常 。

解決方案:

-

硬體改版 , 修改pin網路

-

軟體互換cpu miso mosi輸出的引腳(這要看軟體是否支援)

BUG 2

問題現象:

SPI波形顯示,miso前8 bit始終為0該如何解釋?

原因分析:

因為spi工作需要先把slaver的暫存器地址傳送過去 ,且clk是同步的,故前8 bit的miso是沒有訊號的。故正常。

行文至此,東哥想多說幾句,優秀的嵌入式人要具備快速準確解決問題的能力,這不僅要知識面廣,經驗足,更需要正確的除錯思路。需要多思考,深入思考。記得關注我的部落格,常來看看。