暫存器檔案,隨機訪問儲存器讀寫理解

狀態:特徵是會保持一段時間的,不會突變。

時序(sequential ,順序)電路:預測輸出會怎麼變化,是由當前狀態和輸入決定。(時序電路的特徵和時鐘沒關係)

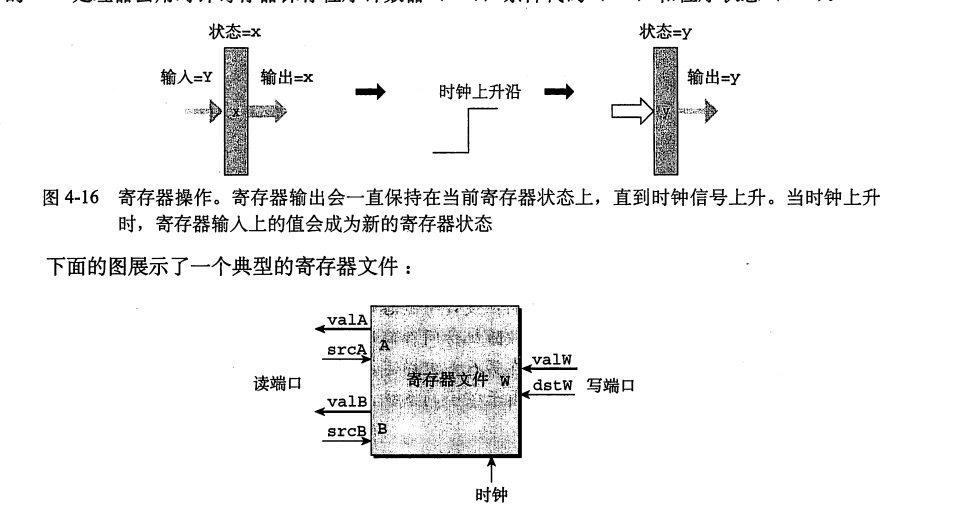

暫存器和時序邏輯什麼關係。!!!!! 通過控制邏輯(時鐘訊號與地址為輸入),控制儲存器是否接受時鐘訊號的控制,若接受,則儲存器,實際就是鍾控觸發器(在上升沿時,觸發器接受輸入)。 見下圖(指反映寫的情況)。

不是內部存在著時序電路的電路,就存在時序電路的特徵(輸出反饋到輸入,改變輸入時,輸出當前的輸出也稱為輸入一部分)。 觸發器是時序電路,隨機訪問儲存器(包括暫存器檔案)是由觸發器構成的,但是在讀取資料時,儲存器就類似於組合電路了。

暫存器——. :

特點:(1)輸出不是簡單的等於輸入的某個函式(組合電路特徵。),而是在時鐘控制下響應。 否則輸出和輸入沒關係,保持狀態(輸出)。

(2)在使能輸入0情況下,狀態保持不變,時鐘控制響應暫存器響應了,結果發現使能輸入為0,則仍然保持輸出狀態。

結論:暫存器輸出狀態的改變,需要兩個條件,1. 時鐘控制允許 2.輸入對於當前狀態對應的輸入發生改變。 3. 使能端為0。 3個條件是並的關係。

暫存器檔案實現原理(即隨機訪問儲存器實現原理): 有讀埠和寫埠,每個埠都包含資料訊號通路和地址輸入。

(1)當讀取時,地址輸入可以選取某一個暫存器,即暫存器輸出訊號電路接上了埠的輸出訊號電路,所以可以看成,讀取資料好像就是一個以地址為輸入,資料為輸出的一個組合邏輯電路塊,實際是使能作用。(實際上,地址線和資料線是匯流排,即接到了每個暫存器,所以地址線是使能線,選取某個暫存器,即某個暫存器能接受輸入)

(2)當寫過程時,資料需要儲存在暫存器的“輸出”上。 所以地址輸入選中儲存的暫存器,資料輸入訊號電路接上暫存器輸入電路,再時鐘控制允許,則寫入成功。

(3)資料儲存過程,當使能為0,暫存器不受任何輸入影響。

所以,暫存器要整合為暫存器檔案,上圖4-16還需要加入使能輸入端(即地址線),時鐘控制訊號線。

指令處理對應的數位電路過程(牽涉到記憶體讀寫,暫存器讀寫),

取指:在該週期,PC暫存器輸出( 地址),使能了儲存器PC和PC+1位元組的儲存,icode:ifun,ra:rb訊號在資料匯流排上。

譯碼:匯流排RA,RB欄位接到暫存器檔案的地址輸入(暫存器是多埠,可以同時讀寫多個暫存器),讀取是使能,不用時鐘。

執行:暫存器檔案輸出接到ALU的資料輸入,匯流排的func欄位接到ALU的控制輸入. ALU組合電路計算,輸出VALE。

訪問:

寫回:VALE訊號線接到R[rb],等到時鐘到來就能寫入

更新PC:PC+2訊號接到PC,等到時鐘到來就能寫入

這是SEQ處理器的模式,一個週期處理一條完整的指令,非流水線。