linux 中斷與異常---mips基礎(一)

阿新 • • 發佈:2019-02-04

MIPS體系結構採用的是精確異常處理模式這是什麼意思呢?下面來看從“See MIPS Run”一書中的摘錄:“In a precise-exception CPU, on anyexception we get pointed at one instruction(the exception victim). All instructions preceding theexception victim in execution sequence are complete; any work done on the victim and on anysubsequent instructions (BNN NOTE: pipeline effects) has no side effects that the software need worry about. The software that handles exceptions can ignore all the timing effects of the CPU's implementations”

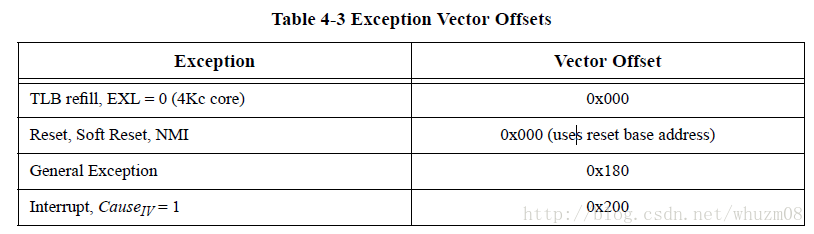

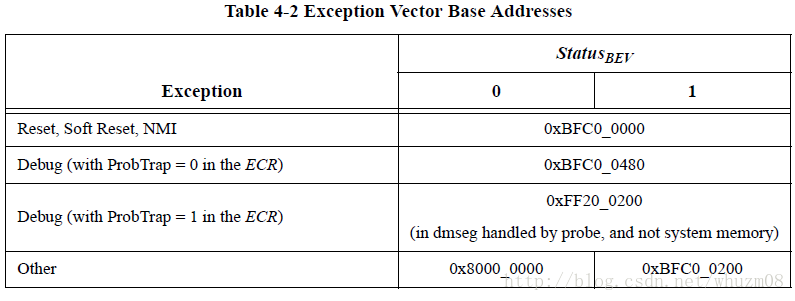

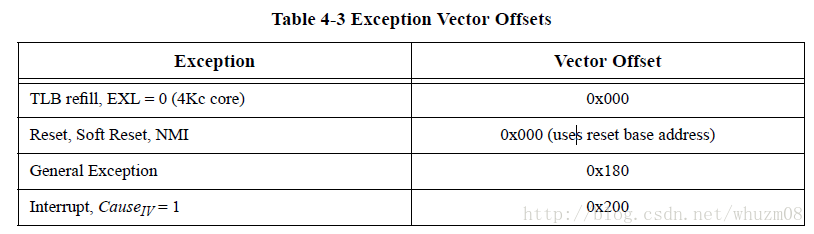

Table 4-3 gives theoffsetsfrom the base address as a function of the exception.

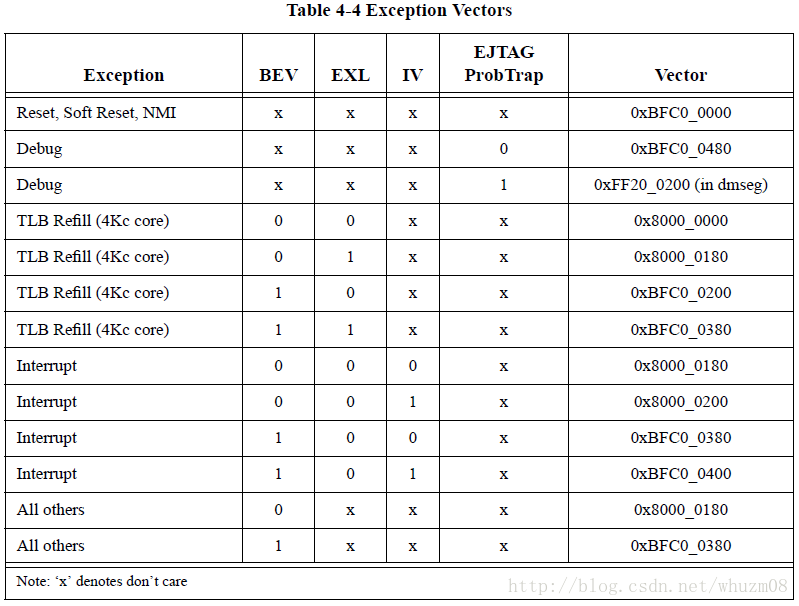

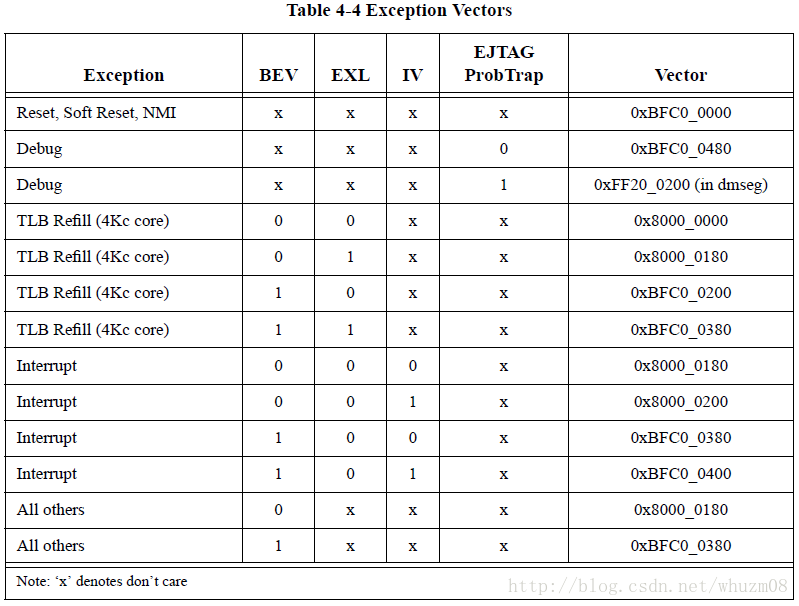

CauseIV:Setting the CP0CauseIVbit to 1 causes Interrupt exceptions to use a dedicated exception vector offset (0x200), rather than having to use the general exception vector offset (0x180).Table 4-4combines these two tables into one thatcontains all possible vector addresses as a function of the state that can affect the vector selection.

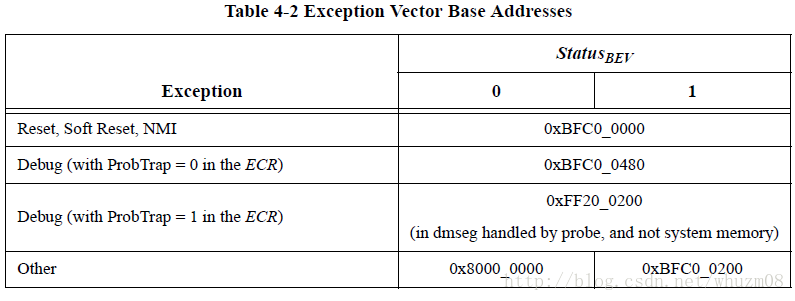

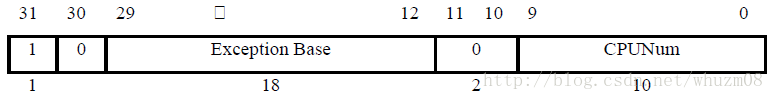

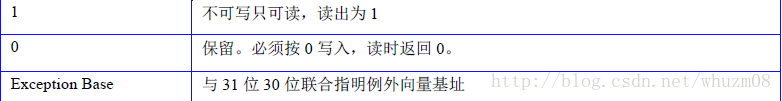

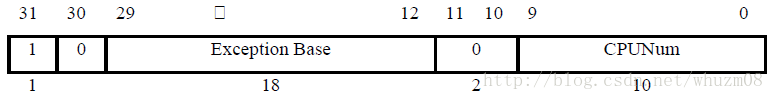

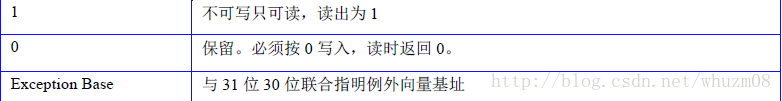

In MIPS32®Release 2 and higher architectures, software is allowed to specify the vector base address via the CP0Ebaseregister for exceptions that occur when CP0StatusBEVequals 0.

對Cache Error這個特殊的異常來說,需要給他安排一個任何時候都是Uncached的基地址了。因為發生這個異常時Cache已經不可靠了,在處理它是就不能使用它了。因此這個異常的入口基地址為: BEV = 1 : BFC0,0300 (系統啟動地址空間 : kseg1) BEV = 0 : [SP]: A000,0000 (實體記憶體地址 : kseg1) [MP]: EBASE[31.30] || 1 || EBASE[28...12] || 0x000 (實體記憶體地址 : kseg1)上面的總結一下:Reset,Soft Reset和NMI: 不受任何配置的影響,異常向量位置總是在0XBFC0_0000General Exception:異常向量在0xBFC0_0200 + 0x180 或 Ebase + 0x180Interrupt:IV 表示是否使用專用的異常處理向量, IV=0,採用General Exception中斷向量, IV=1,則採用int專用的中斷向量TLB refill:EXL為0時,採用TLB refill專用的異常處理向量,EXL為1時,採用General Exception中斷向量

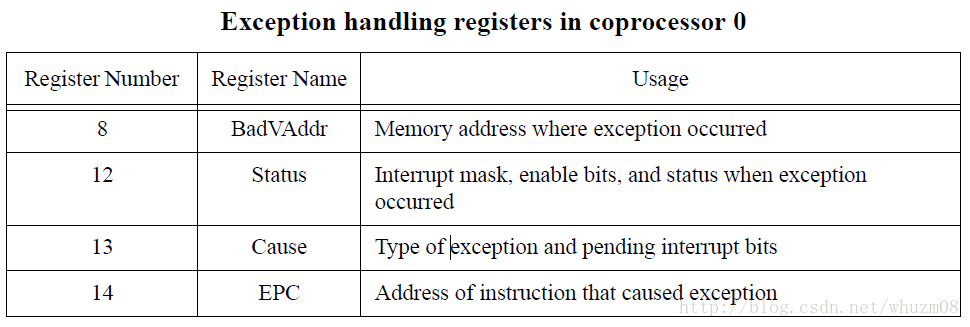

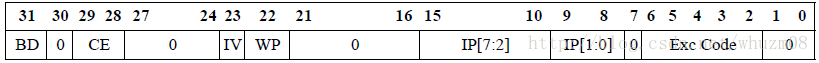

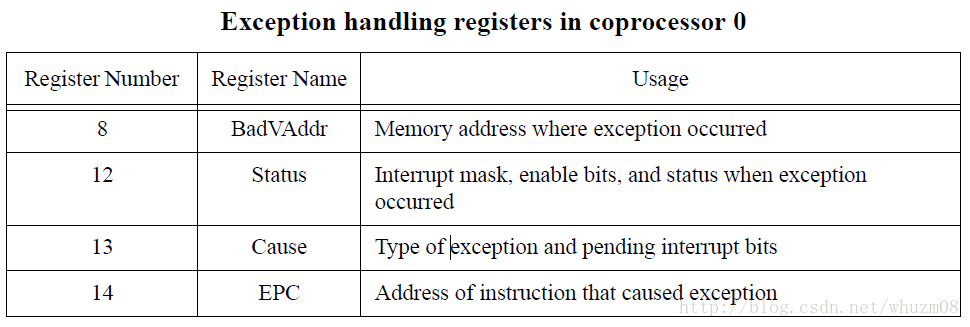

The BadVAddr registerThis register (its name stands forBad VirtualAddress) will contain the memory address where the exceptionhas occurred. An unaligned memory access, for instance, will generate an exception and the address wherethe access was attempted will be stored in BadVAddr.SR(Status Register,狀態暫存器)EXLException Level; set by the processor when any exception other than Reset, Soft Reset, NMI, or Cache Error exception are taken. 0: normal 1: exception當EXL被置位時,- 中斷是被禁止的。 換句話說,這時SR[IE]位是不管用了,相當於所有的中斷都被遮蔽了。- TLB Refill異常將會使用General Exception Vector而不是預設的TLB Refill Vector.- 如果再次發生異常,EPC將不會被自動更新。這一點要非常注意。如果想支援巢狀異 常,要在異常處理例程中清EXL位。當然要先儲存EPC的值。另外要注意的:MIPS當陷 入Exception/Interrupt時,並不改變SR[UX],SR[KX]或SR[SX]的值。SR[EXL]為1自動的 將CPU mode執行在核心模式下。這一點要注意。ERLError Level; set by the processor when Reset, Soft Reset, NMI, orCache Error exceptionare taken. 0: normal 1: error當ERL被置位時,- 中斷被禁止。- 中斷返回ERET使用的是ErrorEPC而不是EPC。需要非常注意這個區別。-Kuseg和xkuseg 被認為是沒有對映(Mapped)的和沒有快取(Un-Cached)。可以這樣理解,MIPS CPU只有在這個時刻才是一種真實模式(real mode),可以不需要TLB的對映, 就直接使用kuseg的地址空間。The ERET instruction to return from exception is used for returning fromexception level (Status.EXL) and error level (Status.ERL). If both bitsare set however we should be returning from ERL first, as ERL caninterrupt EXL, for example when an NMI is taken.都是通過eret返回的,如果EXL和ERL同時設定了,則應該首先從ERL返回,PC設定為ErrorPC,清除ERL,注意這時不會清除EXLERET指令用模擬器實現的程式碼大致如下:if (kvm_read_c0_guest_status(cop0) & ST0_ERL) { kvm_clear_c0_guest_status(cop0, ST0_ERL); vcpu->arch.pc = kvm_read_c0_guest_errorepc(cop0); } else if (kvm_read_c0_guest_status(cop0) & ST0_EXL) { kvm_clear_c0_guest_status(cop0, ST0_EXL); vcpu->arch.pc = kvm_read_c0_guest_epc(cop0);}IEInterrupt Enable 0: disable interrupts 1: enable interrupts。請記住: 當SR[EXL]或SR[ERL]被SET時, SR[IE]是無效的。BEV Normal/Bootstrap exception vectors locationSRSoft Reset,如果是soft reset,該位置1,表明是軟體復位NMI如果是NMI,該位置1,表明是不可遮蔽中斷IM[7:0]Interrupt MaskUMKernel/User Mode, UM=1使用者模式,中斷髮生時不改變該bit的值UM:ERL:EXL Mode100: User000: Kernel-10: Kernel (exception handling)-01: Kernel (error handling)Cause

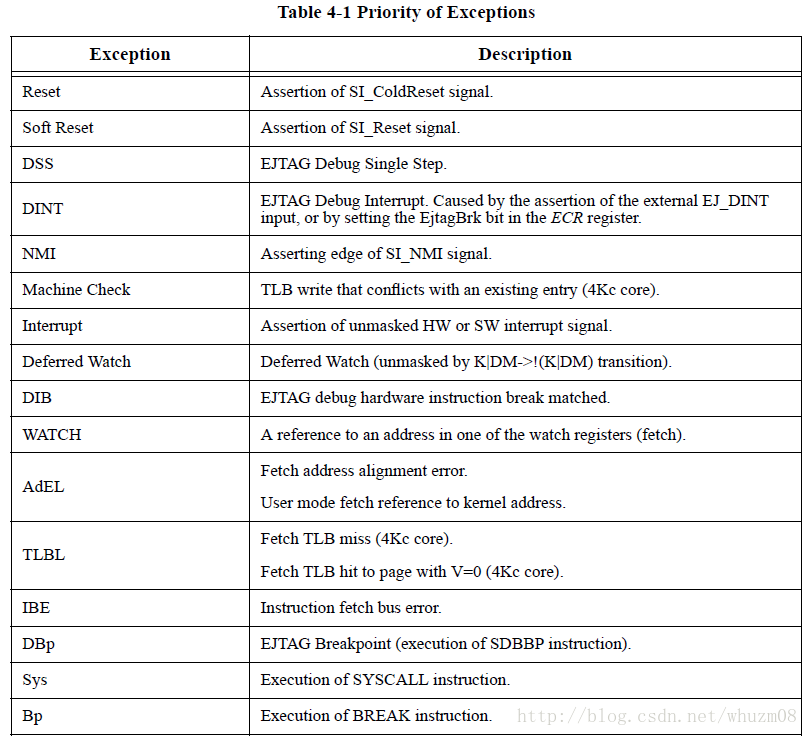

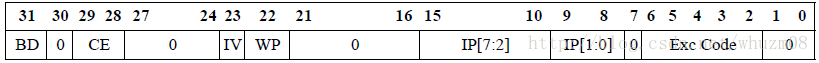

BD: Exception happened in a branch delay slotIV: Use general vs special

- 異常處理的一般過程

- 異常入口(向量)

Table 4-3 gives theoffsetsfrom the base address as a function of the exception.

CauseIV:Setting the CP0CauseIVbit to 1 causes Interrupt exceptions to use a dedicated exception vector offset (0x200), rather than having to use the general exception vector offset (0x180).Table 4-4combines these two tables into one thatcontains all possible vector addresses as a function of the state that can affect the vector selection.

In MIPS32®Release 2 and higher architectures, software is allowed to specify the vector base address via the CP0Ebaseregister for exceptions that occur when CP0StatusBEVequals 0.

- StatusBEV= 1: Exceptions vector to an uncached entry point in KSEG1: 0xBFC00xxx

- StatusBEV= 0: Exceptions vector to cached entry points in KSEG0: defined by CP0 Ebase register, plus some offset

對Cache Error這個特殊的異常來說,需要給他安排一個任何時候都是Uncached的基地址了。因為發生這個異常時Cache已經不可靠了,在處理它是就不能使用它了。因此這個異常的入口基地址為: BEV = 1 : BFC0,0300 (系統啟動地址空間 : kseg1) BEV = 0 : [SP]: A000,0000 (實體記憶體地址 : kseg1) [MP]: EBASE[31.30] || 1 || EBASE[28...12] || 0x000 (實體記憶體地址 : kseg1)上面的總結一下:Reset,Soft Reset和NMI: 不受任何配置的影響,異常向量位置總是在0XBFC0_0000General Exception:異常向量在0xBFC0_0200 + 0x180 或 Ebase + 0x180Interrupt:IV 表示是否使用專用的異常處理向量, IV=0,採用General Exception中斷向量, IV=1,則採用int專用的中斷向量TLB refill:EXL為0時,採用TLB refill專用的異常處理向量,EXL為1時,採用General Exception中斷向量

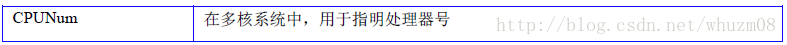

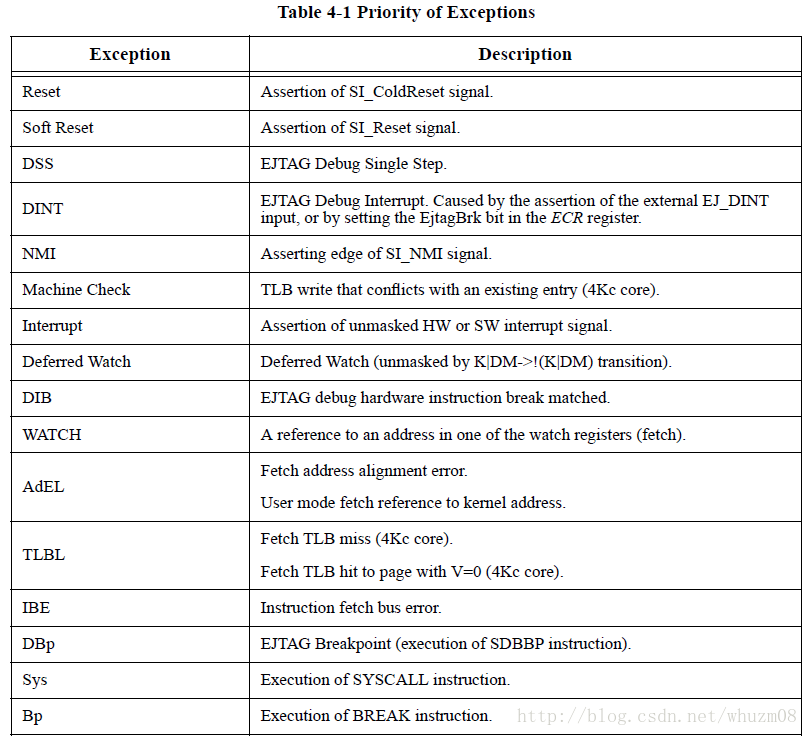

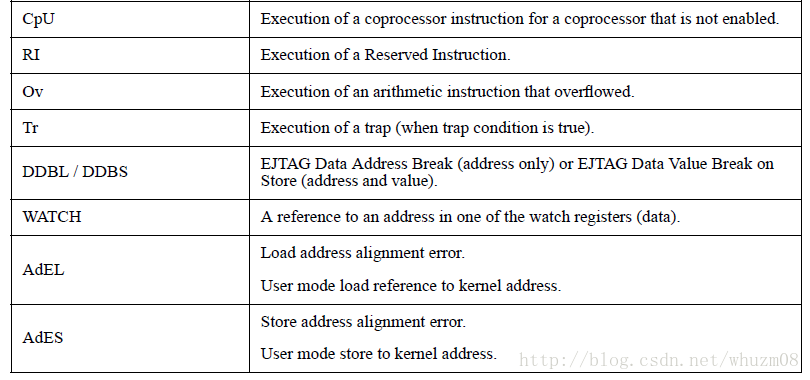

- 異常優先順序

- 異常相關暫存器

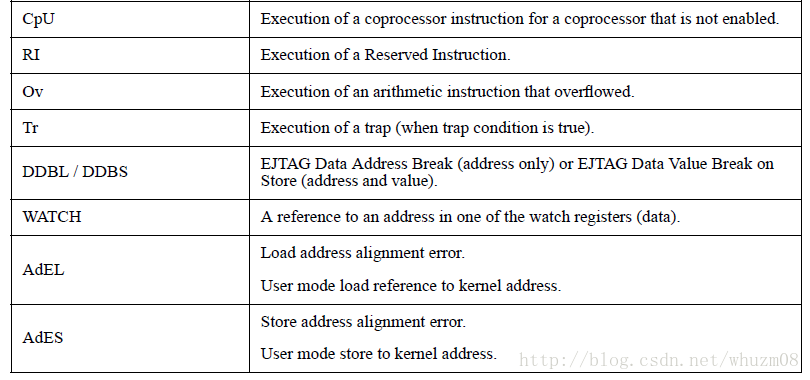

The BadVAddr registerThis register (its name stands forBad VirtualAddress) will contain the memory address where the exceptionhas occurred. An unaligned memory access, for instance, will generate an exception and the address wherethe access was attempted will be stored in BadVAddr.SR(Status Register,狀態暫存器)EXLException Level; set by the processor when any exception other than Reset, Soft Reset, NMI, or Cache Error exception are taken. 0: normal 1: exception當EXL被置位時,- 中斷是被禁止的。 換句話說,這時SR[IE]位是不管用了,相當於所有的中斷都被遮蔽了。- TLB Refill異常將會使用General Exception Vector而不是預設的TLB Refill Vector.- 如果再次發生異常,EPC將不會被自動更新。這一點要非常注意。如果想支援巢狀異 常,要在異常處理例程中清EXL位。當然要先儲存EPC的值。另外要注意的:MIPS當陷 入Exception/Interrupt時,並不改變SR[UX],SR[KX]或SR[SX]的值。SR[EXL]為1自動的 將CPU mode執行在核心模式下。這一點要注意。ERLError Level; set by the processor when Reset, Soft Reset, NMI, orCache Error exceptionare taken. 0: normal 1: error當ERL被置位時,- 中斷被禁止。- 中斷返回ERET使用的是ErrorEPC而不是EPC。需要非常注意這個區別。-Kuseg和xkuseg 被認為是沒有對映(Mapped)的和沒有快取(Un-Cached)。可以這樣理解,MIPS CPU只有在這個時刻才是一種真實模式(real mode),可以不需要TLB的對映, 就直接使用kuseg的地址空間。The ERET instruction to return from exception is used for returning fromexception level (Status.EXL) and error level (Status.ERL). If both bitsare set however we should be returning from ERL first, as ERL caninterrupt EXL, for example when an NMI is taken.都是通過eret返回的,如果EXL和ERL同時設定了,則應該首先從ERL返回,PC設定為ErrorPC,清除ERL,注意這時不會清除EXLERET指令用模擬器實現的程式碼大致如下:if (kvm_read_c0_guest_status(cop0) & ST0_ERL) { kvm_clear_c0_guest_status(cop0, ST0_ERL); vcpu->arch.pc = kvm_read_c0_guest_errorepc(cop0); } else if (kvm_read_c0_guest_status(cop0) & ST0_EXL) { kvm_clear_c0_guest_status(cop0, ST0_EXL); vcpu->arch.pc = kvm_read_c0_guest_epc(cop0);}IEInterrupt Enable 0: disable interrupts 1: enable interrupts。請記住: 當SR[EXL]或SR[ERL]被SET時, SR[IE]是無效的。BEV Normal/Bootstrap exception vectors locationSRSoft Reset,如果是soft reset,該位置1,表明是軟體復位NMI如果是NMI,該位置1,表明是不可遮蔽中斷IM[7:0]Interrupt MaskUMKernel/User Mode, UM=1使用者模式,中斷髮生時不改變該bit的值UM:ERL:EXL Mode100: User000: Kernel-10: Kernel (exception handling)-01: Kernel (error handling)Cause

BD: Exception happened in a branch delay slotIV: Use general vs special