Vivado下的整合邏輯分析儀ILA 入門

剛剛開始學習Zynq 7000的時候,看到別人問ILA的問題時,說是整合邏輯分析儀,我覺得這是一個好東西,我一定要學會它。

我是買了黑金的AX7010, 後來換成AC7010,開始學習Zynq 7000的,當然他的平臺是Vivado 2015.4 。我一步步按照黑金的教程學習,基本掌握了Zynq 7000的開發過程,但教程只是簡單提到了模擬和邏輯分析儀。所以我不斷尋找Vivado 下如何模擬以及邏輯分析儀的使用。一直不得要領,出不來。我好希望有一個教人走一遍的入門教程。經過十多天的苦苦思考和資料尋找,測試,前幾天,測試出來了Vivado 下的模擬,我就積極地和大家分享了,見我的模擬入門一文。今天我又把整合邏輯分析儀的波形調出來了,我又把他分享給大家。新鮮出爐,有些理解不一定都好,但還是足以帶你走一遍。

本文主要參考了xilinx 的ug908-vivado-programming-debugging.pdf,還有http://blog.chinaaet.com/kevinc/p/5100050249 (Vivado中使用邏輯分析儀ILA)。

原始碼和工程下載地址: 連結:http://pan.baidu.com/s/1pL4yCR5 密碼:ki9s

1: 建立工程並準備檔案

開啟Vivado, 並新建一個工程,取名dividerIla ,型別(type),選擇RTL Projecct,Default Part 根據你的硬體平臺選擇。這個一定要選擇正確,因為需要下載並執行的。我的平臺是AC7010, 選擇的是xc7z010clg400-1。

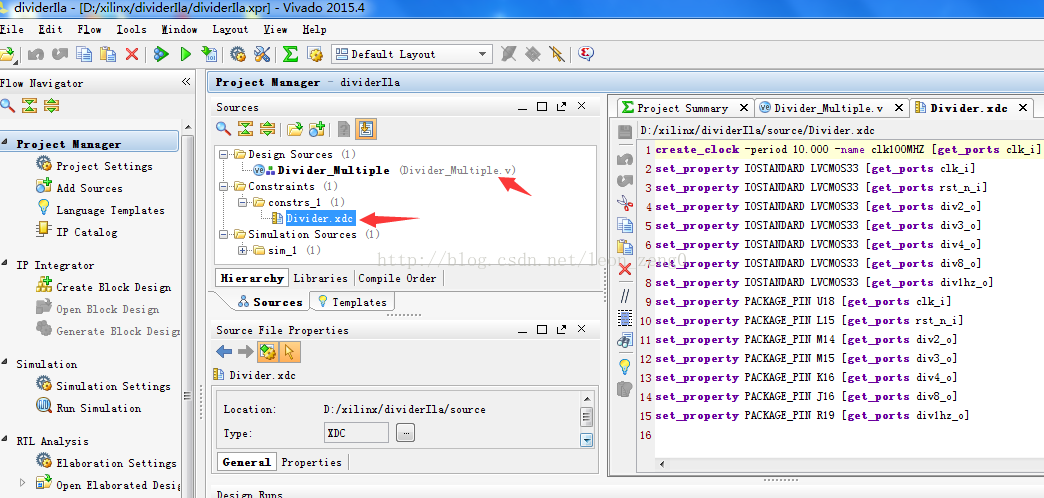

接下來是新增下載的源程式檔案:Divider_Multiple.v 到Design Sources 下, Divider.xdc 到 Constarnts下。最後的效果如下圖,其操作過程不詳述,如果操作不來,請去檢視我寫的 Vivado 下的模擬入門一文,那有詳細圖示。

這裡特別注意,如果你的硬體平臺不一樣,你需要修改Divider.xdc檔案。這裡分配硬體的管腳,需要與你的硬體一致,特別是clk_i, div1hz_o。 clk_i 是時鐘輸入腳,我的硬體是U18, div1hz_o 是led 閃燈控制,我的是R19, rst_n_i 是復位腳,我的是L15(其實沒有使用)。

在這一步的時候,如果你綜合(Synthesis), 執行(Implementation),產生位元流(Genrate Bitstream), 並下載 執行,應該看到你的一個LED 在一閃一閃的。這就是說,如果硬體平臺不一致,你就要保證程式是正確無誤的,否則,你要修改好。

如果你不想下載,這裡提供copy 程式,就是這2個程式的程式碼。

Divider_Multiple.v 程式碼:

`timescale 1ns / 1ps

module Divider_Multiple(

input clk_i,

input rst_n_i,

output div2_o,

output div3_o,

output div4_o,

output div8_o,

output div1hz_o

);

reg div2_o_r=1'b0;

[email protected](posedge clk_i)

div2_o_r=~div2_o_r;

reg [1:0]div_cnt1=2'b00;

[email protected](posedge clk_i)

div_cnt1<=div_cnt1+2'b1;

reg div4_o_r=1'b0;

reg div8_o_r=1'b0;

[email protected](posedge clk_i)

begin

if(div_cnt1==2'b00 || div_cnt1==2'b10)

div4_o_r=~div4_o_r;

else

div4_o_r=div4_o_r;

end

always @ (posedge clk_i)

begin

if((~div_cnt1[0]) && (~div_cnt1[1]))

div8_o_r=~div8_o_r;

else

div8_o_r=div8_o_r;

end

reg[1:0] pos_cnt=2'b00;

reg[1:0] neg_cnt=2'b00;

[email protected](posedge div2_o_r)

begin

if(pos_cnt==2'd2)

pos_cnt<=2'b00;

else

pos_cnt<=pos_cnt+2'b01;

end

[email protected](negedge div2_o_r)

begin

if(neg_cnt==2'd2)

neg_cnt<=2'b00;

else

neg_cnt<=neg_cnt+2'b01;

end

reg div3_o_r0;

reg div3_o_r1;

[email protected](posedge div2_o_r)

if(pos_cnt<2'd1)

div3_o_r0<=1'b1;

else

div3_o_r0<=1'b0;

[email protected](posedge div2_o_r)

if(neg_cnt<2'd1)

div3_o_r1<=1'b1;

else

div3_o_r1<=1'b0;

reg div1hz_o_r=0;

reg [25:0] div1hz_cnt=0;

always @(posedge clk_i)

if(div1hz_cnt<26'd50_000_000)

div1hz_cnt<=div1hz_cnt+1'b1;

else

div1hz_cnt<=0;

[email protected](posedge clk_i)

if(div1hz_cnt==26'd49_999_999)

div1hz_o_r<=~div1hz_o_r;

else

div1hz_o_r<=div1hz_o_r;

assign div2_o=div2_o_r;

assign div3_o=div3_o_r1;

assign div4_o=div4_o_r;

assign div8_o=div8_o_r;

assign div1hz_o=div1hz_o_r;

endmodule

Divider.XDC程式碼:

create_clock -period 10.000 -name clk100MHZ [get_ports clk_i]

set_property IOSTANDARD LVCMOS33 [get_ports clk_i]

set_property IOSTANDARD LVCMOS33 [get_ports rst_n_i]

set_property IOSTANDARD LVCMOS33 [get_ports div2_o]

set_property IOSTANDARD LVCMOS33 [get_ports div3_o]

set_property IOSTANDARD LVCMOS33 [get_ports div4_o]

set_property IOSTANDARD LVCMOS33 [get_ports div8_o]

set_property IOSTANDARD LVCMOS33 [get_ports div1hz_o]

set_property PACKAGE_PIN U18 [get_ports clk_i]

set_property PACKAGE_PIN L15 [get_ports rst_n_i]

set_property PACKAGE_PIN M14 [get_ports div2_o]

set_property PACKAGE_PIN M15 [get_ports div3_o]

set_property PACKAGE_PIN K16 [get_ports div4_o]

set_property PACKAGE_PIN J16 [get_ports div8_o]

set_property PACKAGE_PIN R19 [get_ports div1hz_o]

2 :設定除錯引數

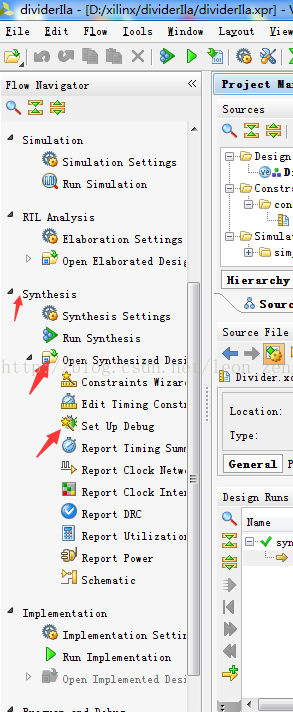

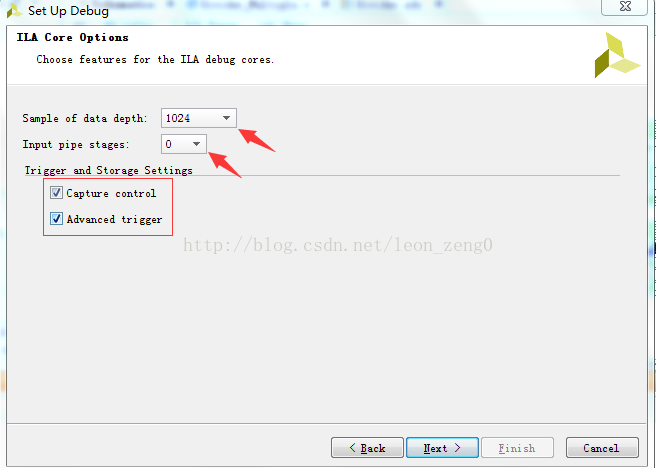

如果你還沒有綜合,那就先執行綜合(Run Synthesis),需要一點時間, 然後按下圖開啟Synthesis -> Set up Debug

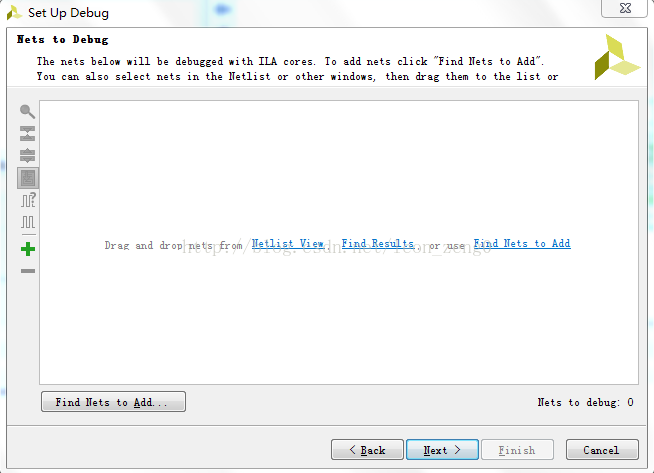

下面就是Set Up Debug 的開始對話方塊,一個網點也沒有。我們需要新增要監控或觸發條件的Net。

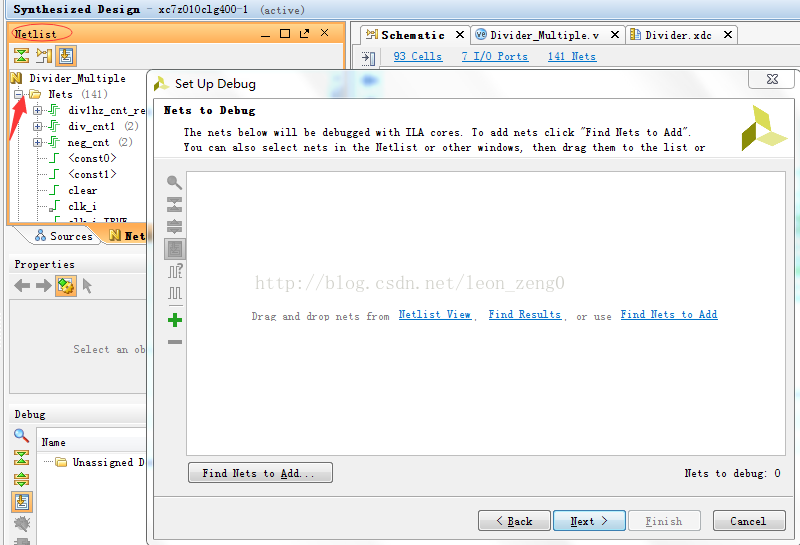

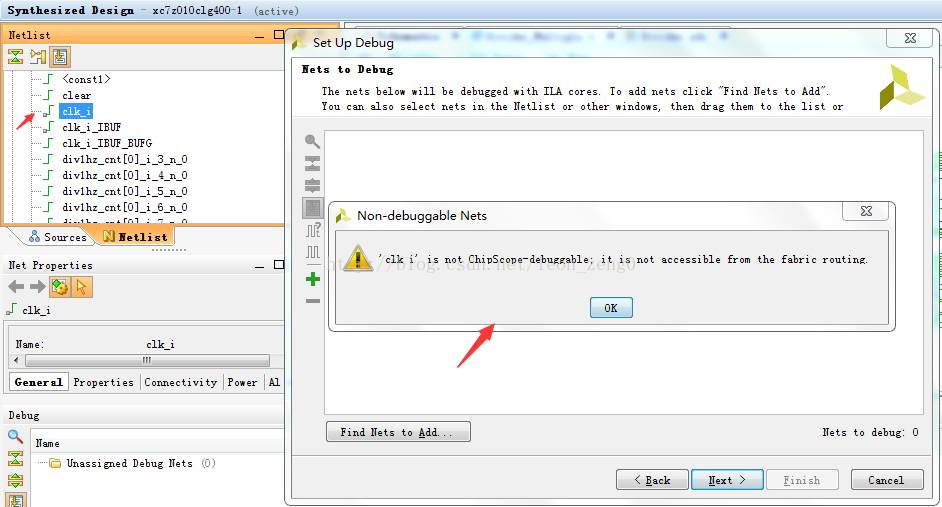

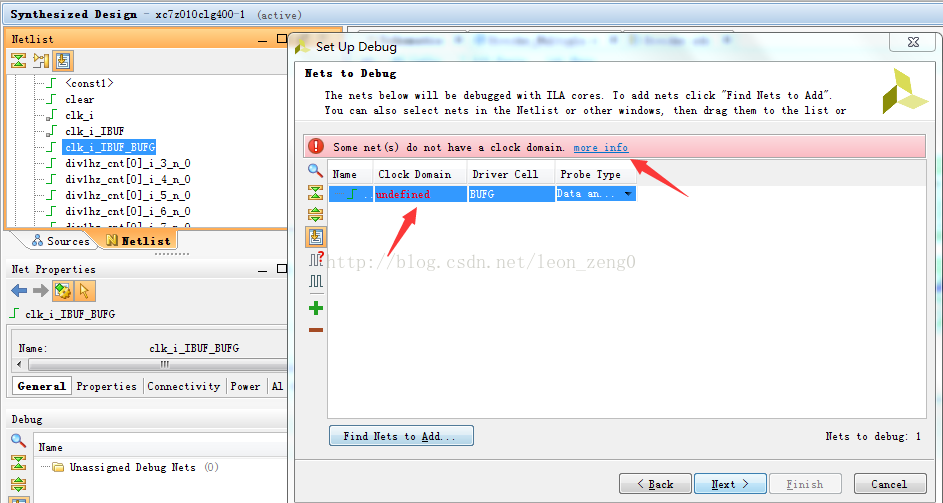

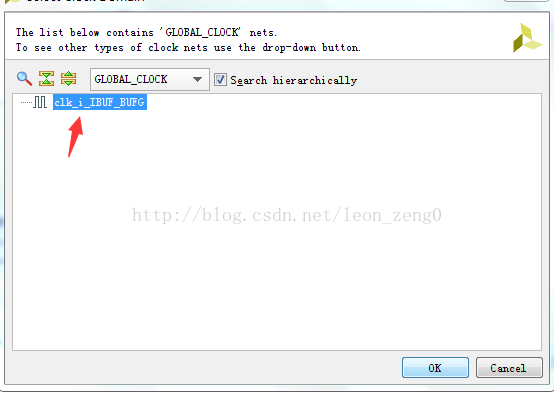

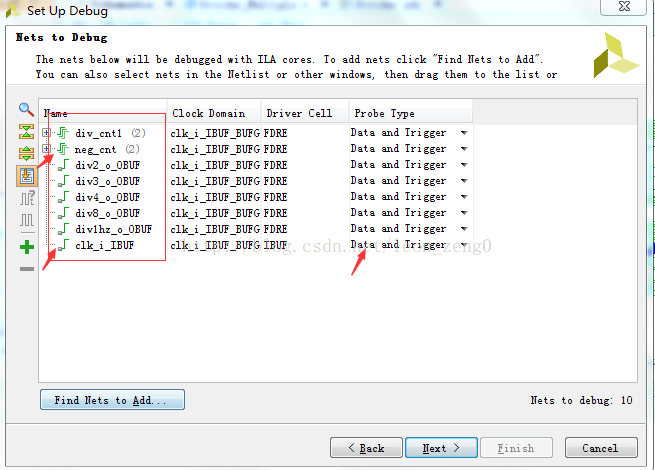

點選Netlist View:

這個時候出現了Netlist View, 點開Nets, 可以看到很多Nets ,右鍵加入或者直接拖拉

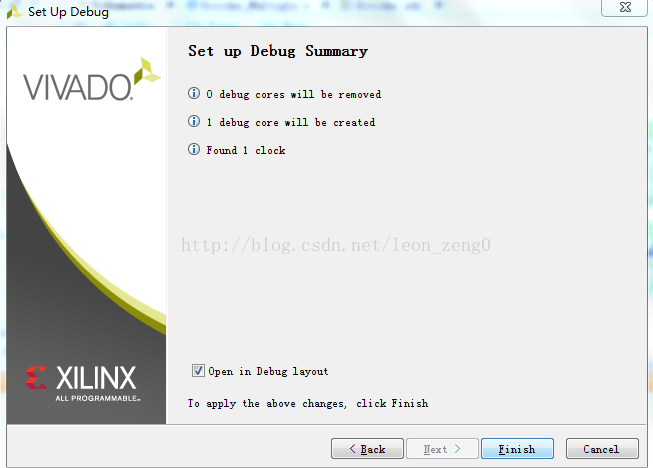

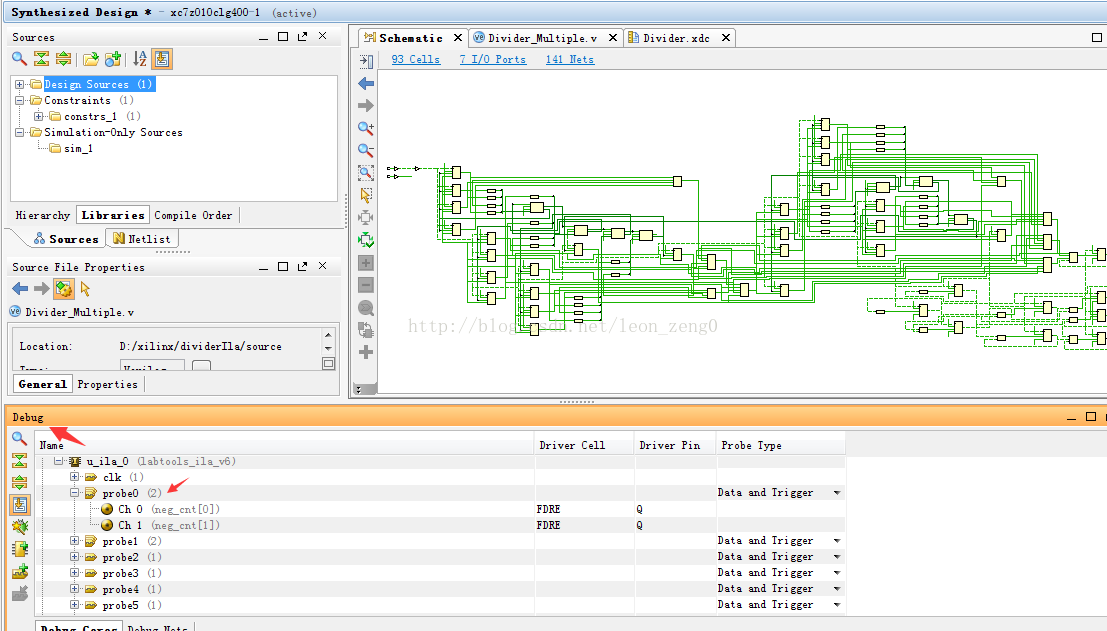

點選Finish,設定完成,出現如下檢視,可以看到Debug 視窗。

3:後續操作

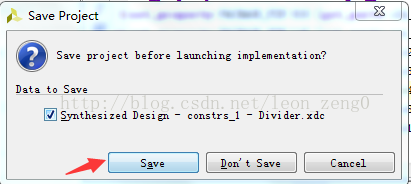

設定完成後,執行執行 (Run Implementation), 這個時候彈出一個對話方塊,我選擇Save

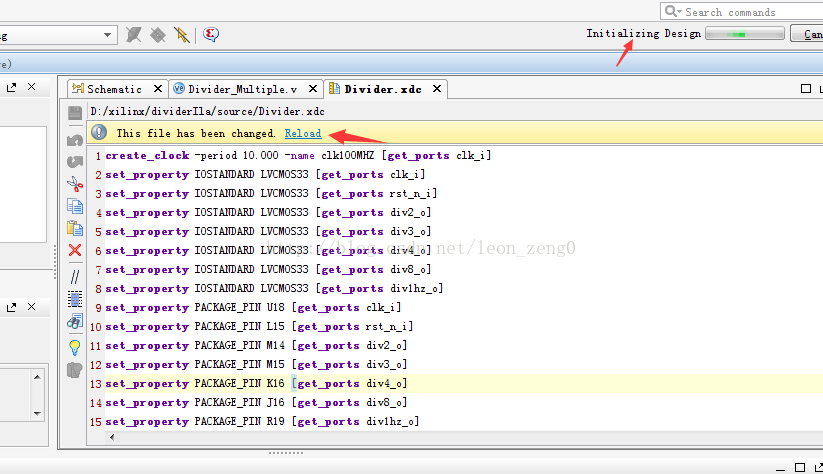

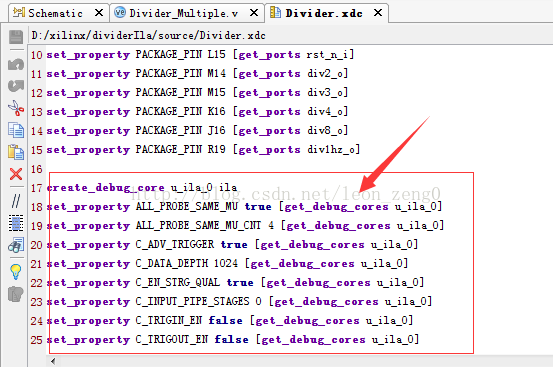

原來我們做的這些設定,就是修改Divider.XDC 檔案的內容,如下圖點選Reload:

我們看到約束檔案Divider.XDC 增加了好些內容。你能看懂嗎,ug908都有介紹,

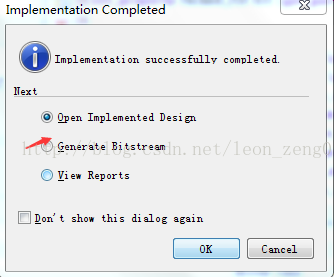

漫長的等待後,Implementation 終於結束了,這裡我選擇了紅箭頭選擇,產生位元流。

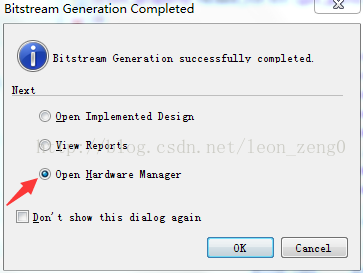

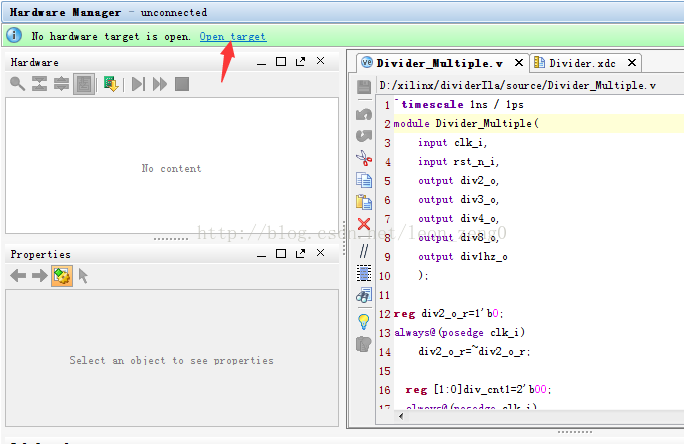

位元流也產生完了,我選擇開啟硬體管理

硬體管理的介面是這樣的, 硬體目標還沒開啟。這時要開啟你的硬體,其實我是一開始就準備好了,包括JTAG。

這是選擇紅箭 Open target

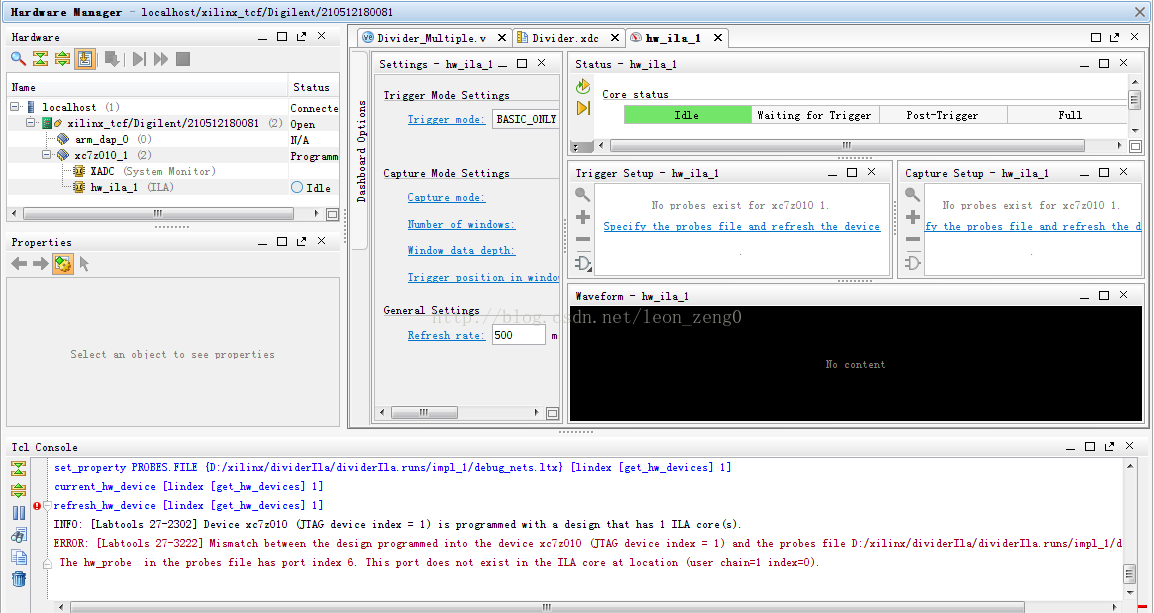

連線好目標是這樣的,下面還有錯誤提示。什麼意思,原來還沒有下載。

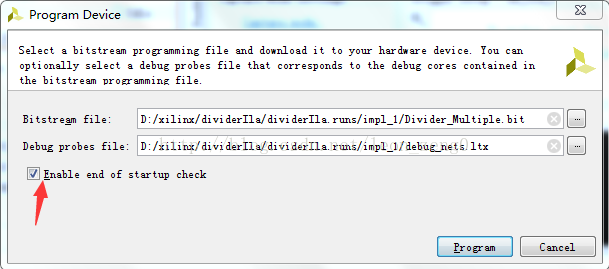

那我就下載,看上去要送2個檔案下去,我還勾上直接啟動。

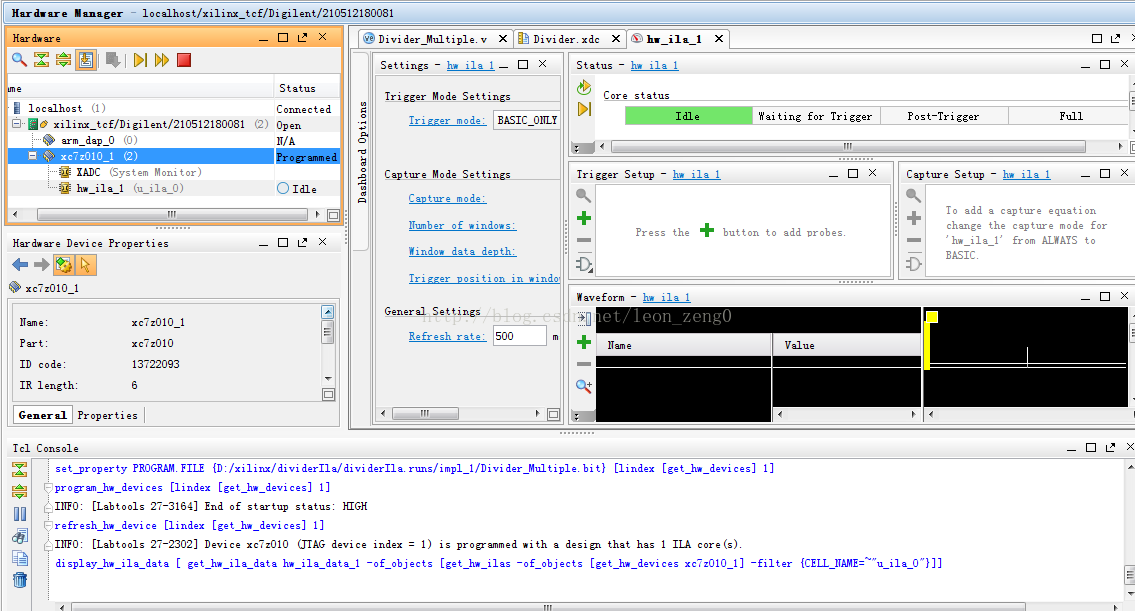

是的吧,下載後錯誤消失了。現在我們就要取樣,看波形了。

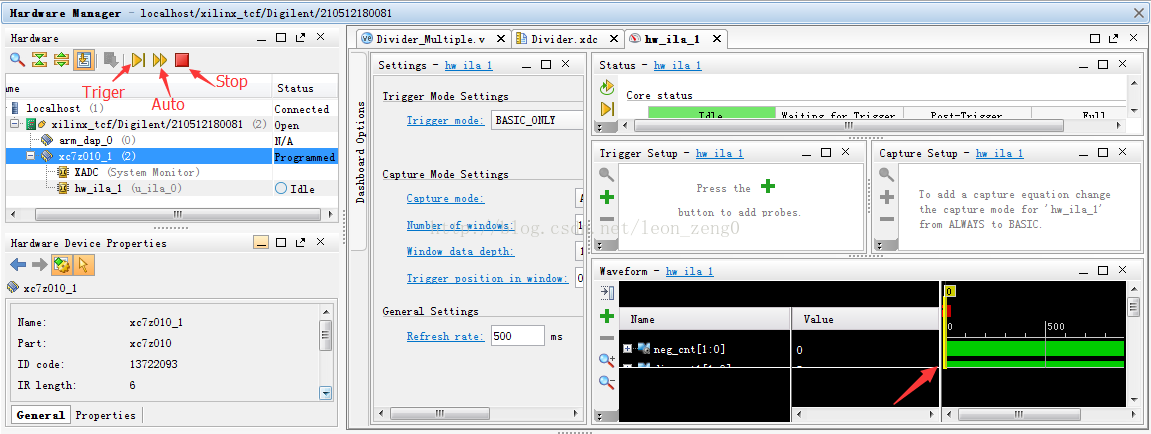

4:波形取樣和顯示控制

通過上面一連串的操作,終於到了顯示介面。左上方有3個紅箭標註的就是取樣控制操作,分別是:

Triger:觸發控制,這個要設定觸發條件,

Auto 直接觸發

Stop 停止觸發

這個就和示波器類似。

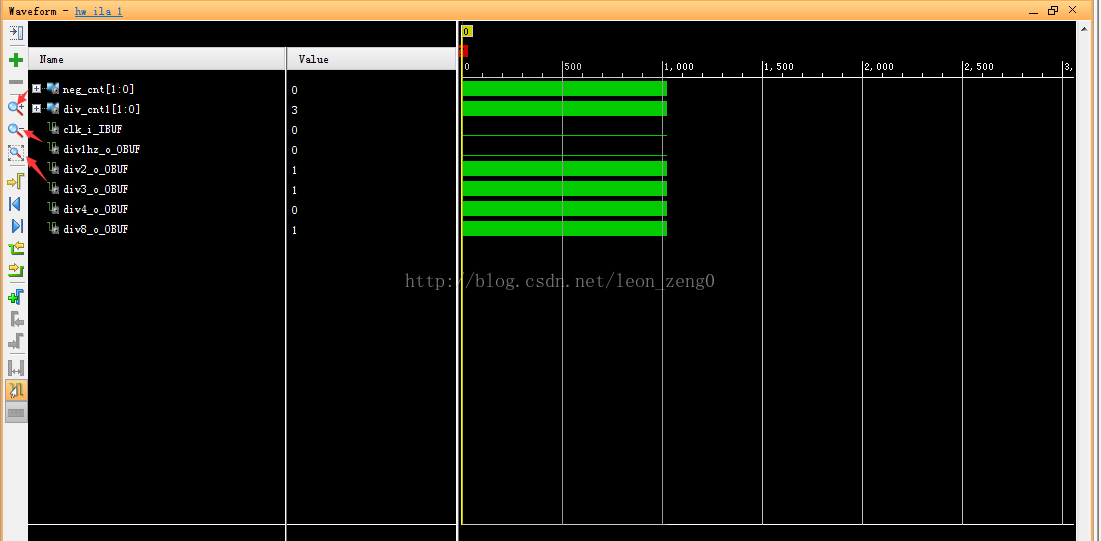

一定要觸發取樣,右邊才有密密麻麻的波形出現。

點選Wavefore 最大化,再最大化。容易看清楚一點。看看左邊3個紅箭的按鈕

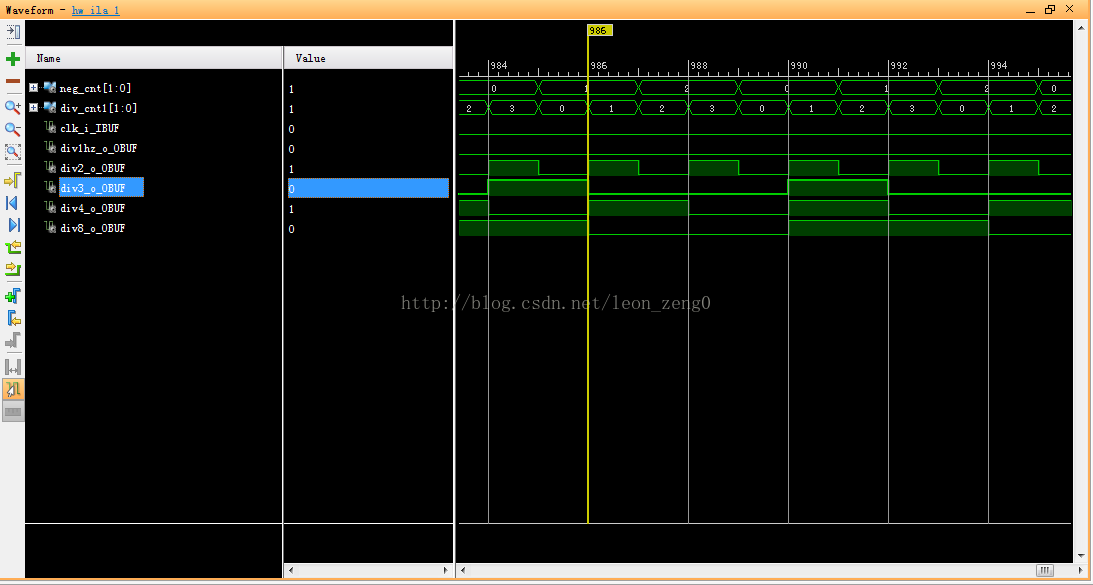

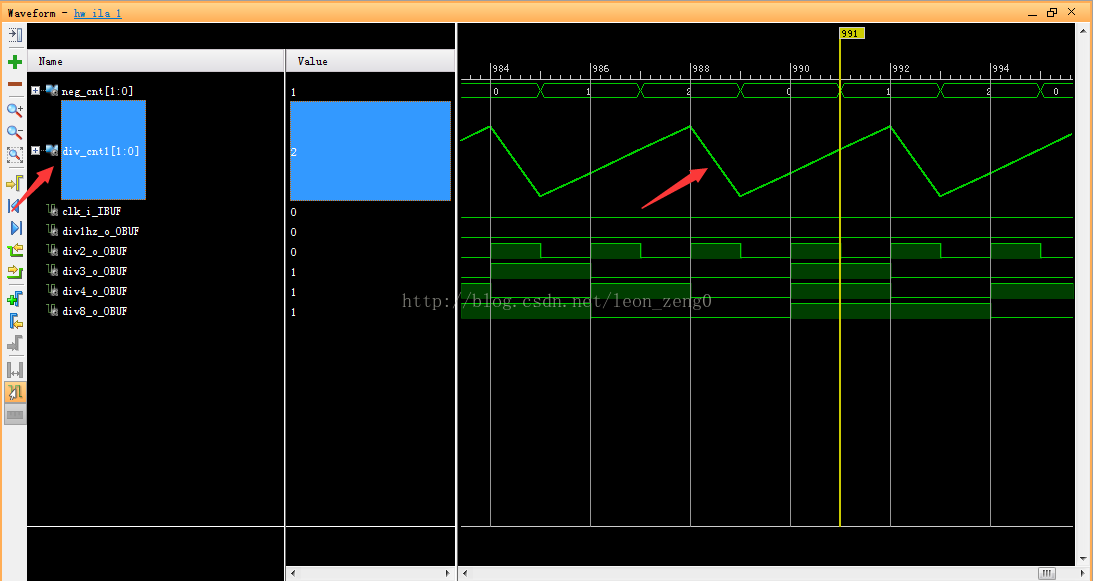

點選波形視窗左邊的按鈕,顯示全部,放大,縮小,調整到波形比較清楚一點。這就是實測的波形,我第一次看到的時候很激動。

右鍵選擇模擬方式看資料,看到模擬變化,而不是資料。

不要只是看看,動手自己做一次。右鍵一下,還有好些功能。就和大家分享到這裡,希望對你有用。

在完成本文後,又實驗了直接新增整合邏輯分析儀ILA IP核的方法,也就是入門續裡面。

相關推薦

Vivado下的整合邏輯分析儀ILA 入門

剛剛開始學習Zynq 7000的時候,看到別人問ILA的問題時,說是整合邏輯分析儀,我覺得這是一個好東西,我一定要學會它。 我是買了黑金的AX7010, 後來換成AC7010,開始學習Zynq 700

Vivado中使用邏輯分析儀ILA

FPGA綜合出來的電路都在晶片內部,基本上是沒法用示波器或者邏輯分析儀器去測量訊號的,所以xilinx等廠家就發明了內建的邏輯分析儀。在vivado中叫 ILA(Integrated Logic Analyzer),之前在ISE中是叫ChipScope。基本原理就是用fpg

Vivado使用指南之:二、如何使用VIVADO 線上邏輯分析儀

一、在想要抓取的訊號之前新增(* mark_debug = "true" *)、儲存、編譯。如:二、編譯完成之後點選set up debug。點選下一步.....直至出現如下頁面右鍵clock domain-->select clock domain,選擇抓取訊號的參考

Vivado下的模擬入門

本文通過一個簡單的例子,介紹Vivado 下的模擬過程。主要參考了miz702的教程,同時也參考了Xilinx的ug937, xapp199.。 我的軟體平臺是Vivado 2015.4, 硬體平臺是黑金的AC7010, Zynq 7000, 其實與平臺關係不大。 本文分

VIVADO下IBERT使用指南

targe art AI com detail clas nbsp .com ado https://wenku.baidu.com/view/50a12d8b9ec3d5bbfd0a74f7.html http://blog.csdn.net/wordwarwordw

Vivado下生成及燒寫MCS文件

water bits == xxx mat word arw onf art Jtag模式: 1、打開Open Hardware Manager 2、 Tools ->Auto Connect 3、TCL輸入: write_cfgmem -format MCS -si

USB虛擬邏輯分析儀,虛擬邏輯分析儀高級觸發功能詳解及圖示

ces jpg 高級 應用 shadow bcf ext ado 很多 LA2132 、32\64通道 G系列USB虛擬邏輯分析儀有很多高級觸發功能,但許多用戶用不好這些觸發功能,下面介紹這些功能的使用。 時序測量: 采集的數據作為時序顯示。 LVDS簡介 :LVDS即低壓

Unity 下整合第三方原生 SDK,以極光廠商通道為例

Unity中整合三方SDK有兩種方式: Unity 專案開發中時常有整合 Android 第三方 SDK 的需求,比如接入第三方推送,分享等功能。而第三方 SDK 的整合文件提到的往往是基於原生 Android 專案整合。 第一種 匯出 gradle 專案進行整合 匯出 gradle 專案的方式可以直接

ASP.Net MVCWebApi下整合Swagger UI(.NetCore 和.NetFramework框架)

.NetFramework框架 1. 安裝Swashbuckle v5.6.0 Nuget包(目前最新版) 2. 解決方案>屬性>生成 3. 新增配置 引入Swashbuckle包,App_Start資料夾會自動新增 SwaggerCon

SPI通訊邏輯分析儀測試總結

1 今天測試的時候發現數據很怪測試的時鐘訊號不對其他的訊號 DI 和DO也不對此時應該檢查軟體設定是否正確。 邏輯分析儀需要設定好如下幾個地方 1 取樣頻率需要提高 2 SPI通訊模式是否設定正確,因為SPI有四種通訊模式當spi通訊的時候只能選擇

手把手教你如何在Android下進行JNI開發(入門)

在進行Android開發的過程中,我們必定會遇到視訊影象處理、高強度密集運算、特殊演算法等場景,這時我們就不得不需要去接觸一些C/C++程式碼,進行JNI開發。下面我將從Android.mk和CMake這兩種方式教大家如何進行開發。文章結尾將給出演示的專案程式碼,如果你能耐心地仔細看完,相信你一定能掌握

UART學習之路(四)VerilogHDL實現的簡單UART,VIVADO下完成模擬

用VerilogHDL實現UART並完成模擬就算是對UART整個技術有了全面的理解,同時也算是Verilog入門了。整個UART分為3部分完成,傳送模組(Transmitter),接收模組(Receiver)和波特率發生模組(BuadRateGenerator)。傳送模組相比於接收模組要簡單一些,主要功能就是

ASP.Net MVCWebApi下整合Swagger UI(.NetCore & .NetFramework框架)

.NetFramework框架 1. 安裝Swashbuckle v5.6.0 Nuget包(目前最新版) 2. 解決方案>屬性>生成 3. 新增配置 引入Swashbuckle包,App_Start資料夾會自動新增 SwaggerConfig.

springboot整合elasticsearch全文檢索入門

只是簡單的整合介紹 # 安裝 # 依賴 springBootVersion = '2.0.5.RELEASE' compile group: 'org.springframework.boot', name: 'spring-boot-starter-da

Windows10下的docker安裝與入門

個人站點 :http://oldchen.iwulai.com/ 說明:本文是直接使用的Windows10的虛擬機器,不需要下載任何的工具和虛擬機器 在Windows上安裝Docker d

maven下整合SSM的檔案配置,包含mybatis外掛使用,詳細註釋版,拿來即用

spring配置檔案applicationContext.xml,放在resources下 <?xml version="1.0" encoding="UTF-8"?> <beans xmlns="http://www.springframework.org/schema/beans

Spring Boot下整合Jasypt對配置檔案進行加密

由於日趨緊張的程式碼安全問題,更多的專案需要進行簡單的加密措施。包括對資料庫連線資訊,redis連線資訊等。 本文就講解一下怎麼使用Jasypt進行簡單的配置檔案加密。 一、在maven裡新增Jasypt的依賴。 <dependency> <groupId&g

金蝶K3單據增加單據下推關聯關係(後臺調整欄位下推邏輯)

現狀:BOS裡邊銷售出庫單增加了一個單據欄位,引用的是BOS基礎資料裡邊的資料,在BOS裡邊是沒有設定單據下推攜帶關聯的地方,但是在單據自定義裡邊又選不到BOS基礎資料。 需求:增加的這個欄位需要引用

Windows10下的docker安裝與入門 (三) 建立自己的docker映象並且在容器中執行它

Docker 是一個開源的應用容器引擎,讓開發者可以打包他們的應用以及依賴包到一個可移植的容器中,然後釋出到任何流行的 Linux 機器上,也可以實現虛擬化。容器是完全使用沙箱機制,相互之間不會有任何介面。 本教程主要分以下幾點內容: ------------

maven專案中SSM+Shiro整合配置中,在有SpringMVC+MyBatis配置下整合shiro的配置步驟

最近在做SSM(SpringMVC+Shiro+MyBatis)整合的一個專案,對於shiro的配置不是特別熟練,於是想要寫下來,加深一下印象。在有SpringMVC+MyBatis配置的基礎上整合shiro: 首先進入shiro的官方網站(http