關於Verilog HDL中阻塞與非阻塞賦值形象理解

關於Verilog 中阻塞與非阻塞賦值的幾點理解

相信很多剛開始學習Verilog的童鞋對阻塞、非阻塞賦值理解得不是很明白,或者說是一頭霧水。確實,Verilog中阻塞、非阻塞一直就是一個難點,很多具備很久開發經驗的工程師仍是不得要領,在分析程式碼,看模擬時還是迷迷糊糊。我自己在學習語法的時候感覺理解了,但是在自己寫程式碼,看模擬時仍然會出現不理解的波形,所以,就從頭開始再看了遍語法。

阻塞賦值

阻塞賦值,顧名思義,即在一個always塊中,後面的語句會受到前語句的影響,具體來說,在同一個always中,一條阻塞賦值語句如果沒有執行結束,那麼該語句後面的語句就不能被執行,即被“阻塞”。也就是說always塊內的語句是一種順序關係,這裡和C語言很類似,比如,在C語言中,b= a;c=b;執行的時候就是先執行第一句b= a,然後執行下一句c=b,最後結果是a=c。同樣,在時鐘沿觸發下,always塊內,阻塞賦值是同樣順序執行,如下程式碼:

[email protected](posedge clk)

begin

b = a;

c = b;

end在時鐘上升沿來的時候,a賦給b,執行完成後,b在賦給c,整個程式碼執行完時,a=c,效果與C語言同。

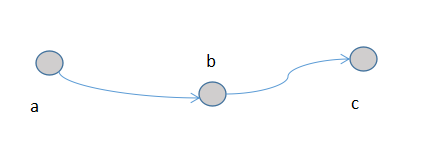

其過程下圖所示

a的值先給b,然後才能給到c,這都是在一個時鐘沿上完成的。

非阻塞賦值

在說非阻塞賦值之前,我們要先知道觸發器的工作原理。即在時鐘到來時,觸發器會將輸入端的資料打到輸出端,這是受時鐘節拍控制的。其實,非阻塞賦值更能體現出硬體電路工作時的實際情況。那麼非阻塞賦值具體是怎麼回事呢?

繼續用上面的例子:

[email protected](posedge clk)

begin

b <= a;

c <= b;

end 在時鐘上升沿到來時,該always塊就不同於阻塞賦值的最終輸出結果a=c,而是a傳遞到c需要間隔兩個時鐘,怎麼理解呢?

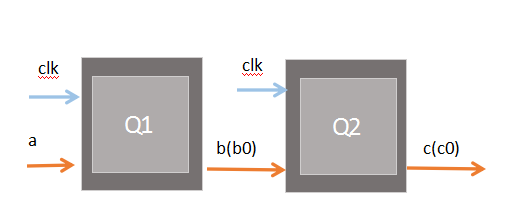

直接看圖吧

非阻塞賦值是由時鐘節拍決定,在時鐘上升到來時,執行賦值語句右邊,然後將begin-end之間的所有賦值語句同時賦值到賦值語句的左邊,注意:是begin—end之間的所有語句,一起執行,且一個時鐘只執行一次。對於上面例子,在第一個時鐘上升沿到來時,a把值賦給b,b把值賦給c,而此時b的值還沒有被更新(即a的值還沒有被觸發器打給b),只是將b0(b前一次的值)打給c,所以第一個時鐘結束後,b的當前值是a,c的當前值是b0(圖中的c0)。第二個時鐘上升沿到來時,才當前的b賦給c,由觸發器輸出,所以此時c的值才更新為a,故a和c相差2個時鐘。

若a為 1,b為0,c為1的話,那麼在非阻塞語句的always塊中,一個時鐘沿到來,由於他們之間是同時執行的,所以把a的1賦給了b,把b的0賦給了c,但是在阻塞語句裡面,a的1先給了b,然後b把新賦值的1又給了c,那麼c在一個時鐘之後即變成了1。

通過上面的描述,阻塞、非阻塞賦值應該有了比較清晰的瞭解,但是什麼時候用阻塞,什麼時候用非阻塞賦值呢?在同一個always塊中是否可以混合賦值呢?

對於第一個問題,夏宇聞老師書中直接給出了建議:

1、時序邏輯,使用“非阻塞賦值”。

2、 鎖存器(latch)建模,使用“非阻塞賦值”。

3、組合邏輯,使用“阻塞賦值”

4、 當在同一個always塊裡面既為組合邏輯又為時序邏輯時,使用“非阻塞賦值”。

5、組合邏輯輸出時,為消除毛刺會在輸出端加一個觸發器,即使用非阻塞賦值

對於第二個問題,不建議在同一個always塊中使用混合賦值,在quartusII 中直接會報錯,綜合無法通過。同時同一個變數也不能在多個always塊中被賦值,會報錯。

相關推薦

關於Verilog HDL中阻塞與非阻塞賦值形象理解

關於Verilog 中阻塞與非阻塞賦值的幾點理解 相信很多剛開始學習Verilog的童鞋對阻塞、非阻塞賦值理解得不是很明白,或者說是一頭霧水。確實,Verilog中阻塞、非阻塞一直就是一個難點,很多具備很久開發經驗的工程師仍是不得要領,在分析程式碼,看模擬時還

關於veriolg中阻塞與非阻塞賦值問題

觸發 改變 希望 到來 決定 工作 執行 為什麽 個人 在一開始學到阻塞和非阻塞的時候,所被告知的兩者的區別就在於阻塞是串行的,非阻塞是並行的。但是雖然知道這個不同點,有些時候還是很難真正區分用兩者電路的區別,在這就通過幾個例子來解釋一下。 以一個簡單的串行流水線寄存器為例

關於verilog裡阻塞與非阻塞賦值的個人理解

最近在做數字的東西,因此一直在學習verilog的語法,看的是夏宇聞老師的《verilog數字系統設計教程》這本書,在看到第14章深入理解阻塞與非阻塞賦值的不同時,結合書後面的誓言RISC_CPU,關於時序問題,產生了一些疑問,因此寫了一個簡單的程式,探索一

Socket編程中,阻塞與非阻塞的區別

軟件 復用 優點 調用 服務器 運用 需要 默認 con 阻塞:一般的I/O操作可以在新建的流中運用.在服務器回應前它等待客戶端發送一個空白的行.當會話結束時,服務器關閉流和客戶端socket.如果在隊列中沒有請示將會出現什麽情況呢?那個方法將會等待一個的到來.這個行為

網路程式設計中阻塞與非阻塞、同步與非同步、I/O模型的理解

1. 概念理解 在進行網路程式設計時,我們常常見到同步(Sync)/非同步(Async),阻塞(Block)/非阻塞(Unblock)四種呼叫方式:同步:所謂同步,就是在發出一個功能呼叫時,在沒有得到結果之前,該呼叫就不返回。也就是必須一件一件事做,等前一件做完了才能做下一件事。 例如

Linux裝置驅動中的阻塞與非阻塞I/O

阻塞和非阻塞I/O是裝置訪問的兩種不同模式,驅動程式可以靈活的支援使用者空間對裝置的這兩種訪問方式 本例子講述了這兩者的區別 並實現I/O的等待佇列機制, 並進行了使用者空間的驗證 基本概念: 1> 阻塞操作 是指 在執行裝置操作時,若不能獲得資源,則掛起程

linux裝置中的阻塞與非阻塞io

1:阻塞與非阻塞io 阻塞操作:執行裝置操作時若不能獲得資源則掛起程序(程序進入休眠狀態,將cpu資源讓給其他程序),知道滿足條件後在執行!喚醒睡眠的程序的地方最大可能發生在中斷中,因為硬體資源的獲得一般伴隨著一箇中斷。 非阻塞:程序不能進行裝置操作時並不掛起,它或者放棄,

linux裝置驅動中的阻塞與非阻塞(一)

以上是驅動中的讀取和寫入操作,當寫程序發現數據已滿,不能寫入時,且上層應用是以阻塞的方式開啟裝置檔案時,所以必須要寫入資料才能返回,否則不能返回,那麼就有兩種實現機制,要不就是不停地忙等待,等待裝置可以寫入時,便寫入,然後返回,可是這樣做的話,非常影響CPU的執行效率,大大降低了CPU的效能,所以linux核

Linux 裝置驅動中的阻塞與非阻塞I/O

何謂阻塞與非阻塞I/O?簡單來說就是對I/O操作的兩種不同的方式。 阻塞:當操作I/O裝置時,如果不能得到相應的資源,則該程序進入休眠狀態,被從排程器的佇列中移走,直到等待的條件滿足。 阻塞的讀取一個字元: char buf; fd = open("/dev/ttyS

Verilog堵塞賦值與非堵塞賦值

解決 ont mark con 原理 inpu 特點 全部 cal verilog設計進階 時間:2014年5月6日星期二 主要收獲: 1.堵塞賦值與非堵塞賦值; 2.代碼測試; 3.組合邏輯電路和時序邏輯電路。

同步與異步、阻塞與非阻塞

阻塞與非阻塞 就會 結束 檢查 通信機制 得到 node 分布 好書 “阻塞”與"非阻塞"與"同步"與“異步"不能簡單的從字面理解,提供一個從分布式系統角度的回答。1.同步與異步同步和異步關註的是消息通信機制 (synchronous communication/ a

阻塞與非阻塞,同步與異步

通過 部件 一個 socket 沒有 事件觸發 sel syn 就會 在進行網絡編程時,我們常常見到同步(Sync)/異步(Async),阻塞(Block)/非阻塞(Unblock)四種調用方式:同步: 所謂同步,就是在發出一個功能調用時,在沒有得到結果之前,

同步與異步,阻塞與非阻塞

消息 阻塞 結果 阻塞與非阻塞 過程調用 函數 異步 非阻塞 完成 異步的概念和同步相對。當一個同步調用發出後,調用者要一直等待返回消息(結果)通知後,才能進行後續的執行;當一個異步過程調用發出後,調用者不能立刻得到返回消息(結果)。實際處理這個調用的部件在完成後,通過狀態

轉:聊聊同步、異步、阻塞與非阻塞

AI strong 什麽 商業 同步與異步 好的 等待 不難 兩個 轉載:https://www.jianshu.com/p/aed6067eeac9 近來遇到了一些常見的概念,尤其是網絡編程方面的概念,如:阻塞、非阻塞、異步I/O等等,對於這些概念自己也沒有太清晰的認

關於flock文件鎖的阻塞與非阻塞

open bsp 等待 fopen pan ech 直接 else 阻塞與非阻塞 阻塞模式,程序會一直等待。 <?php $fp = fopen("lock.txt", "r"); if(flock($fp,LOCK_EX)) { //code flock($fp,

Java 同步與異步-阻塞與非阻塞理解

blog markdown logs 任務 一段 mar 慢操作 兩個 需要 Java 同步與異步-阻塞與非阻塞理解 Java 中同步與異步,阻塞與非阻塞都是用來形容交互方式,區別在於它們描述的是交互的兩個不同層面。 同步與異步 同步與異步更關註交互雙方是否可以同時工作。以

socket阻塞與非阻塞 同步與非同步 I/O模型

分享一下我老師大神的人工智慧教程!零基礎,通俗易懂!http://blog.csdn.net/jiangjunshow 也歡迎大家轉載本篇文章。分享知識,造福人民,實現我們中華民族偉大復興!

socket阻塞與非阻塞,同步與非同步、I/O模型(轉載只為查閱方便,若有侵權,立刪)

socket阻塞與非阻塞,同步與非同步 作者:huangguisu 1. 概念理解 在進行網路程式設計時,我們常常見到同步(Sync)/非同步(Async),阻塞(Block)/非阻塞(Unbl

redux-saga generator巢狀執行的阻塞與非阻塞

1.generator呼叫generator 在one中yield另一個generatoranother function*another(params){ // ... } function*one(params,{ call, put }){ // ...

圖解阻塞與非阻塞&同步與非同步

一、阻塞I/O模型 二、非阻塞I/O模型 三、非同步I/O模型 四、同步I/O模型