復位電路設計問題

阿新 • • 發佈:2019-02-06

前言

最近看advanced fpga 以及fpga設計實戰演練中有講到復位電路的設計,才知道復位電路有這麼多的門道,而不是簡單的外界訊號輸入系統復位。

流程:

1.同步復位:

優點:同步的典型優點是確保電路100%是同步電路;容易被STA;當作用於一些基於週期機制的功能模組時更易於模擬。

缺點:脈衝寬度滿足一定的要求。總是需要一個時鐘來完成對電路的復位。

程式碼:一個4bit的計數器。

1 always @(posedge clk /*or negedge sys_rst_n*/) begin 2 if (~sys_rst_n) begin 3 count <= 0;4 end //if 5 else begin 6 count <= count + 1'b1; 7 end //else 8 end //always

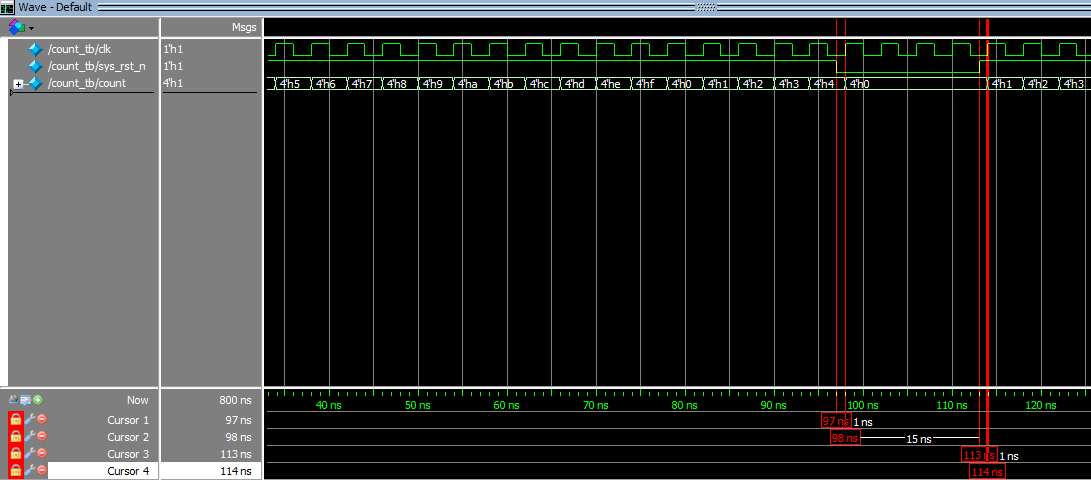

模擬解析(下圖):

時鐘上升沿如果復位訊號為低電平,復位開始,時鐘上升沿若復位訊號為高電平,復位結束。

2.非同步復位:

優點:沒有像同步復位那樣插入到資料路徑中;復位即刻生效。

缺點:復位訊號被釋放時可能出現亞穩態;對噪聲的易感染性,可能導致虛假復位。

程式碼:

1 always @(posedge clk or negedge sys_rst_n) begin 2 if (~sys_rst_n) begin3 count <= 0; 4 end //if 5 else begin 6 count <= count + 1'b1; 7 end //else 8 end //always

模擬解析(下圖):

復位訊號低電平時候,系統立刻進入復位態;

3.非同步復位同步釋放:(推薦使用)

優點:結合了同步復位與非同步復位的優點。

缺點:容易受到噪聲與宰脈衝的干擾。如果可能,最好對輸入到fpga的非同步復位訊號先進行濾波與去抖動。

程式碼:

1 module rstn_as ( 2 //input; 3 inputwire clk, 4 input wire sys_rst_n, 5 //output; 6 output reg rst_n 7 ); 8 reg rst_n_reg; 9 always @(posedge clk or negedge sys_rst_n) begin 10 if (~sys_rst_n) begin 11 rst_n <= 1'b0; 12 rst_n_reg <= 1'b0; 13 end //if 14 else begin 15 rst_n_reg <= 1'b1; 16 rst_n <= rst_n_reg; 17 end //else 18 end //always 19 20 endmodule

wire rst_n; rstn_as u1( .clk (clk), .sys_rst_n (sys_rst_n), .rst_n (rst_n) ); always @(posedge clk or negedge rst_n) begin if (~rst_n) begin count <= 0; end //if else begin count <= count + 1'b1; end //else end //always

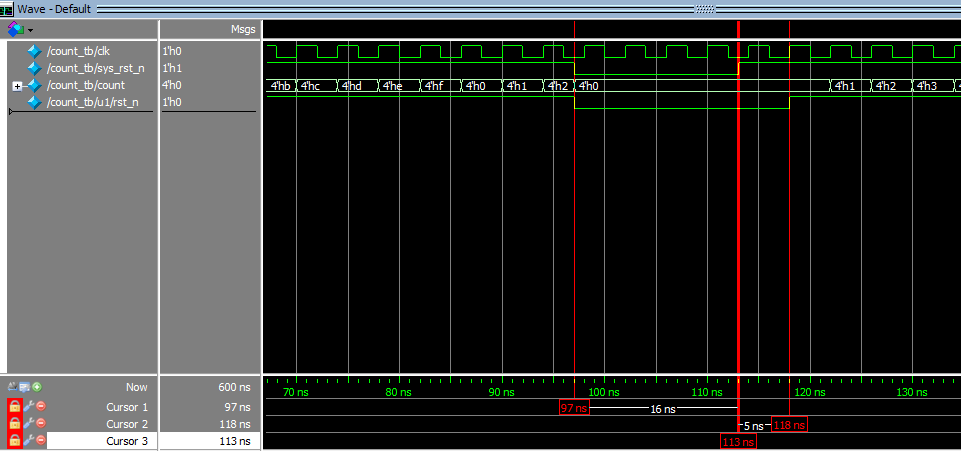

模擬解析(下圖):

當復位訊號低電平時,系統立即復位;當時鐘上升沿檢測到復位訊號失效後,在下一個時鐘上升沿拉高rst_n。新的rst_n是已經同步化了的復位訊號。

以上。