Cadence 16.6基本操作技巧(持續更新)

都是工作上碰到的需要學習的知識,比較實用。

1、修改Pin腳網路

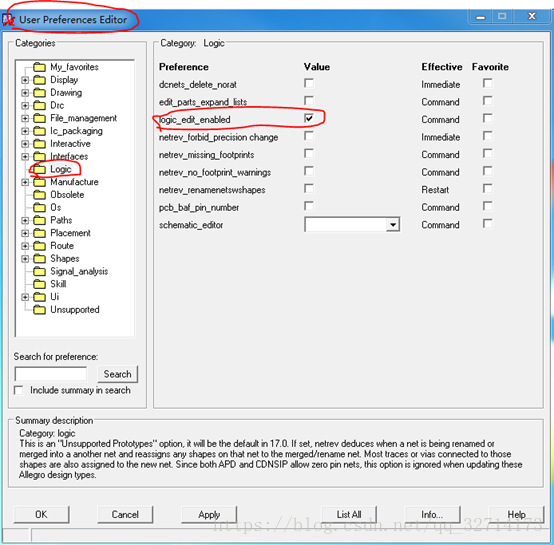

set up --user preference Editor

Logic--net logic

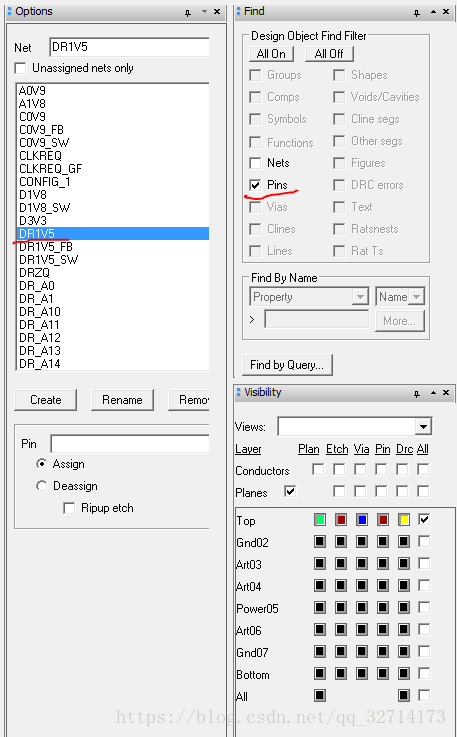

Option處選擇網路,然後find處選擇Pins,之後點選要修改網路的Pin即可將原來的網路修改為所選擇的網路。

2、在使用測量工具的時候,在Find處選擇物件就一定會吸附到該物件中心,否則就可以選擇任意位置。

3、交換兩個器件的位置

Place--Swap--Components

4、走線的模式

在走線狀態下,option狀態列下的bubble選項:

off--走線的時候基本使用這種模式。

hug only 推擠走線的時候只是hug不會移動走線。

shove preferred推擠走線的時候會移動已經走好的線,不推薦這種模式。

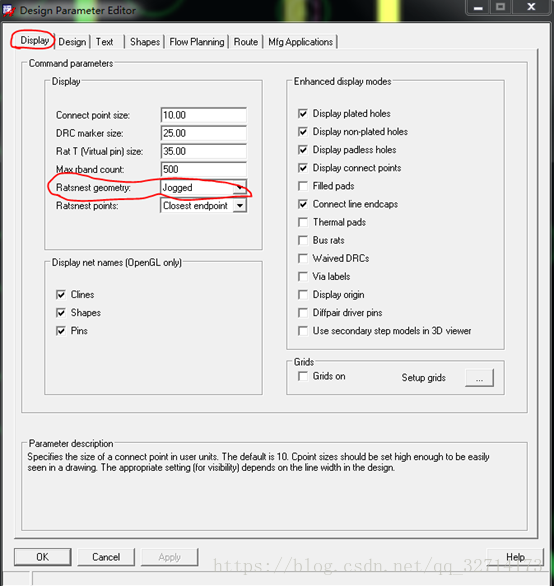

5、改變飛線佈線模式

有jogged和straight模式。

Jogged:當飛仙呈水平或者垂直時自動顯示有拐角的線段。

Straight:最短的直線段。

(因為之前用的AD所以一直習慣直線段的飛線模式,但是後來習慣之後還是覺得jogged的模式更合理。)

6、內電層敷銅

疊層設定好之後,該層是沒有銅皮的,需要自己敷。(AD是設定完疊層就有了)

先畫一塊在route keepin層的銅皮,這相當於設定了可以佈線的區域,之後畫的銅皮都會在這個框裡面,當然走線也不能超出這個框。

具體流程:

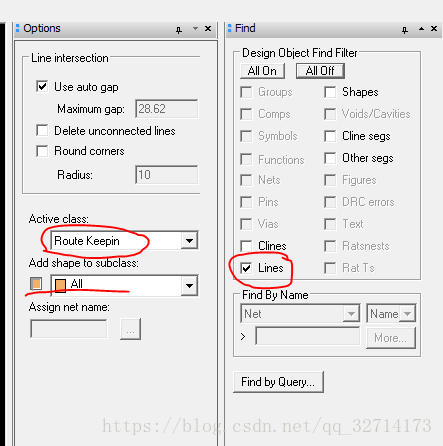

a、只打開board outline層

b、shape --compose shape,options和find處設定如下圖設定完之後直接畫一個大於outline層的框即可。

Find處只需要選擇line,不需要選擇其他。

有時候你框選了但是route keepin的shape沒有出來。是因為你的outline處於fix狀態,解鎖之後就可以了。

c、選擇外框,右鍵選擇expand/contract,需要縮排20mil。

d、之後設定層數和網路直接鋪一整塊銅皮即可。銅皮基本選擇dynamic模式。

7、繞T型等長

A、開啟CM進行如下設定

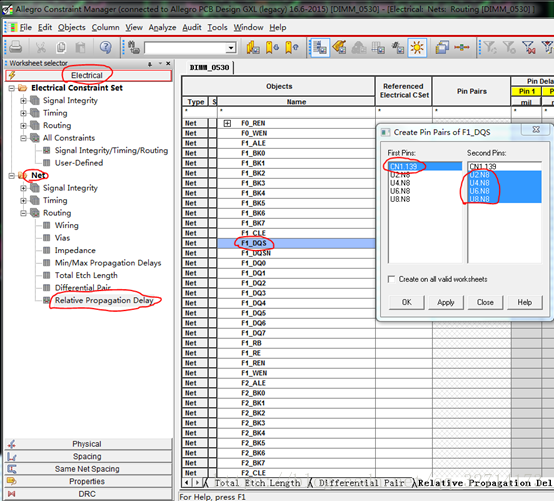

選擇F1_DQS,右鍵creat-pin pair,則出現右邊的選項框。First pin可以理解為源端,second可以理解為負載端,在T形網路中, 一個源端最多可以對應四個負載端,等長即從源端到每個負載端的長度一樣。

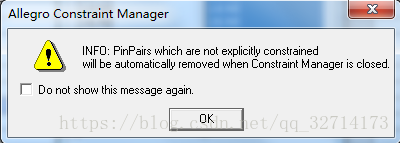

設定好pin pair之後按ok會出現這個警告,意思是設定完pin pair之後必須馬上設定規則,否則過一段時間,設定的pin pair會消失,得重新設定。

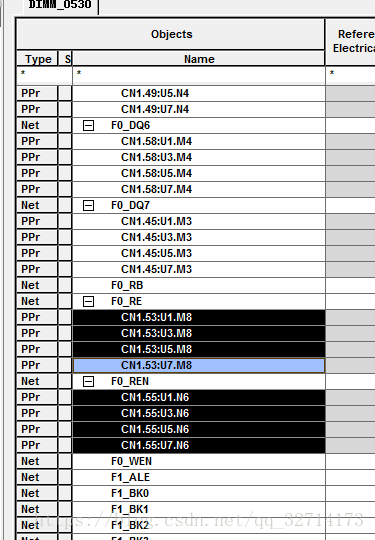

B、將F0的DQS、DQSN、DQ0~7、RE、REN選擇好pin pair之後,就可以設定match group。

需要將每個pin pair選中之後再右鍵creat-match group。如下圖。(不要直接點網路建立match group,一定要點pin pair)

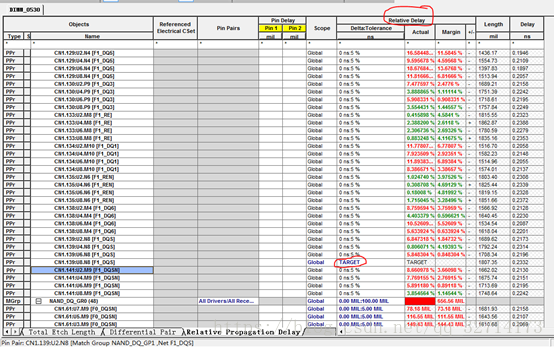

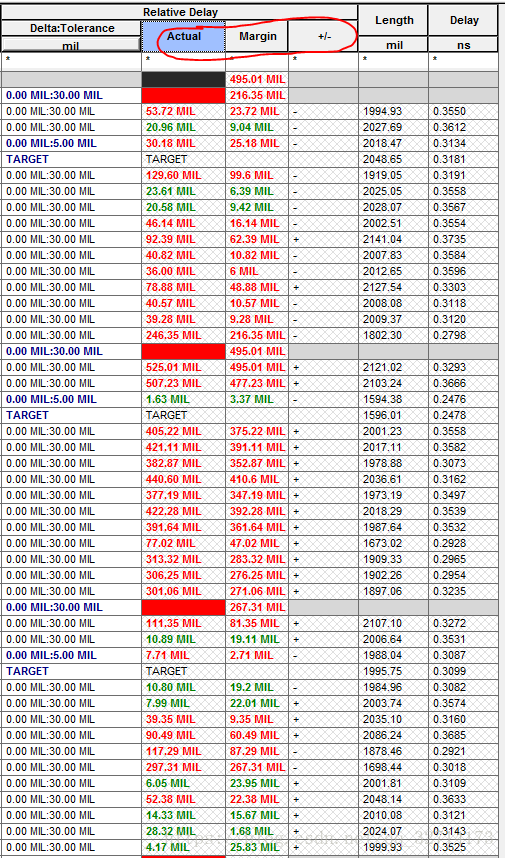

C、match group設定好之後,設定等長基準,這邊以DQS為基準(選擇其中一個即可),右鍵set as target。然後在其他單元格設定允許誤差的範圍,一般為0:100mil。然後後面紅色的資料表示超出範圍,綠色的資料表示在範圍內。

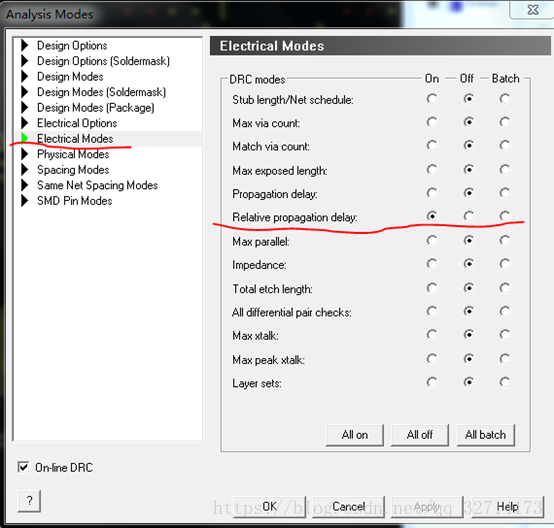

開啟檢查模式。Setup--constraint--modes

這個一定要開啟,不然規則裡面relative delay出不來,即如下圖所示3列是沒法顯示的。

D、之後就手動繞等長。

1)這個是走蛇形線。Options如下設定。(差分最好走5W線寬)

2)狀態條沒有顯示了(摘錄自網上)

F 、T型第一根引出的線可以走的比較長,但是延展到其他四個端點的線最好能走直線不要繞。雖然延伸出去的線是高阻狀態, 但是它會有反射,先越長反射越大,所以儘量走短線。。

net schedule,點選這個,點選想要檢視的網路,可以檢視從s端到d端的飛線。

順序是先讓T區兩端的線保持一樣長,總長誤差5mil以內的,比如DQS和DQSN這兩根線,兩端線的誤差就要在1mil以內。 總長誤差在100mil以內的,兩端線的誤差可以適當長一點。

可以點選 ,然後選擇想要檢視的物件,檢視線長資訊。

繞的之後掌握的技巧:

先看一下這一個match group裡面的線差距怎麼樣,然後找一個適當的長度,將基準線調成這個長度,然後先將誤差比較小的線完成,之後繞誤差相對可以大一點的。(一開始先調了基準線導致後面有些線無法縮小,之後得將所有線整體饒長)

G、饒等長比較方便的命令。

Route--timing vision

這個功能直接讓比基準長的一種顏色,比基準短的一種顏色,繞好的顯示一種顏色,直接繞就好了,不用去看規則管理器。

Route--auto-interactive delay tune

選擇命令,然後框選想要等長的線就好了。

H、最近畫好的板子在模擬的時候知道,等長不是根據基準DQS繞的,是需要組內所有長度誤差都在30ps以內,所以一開始可以根據上述步驟除錯,之後再根據模擬結果除錯。30ps約等於200mil(經驗值),以這個值調整出來的不會差很多。

8、關於規則的有關設定

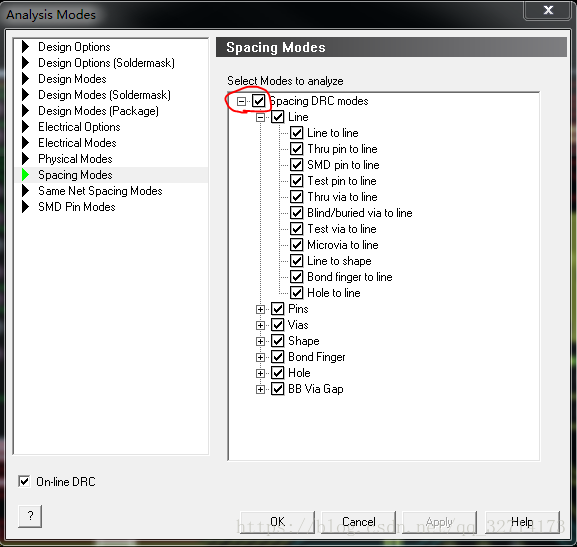

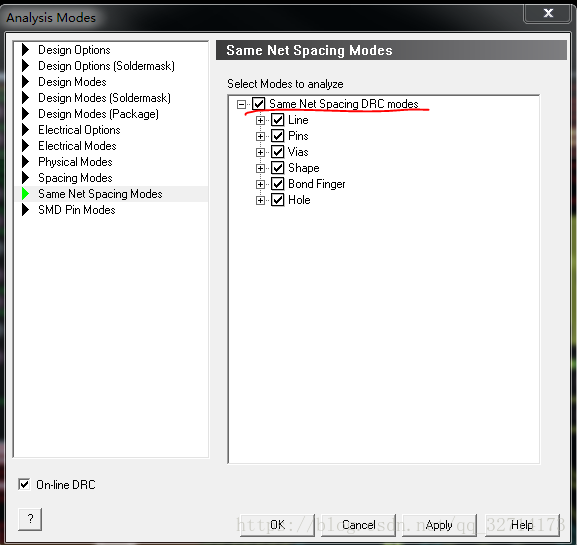

set up--Constraints--modes

這幾個引數都需要設定,具體看公司要求。

sapcing mode都需要開啟,假如有些可以忽略的再waive掉。

相同網路的靠太近也會報錯,這個也需要都開啟。

9、匯出設定

1)匯出選項

File→Export→Sub-Drawing

在Find 視窗中選擇需要匯出的選項,可以是option裡面的任何東西,比如Line/shape/cline。

2)在命令視窗輸入x 0 0 (匯出檔案的參考基準座標,Compelet完直接按X就可以不用去選下面的視窗,如果X被快捷鍵佔用則使用pick)

輸完座標後,按回車,彈出儲存CLP檔案的視窗,將CLP檔案命名儲存。

3)匯入選項

將CLP檔案放到需要匯入的檔案的當前目錄下

File→import→Sub-drawing選中需要匯入的CLP檔案

輸入基準座標(想匯入到哪個座標,就輸入什麼座標,基本為 x 0 0)

回車完成匯入。

PS:要在兩個PCB中相互匯入Line/shape/cline需要兩個檔案的疊層層數和各層的名字一致,一般的操作,會將匯出的檔案的疊層改成和要匯入的檔案一致,如果要匯入via,還需要在要匯入的PCB的中也有這個via的路徑

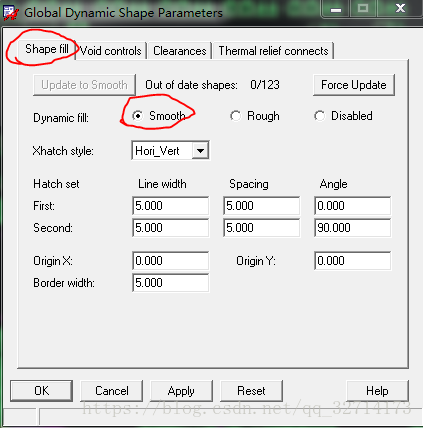

10、銅皮不能自動更新

銅皮屬性是dynamic copper,但是修改的過程中他不會自動更新。可以選擇shape--global dynamic shape parameters(這邊改動之後所有銅皮都會修改為相應的設定)

將dynamic fill設定為smooth即可。

11、修改Shape屬性的outline

首先關閉其他東西,直留一個outline。

然後shape--decompose shape,在option那邊選擇board geometry --outline。

最後框選住整個outline就會變成board geometry屬性的outline了。

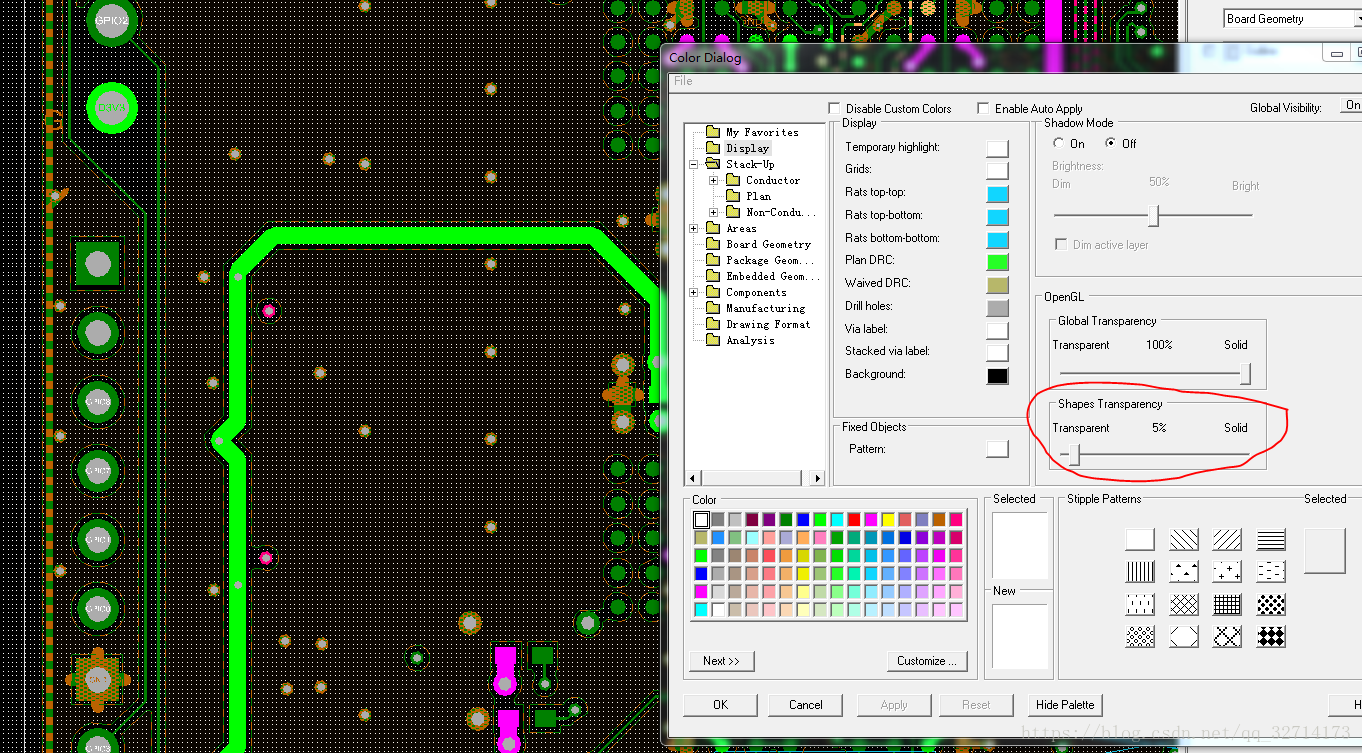

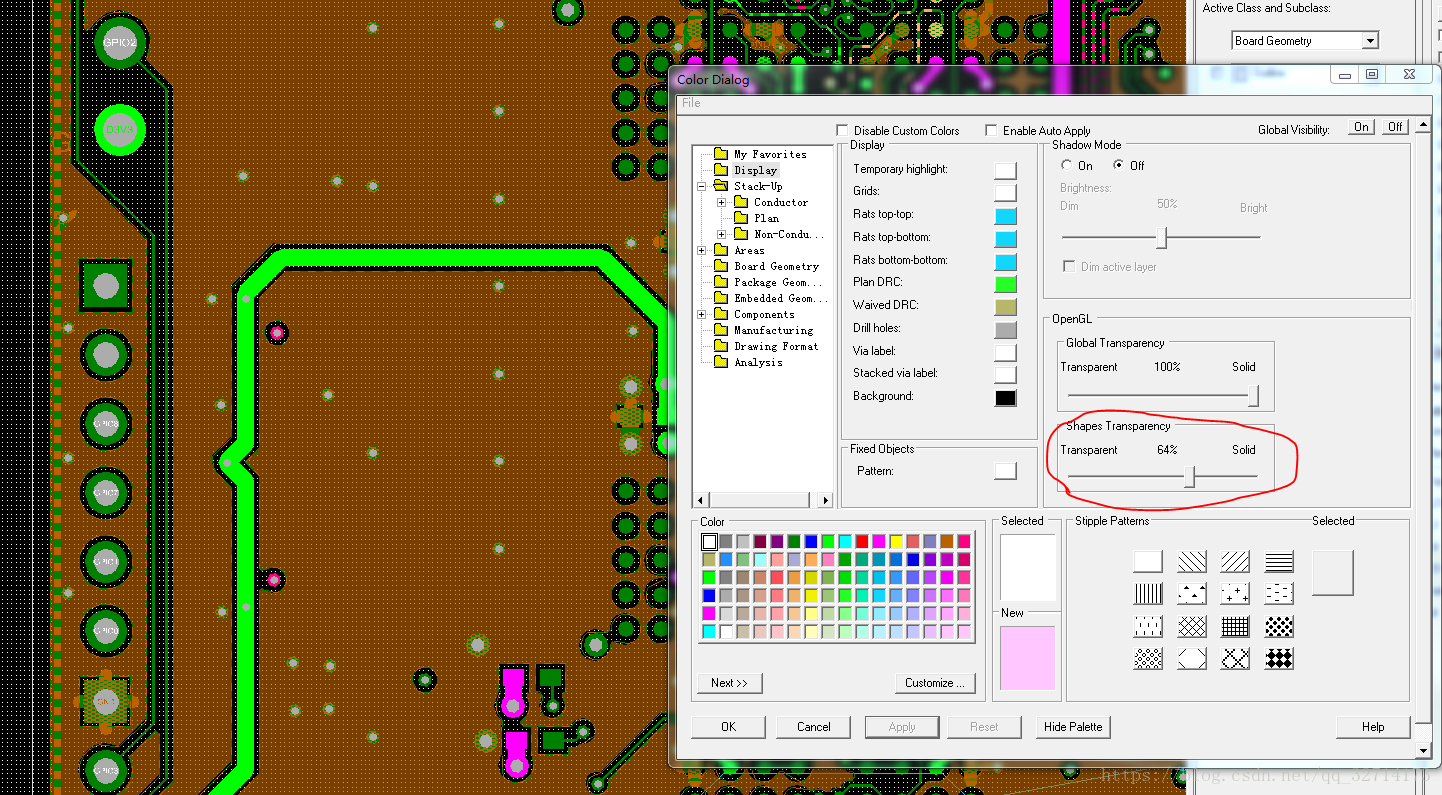

12、銅皮顯示修改

調高之後就可以正常顯示,上圖我總覺得和靜態銅皮一樣。

13、畫弧形線

Route--unsupported prototypes--auto-interactive convert corner

然後點選需要變弧形的線就可以整一條畫弧形。

14、工程性問題

PCB完成後需要檢查一下NPTH(非金屬化孔)是不是有金屬連線,有金屬連線都需要改成PTH(金屬化孔)。另外,NPTH也需要加上solder mask,假如不加板廠預設是塞孔。

在建通孔pad或者Via時也把公差加上,都按+/-4mil就可以了,安裝孔和插接孔,只能大不能少,避免因為公差原因無法安裝。(在出NC drill那邊修改)

調整字元時需要開啟對應層的Solder mask和焊盤,寧願刪除也不要壓到Solder mask上,所有的封裝製作時都需要對應的Assembly層絲印,以免刪除Silkscreen後沒有備用。

15、snap pick to

這是一個很好用的操作,先選擇一個命令,比如移動或者複製,然後滑鼠移動到想到操作的目標附近,右鍵選擇snap pick to。 (segment vertext為線段頂端,比較常用)之後目標會吸附在游標上,將目標移動到相應位置,再右鍵選擇snap pick to,至此操作完成。

在shape edit boundary時也很有用,因為假如銅皮的端點不在格點上的話是選中不了的,這個時候就可以選擇snap pick to--segment vertsxt,這樣就可以很容易的選中銅皮的端點。

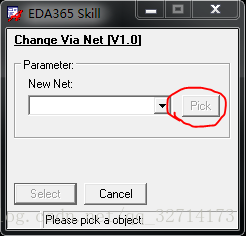

16、更換via的網路

需要使用EDA365 skill

3、route tools--change via’s net

出現以下對話方塊,點選pick

然後點選相應網路,done。

再選擇select,點選相應過孔,done

17、Waive DRC

Waive DRC之後還會顯示是因為waive掉的DRC是在show的狀態下。

選擇display--waive DRCs--blank即可關閉。當然選擇show可以開啟,在最後檢查的時候可以選擇show再檢查一遍waive掉的DRC是否沒有影響。

18、銅皮過BGA

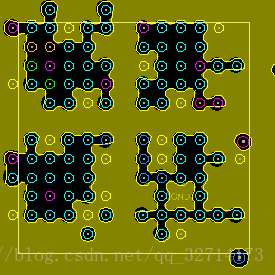

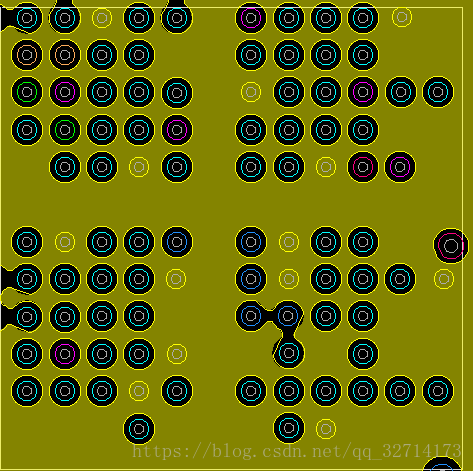

敷銅過bga的時候會遇到以下問題

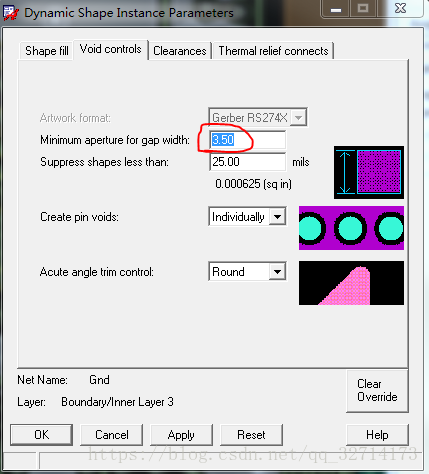

這樣的銅皮比較參考性就不是很好了。可以設定以下引數,shape select--選中銅皮右鍵--parameters即可出現以下對話方塊。

將紅圈標註位置設定為3.5即可變成下圖所示

這樣銅皮就相對比較完整。

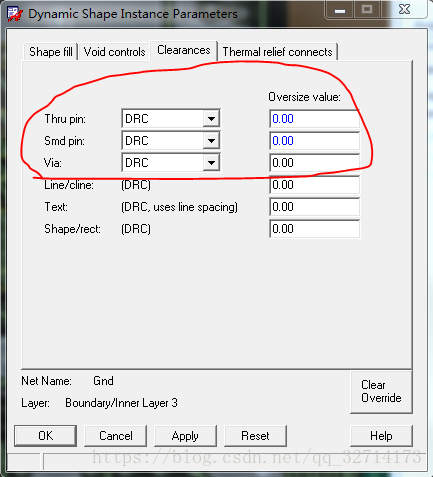

需要說明一下這邊的引數是在規則管理器設定的引數上面再額外加的。

比如假如在規則裡面設定shape to via的間距為4mil,然後又在parameters 這邊設定via的間距為4mil,那麼實際上shape to via的間距會變為8mil。

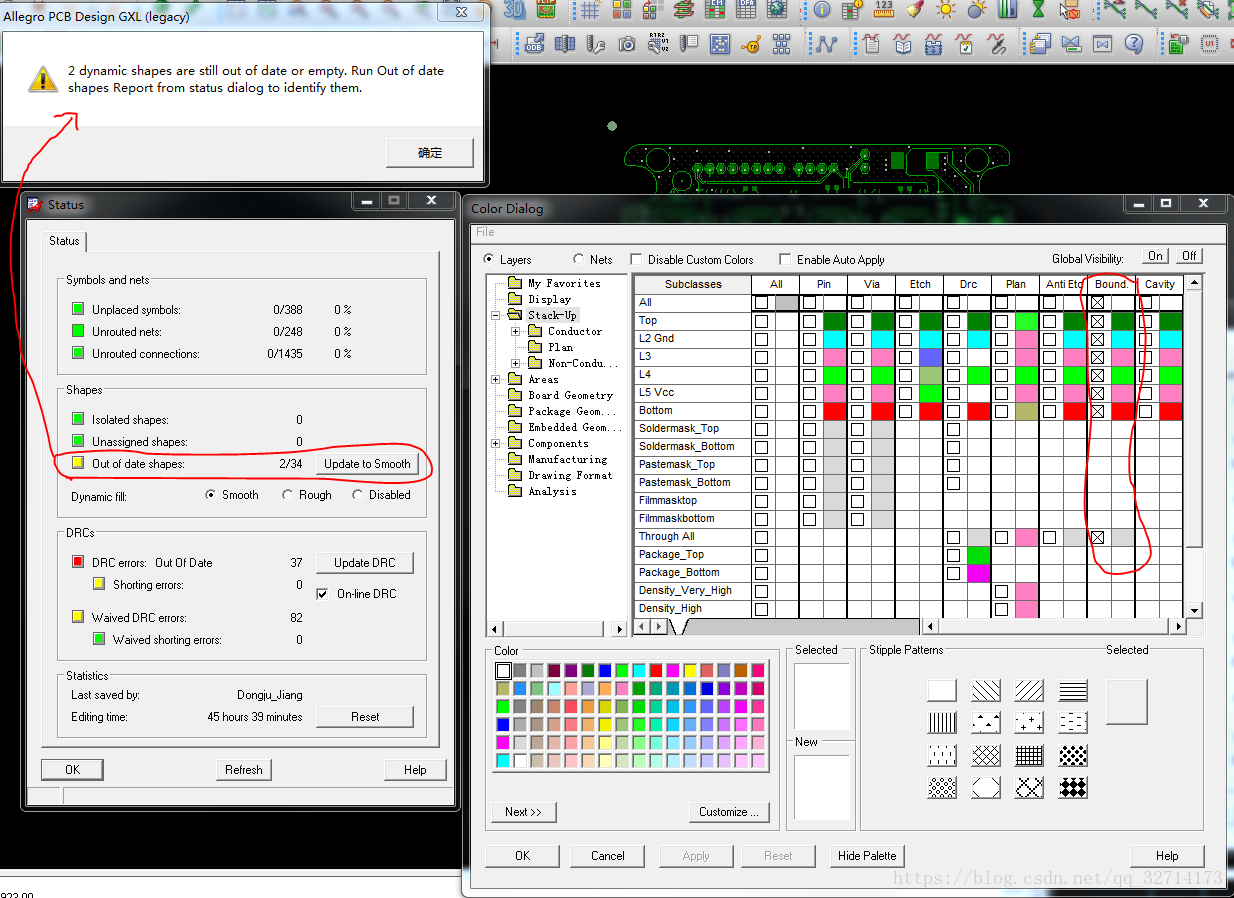

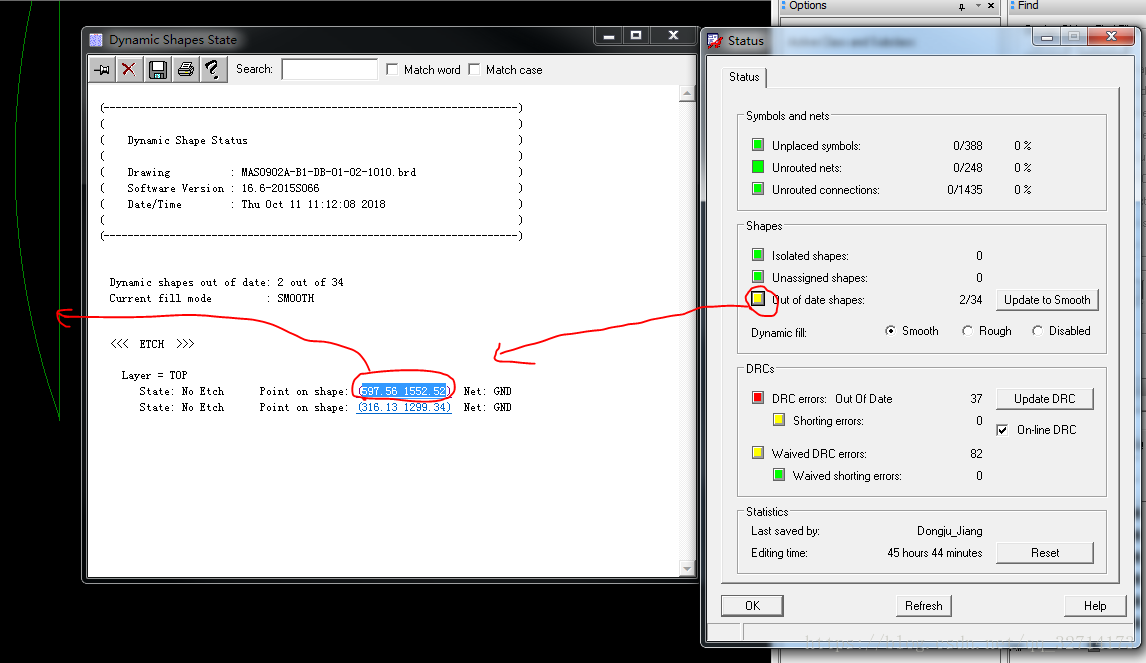

19、update to smooth

有的時候不能update to smooth,因為只有一個外框但是沒有填充的shape是刪除不了的。這個時候可以關閉所有圖層然後開啟bound。

點選out of data shape前面那個小框,會出現對應沒刪除銅皮的座標,點選座標即可跳轉到相應的銅皮,刪除即可。

20、複用佈局和走線

選擇placement edit模式

選擇除group之外其他的選項,框選需要複用的佈局,右鍵(需要選中元器件右鍵)place replicate create,在空白處右鍵done,會自動跳出需要儲存的檔案,命名後儲存即可。

然後選擇還未佈局的元器件(劃重點!必須是一模一樣,有一點不一樣都會導致複用佈局出錯),右鍵(需要選中元器件右鍵,其他位置右鍵不會出來相應選項)place replicate apply,選擇剛才儲存的檔案即可。

複用一遍之後有改動需要再次複用時,需要先在placement edit 模式下選擇group,然後右鍵disband group。然後再按之前的步驟即可複用。

這個技巧操作過程中可能會出挺多錯,有時候也會有元器件對不上的情況,但是你多試幾遍熟悉了之後就會覺得挺方便的。