STM32F4學習筆記13——ADC part1

ADC 簡介

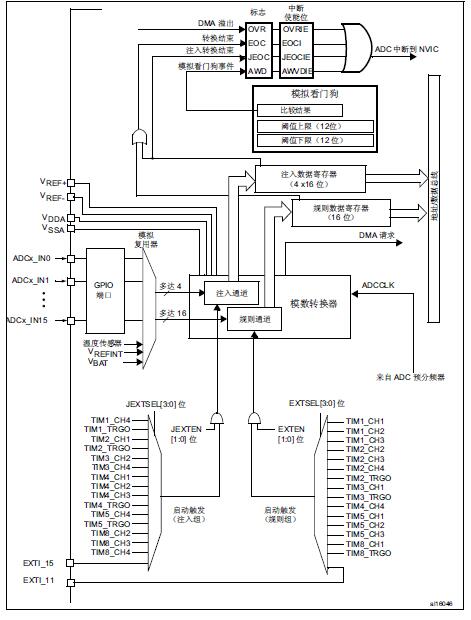

12 位 ADC 是逐次趨近型模數轉換器。它具有多達 19 個複用通道,可測量來自 16 個外部 源、兩個內部源和 VBAT 通道的訊號。這些通道的 A/D 轉換可在單次、連續、掃描或不連續 取樣模式下進行。ADC 的結果儲存在一個左對齊或右對齊的 16 位資料暫存器中。

ADC 具有模擬看門狗特性,允許應用檢測輸入電壓是否超過了使用者自定義的閾值上限或下限。

ADC 主要特性

● 可配置 12 位、10 位、8 位或 6 位解析度

● 在轉換結束、注入轉換結束以及發生模擬看門狗或溢位事件時產生中斷

● 單次和連續轉換模式

● 用於自動將通道 0 轉換為通道“n”的掃描模式

● 資料對齊以保持內建資料一致性

● 可獨立設定各通道取樣時間

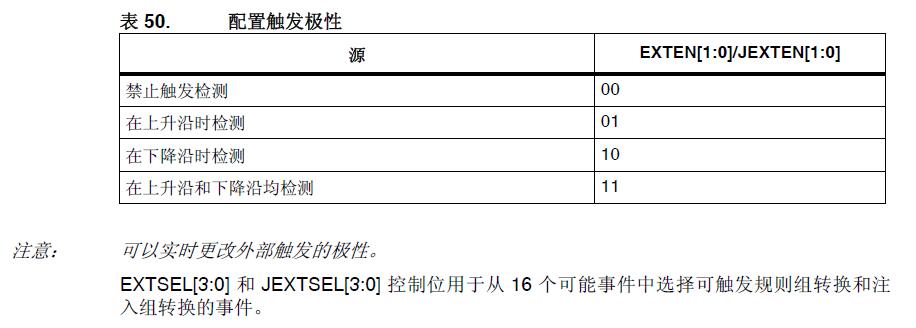

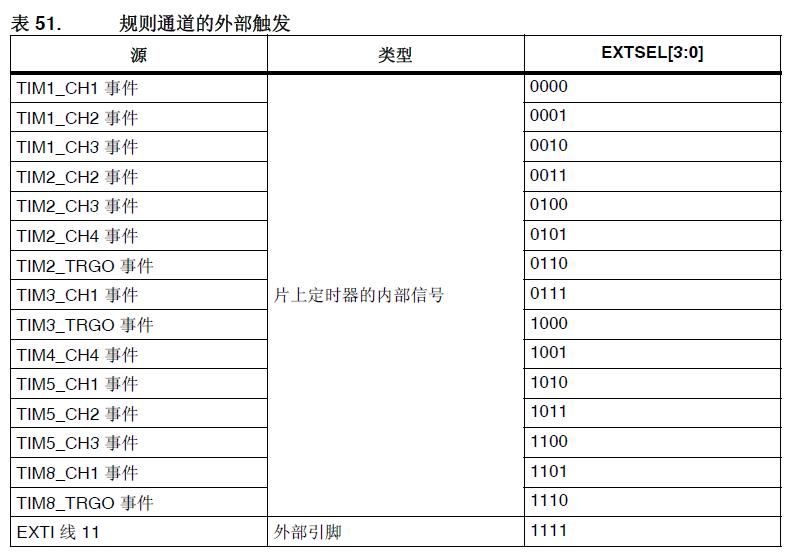

● 外部觸發器選項,可為規則轉換和注入轉換配置極性

● 不連續取樣模式

● 雙重/三重模式(具有 2 個或更多 ADC 的器件提供)

● 雙重/三重 ADC 模式下可配置的 DMA 資料儲存

● 雙重/三重交替模式下可配置的轉換間延遲

● ADC 轉換型別(參見資料手冊)

● ADC 電源要求:全速執行時為 2.4 V 到 3.6 V,慢速執行時為 1.8 V

● ADC 輸入範圍:VREF— VIN VREF+

● 規則通道轉換期間可產生 DMA 請求

圖 34 顯示了 ADC 的框圖。

注意:VREF— 如果可用(取決於封裝),則必須將其連線到 VSSA

ADC 功能說明

ADC 開關控制

可通過將 ADC_CR2 暫存器中的 ADON 位置 1 來為 ADC 供電。首次將 ADON 位置 1 時, 會將 ADC 從掉電模式中喚醒。

SWSTART 或 JSWSTART 位置 1 時,啟動 AD 轉換。

可通過將 ADON 位清零來停止轉換並使 ADC 進入掉電模式。在此模式下,ADC 幾乎不耗電 (只有幾 μA)。

ADC 時鐘

ADC 具有兩個時鐘方案:

● 用於類比電路的時鐘:ADCCLK,所有 ADC 共用

此時鐘來自於經可程式設計預分頻器分頻的 APB2 時鐘,該預分頻器允許 ADC 在 fPCLK2/2、/4、/6 或 /8 下工作。有關 ADCCLK 的最大值,請參見資料手冊。

● 用於數字介面的時鐘(用於暫存器讀/寫訪問)

此時鐘等效於 APB2 時鐘。可以通過 RCC APB2 外設時鐘使能暫存器 (RCC_APB2ENR)分別為每個 ADC 使能/禁止數字介面時鐘。

通道選擇

有 16 條複用通道。可以將轉換分為兩組:規則轉換和注入轉換。每個組包含一個轉換序列, 該序列可按任意順序在任意通道上完成。例如,可按以下順序對序列進行轉換:ADC_IN3、ADC_IN8、ADC_IN2、ADC_IN2、ADC_IN0、ADC_IN2、ADC_IN2、ADC_IN15。

● 一個規則轉換組最多由 16 個轉換構成。必須在 ADC_SQRx 暫存器中選擇轉換序列的規

則通道及其順序。規則轉換組中的轉換總數必須寫入 ADC_SQR1 暫存器中的 L[3:0] 位。

● 一個注入轉換組最多由 4 個轉換構成。必須在 ADC_JSQR 暫存器中選擇轉換序列的注入

通道及其順序。注入轉換組中的轉換總數必須寫入 ADC_JSQR 暫存器中的 L[1:0] 位。

如果在轉換期間修改 ADC_SQRx 或 ADC_JJSQR 暫存器,將復位當前轉換並向 ADC 傳送一個新的啟動脈衝,以轉換新選擇的組。

溫度感測器、VREFINT 和 VBAT 內部通道

● 對於 STM32F40x 和 STM32F41x 器件,溫度感測器內部連線到通道 ADC1_IN16。

內部參考電壓 VREFINT 連線到 ADC1_IN17。

● 對於 STM23F42x 和 STM32F43x 器件,溫度感測器內部連線到與 VBAT 共用的通道ADC1_IN18。一次只能選擇一個轉換(溫度感測器或 VBAT)。同時設定了溫度感測器和 VBAT 轉換時,將只進行 VBAT 轉換。

內部參考電壓 VREFINT 連線到 ADC1_IN17。

VBAT 通道連線到通道 ADC1_IN18。該通道也可轉換為注入通道或規則通道。

注意:溫度感測器、VREFINT 和 VBAT 通道只在主 ADC1 外設上可用。

單次轉換模式

在單次轉換模式下,ADC 執行一次轉換。CONT 位為 0 時,可通過以下方式啟動此模式:

● 將 ADC_CR2 暫存器中的 SWSTART 位置 1(僅適用於規則通道)

● 將 JSWSTART 位置 1(適用於注入通道)

● 外部觸發(適用於規則通道或注入通道)

完成所選通道的轉換之後:

● 如果轉換了規則通道:

— 轉換資料儲存在 16 位 ADC_DR 暫存器中

— EOC(轉換結束)標誌置 1

— EOCIE 位置 1 時將產生中斷

● 如果轉換了注入通道:

— 轉換資料儲存在 16 位 ADC_JDR1 暫存器中

— JEOC(注入轉換結束)標誌置 1

— JEOCIE 位置 1 時將產生中斷

然後,ADC 停止。

連續轉換模式

在連續轉換模式下,ADC 結束一個轉換後立即啟動一個新的轉換。CONT 位為 1 時,可通過外部觸發或將 ADC_CR2 暫存器中的 SWSTRT 位置 1 來啟動此模式(僅適用於規則通道)。

每次轉換之後:

● 如果轉換了規則通道組:

— 上次轉換的資料儲存在 16 位 ADC_DR 暫存器中

— EOC(轉換結束)標誌置 1

— EOCIE 位置 1 時將產生中斷

注意:無法連續轉換注入通道。連續模式下唯一的例外情況是,注入通道配置為在規則通道之後自動轉換(使用 JAUTO 位),請參見自動注入一節。

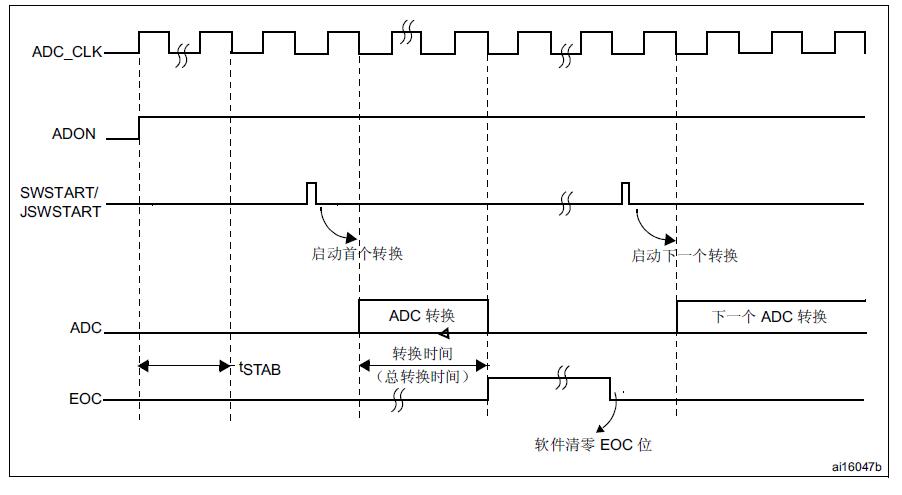

時序圖

ADC 在開始精確轉換之前需要一段穩定時間 tSTAB。ADC 開始轉換並經過 15 個 時鐘週期後,EOC 標誌置 1,轉換結果存放在 16 位 ADC 資料暫存器中。

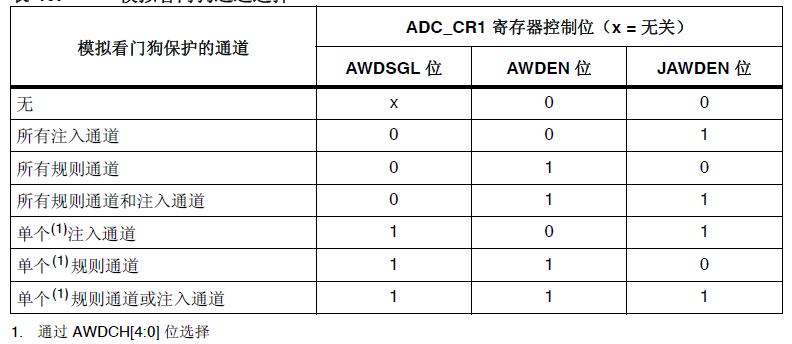

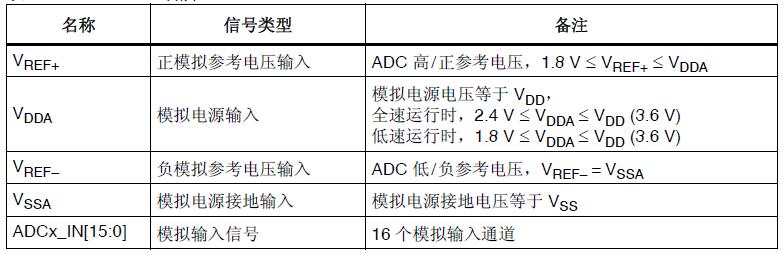

模擬看門狗

如果 ADC 轉換的模擬電壓低於閾值下限或高於閾值上限,則 AWD 模擬看門狗狀態位會置 1。這些閾值在 ADC_HTR 和 ADC_LTR 16 位暫存器的 12 個最低有效位中進行程式設計。可以 使用 ADC_CR1 暫存器中的 AWDIE 位使能中斷。

閾值與 ADC_CR2 暫存器中的 ALIGN 位的所選對齊方式無關。在對齊之前,會將模擬電壓 與閾值上限和下限進行比較。

下表介紹了應如何配置 ADC_CR1 暫存器才能在一個或多個通道上使能模擬看門狗。

掃描模式

此模式用於掃描一組模擬通道。

通過將 ADC_CR1 暫存器中的 SCAN 位置 1 來選擇掃描模式。將此位置 1 後,ADC 會掃描 在 ADC_SQRx 暫存器(對於規則通道)或 ADC_JSQR 暫存器(對於注入通道)中選擇的 所有通道。為組中的每個通道都執行一次轉換。每次轉換結束後,會自動轉換該組中的下一個通道。如果將 CONT 位置 1,規則通道轉換不會在組中最後一個所選通道處停止,而是再 次從第一個所選通道繼續轉換。

如果將 DMA 位置 1,則在每次規則通道轉換之後,均使用直接儲存器訪問 (DMA) 控制器將 轉換自規則通道組的資料(儲存在 ADC_DR 暫存器中)傳輸到 SRAM。

在以下情況下,ADC_SR 暫存器中的 EOC 位置 1:

● 如果 EOCS 位清零,在每個規則組序列轉換結束時

● 如果 EOCS 位置 1,在每個規則通道轉換結束時

從注入通道轉換的資料始終儲存在 ADC_JDRx 暫存器中。

注入通道管理

觸發注入

要使用觸發注入,必須將 ADC_CR1 暫存器中的 JAUTO 位清零。

1.通過外部觸發或將 ADC_CR2 暫存器中的 SWSTART 位置 1 來啟動規則通道組轉換。

2. 如果在規則通道組轉換期間出現外部注入觸發或者 JSWSTART 位置 1,則當前的轉換 會復位,並且注入通道序列會切換為單次掃描模式。

3. 然後,規則通道組的規則轉換會從上次中斷的規則轉換處恢復。

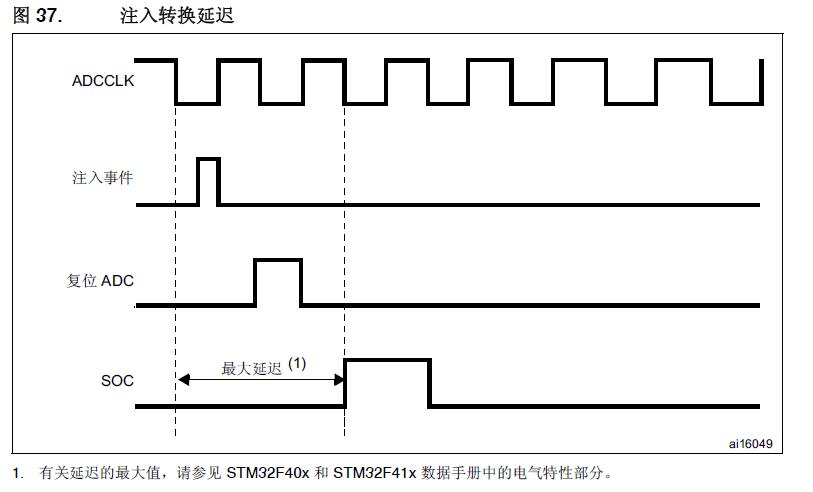

如果在注入轉換期間出現規則事件,注入轉換不會中斷,但在注入序列結束時會執行規則序列。圖 37 顯示了相應的時序圖。

注意:使用觸發注入時,必須確保觸發事件之間的間隔長於注入序列。例如,如果序列長度為 30 個 ADC 時鐘週期(即,取樣時間為 3 個時鐘週期的兩次轉換),則觸發事件的最小間隔不能 小於 31 個 ADC 時鐘週期。

自動注入

如果將 JAUTO 位置 1,則注入組中的通道會在規則組通道之後自動轉換。這可用於轉換最 多由 20 個轉換構成的序列,這些轉換在 ADC_SQRx 和 ADC_JSQR 暫存器中程式設計。

在此模式下,必須禁止注入通道上的外部觸發。

如果 CONT 位和 JAUTO 位均已置 1,則在轉換規則通道之後會繼續轉換注入通道。

注意:不能同時使用自動注入和不連續取樣模式。

不連續取樣模式

規則組

可將 ADC_CR1 暫存器中的 DISCEN 位置 1 來使能此模式。該模式可用於轉換含有 n (n 8) 個轉換的短序列,該短序列是在 ADC_SQRx 暫存器中選擇的轉換序列的一部分。可通過寫 入 ADC_CR1 暫存器中的 DISCNUM[2:0] 位來指定 n 的值。

出現外部觸發時,將啟動在 ADC_SQRx 暫存器中選擇的接下來 n 個轉換,直到序列中的所 有轉換均完成為止。通過 ADC_SQR1 暫存器中的 L[3:0] 位定義總序列長度。

示例:

n = 3,要轉換的通道 = 0、1、2、3、6、7、9、10

第 1 次觸發:轉換序列 0、1、2

第 2 次觸發:轉換序列 3、6、7

第 3 次觸發:轉換序列 9、10 並生成 EOC 事件

第 4 次觸發:轉換序列 0、1、2

注意:在不連續取樣模式下轉換規則組時,不會出現翻轉。

轉換完所有子組後,下一個觸發訊號將啟動第一個子組的轉換。在上述示例中,第 4 次觸發 重新轉換了第 1 個子組中的通道 0、1 和 2。

注入組

可將 ADC_CR1 暫存器中的 JDISCEN 位置 1 來使能此模式。在出現外部觸發事件之後,可 使用該模式逐通道轉換在 ADC_JSQR 暫存器中選擇的序列。

出現外部觸發時,將啟動在 ADC_JSQR 暫存器中選擇的下一個通道轉換,直到序列中的所 有轉換均完成為止。通過 ADC_JSQR 暫存器中的 JL[1:0] 位定義總序列長度。

示例:

n = 1,要轉換的通道 = 1、2、3

第 1 次觸發:轉換通道 1 、2、3

第 2 次觸發:轉換通道 2

第 3 次觸發:轉換通道 3 並生成 EOC 和 JEOC 事件

第 4 次觸發:通道 1

注意:轉換完所有注入通道後,下一個觸發訊號將啟動第一個注入通道的轉換。在上述示例中,第 4 次觸發重新轉換了第 1 個注入通道。

不能同時使用自動注入和不連續取樣模式。

不得同時為規則組和注入組設定不連續取樣模式。只能針對一個組使能不連續取樣模式。

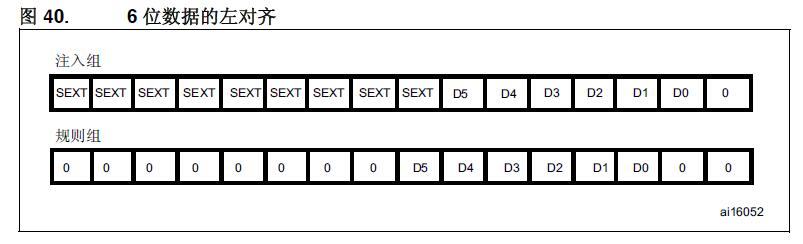

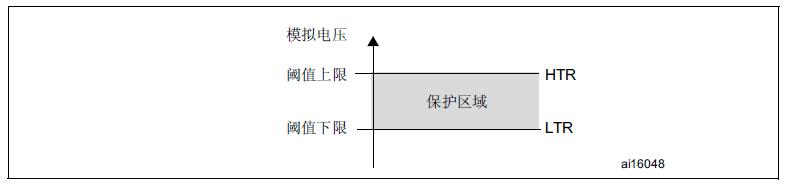

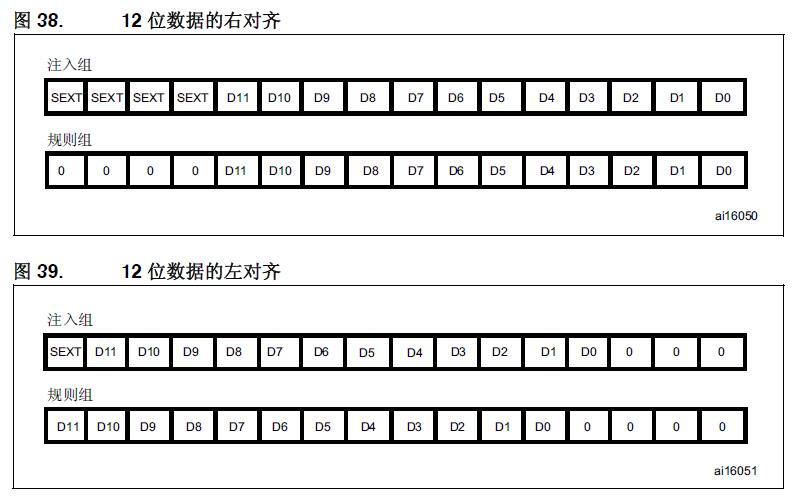

資料對齊

ADC_CR2 暫存器中的 ALIGN 位用於選擇轉換後儲存的資料的對齊方式。可選擇左對齊和 右對齊兩種方式,如圖 38 和圖 39 所示。

注入通道組的轉換資料將減去 ADC_JOFRx 暫存器中寫入的使用者自定義偏移量,因此結果可 以是一個負值。SEXT 位表示擴充套件的符號值。

對於規則組中的通道,不會減去任何偏移量,因此只有十二個位有效。

特例:採用左對齊時,資料基於半字進行對齊,除了解析度設定為 6 位時。解析度設定為 6 位 時,資料基於位元組進行對齊,如圖 40 所示。

可獨立設定各通道取樣時間

ADC 會在數個 ADCCLK 週期內對輸入電壓進行取樣,可使用 ADC_SMPR1 和 ADC_SMPR2 暫存器中的 SMP[2:0] 位修改週期數。每個通道均可以使用不同的取樣時間進行取樣。

總轉換時間的計算公式如下:

Tconv = 取樣時間 + 12 個週期

示例:

ADCCLK = 30 MHz 且取樣時間 = 3 個週期時:

Tconv = 3 + 12 = 15 個週期 = 0.5 μs(APB2 為 60 MHz 時)

外部觸發轉換和觸發極性

可以通過外部事件(例如,定時器捕獲、EXTI 中斷線)觸發轉換。如果 EXTEN[1:0] 控制位 (對於行規轉換)或 JEXTEN[1:0] 位(對於注入轉換)不等於“0b00”,則外部事件能夠 以所選極性觸發轉換。表 50 提供了 EXTEN[1:0] 和 JEXTEN[1:0] 值與觸發極性之間的對應 關係。

可通過將 ADC_CR2 暫存器中的 SWSTART(對於規則轉換)或 JSWSTART(對於注入轉 換)位置 1 來產生軟體源觸發事件。

可通過注入觸發中斷規則組轉換。

注意:可以實時更改觸發選擇。不過,當更改觸發選擇時,會在 1 個 APB 時鐘週期的時間範圍內禁 止觸發檢測。這是為了避免在轉換期間出現意外檢測。

快速轉換模式

可通過降低 ADC 解析度來執行快速轉換。RES 位用於選擇資料暫存器中可用的位數。每種 解析度的最小轉換時間如下:

● 12 位:3 + 12 = 15 ADCCLK 週期

● 10 位:3 + 10 = 13 ADCCLK 週期

● 8 位:3 + 8 = 11 ADCCLK 週期

● 6 位:3 + 6 = 9 ADCCLK 週期

使用 DMA

由於規則通道組只有一個數據暫存器,因此,對於多個規則通道的轉換,使用 DMA 非常有 幫助。這樣可以避免丟失在下一次寫入之前還未被讀出的 ADC_DR 暫存器中的資料。

在使能 DMA 模式的情況下(ADC_CR2 暫存器中的 DMA 位置 1),每完成規則通道組中的 一個通道轉換後,都會生成一個 DMA 請求。這樣便可將轉換的資料從 ADC_DR 暫存器傳輸 到用軟體選擇的目標位置。

儘管如此,如果資料丟失(溢位),則會將 ADC_SR 暫存器中的 OVR 位置 1 並生成一箇中 斷(如果 OVRIE 使能位已置 1)。隨後會禁止 DMA 傳輸並且不再接受 DMA 請求。在這種 情況下,如果生成 DMA 請求,則會中止正在進行的規則轉換並忽略之後的規則觸發。隨後 需要將所使用的 DMA 流中的 OVR 標誌和 DMAEN 位清零,並重新初始化 DMA 和 ADC, 以將需要的轉換通道資料傳輸到正確的儲存器單元。只有這樣,才能恢復轉換並再次使能資料傳輸。注入通道轉換不會受到溢位錯誤的影響。

在 DMA 模式下,當 OVR = 1 時,傳送完最後一個有效資料後會阻止 DMA 請求,這意味著 傳輸到 RAM 的所有資料均被視為有效。

在最後一次 DMA 傳輸(DMA 控制器的 DMA_SxRTR 暫存器中配置的傳輸次數)結束時:

● 如果將 ADC_CR2 暫存器中的 DDS 位清零,則不會向 DMA 控制器發出新的 DMA 請求

(這可避免產生溢位錯誤)。不過,硬體不會將 DMA 位清零。必須將該位寫入 0 然後

寫入 1 才能啟動新的傳輸。

● 如果將 DDS 位置 1,則可繼續生成請求。從而允許在雙緩衝區迴圈模式下配置 DMA。

要在使用 DMA 時將 ADC 從 OVR 狀態中恢復,請按以下步驟操作:

1.重新初始化 DMA(調整目標地址和 NDTR 計數器)

2. 將 ADC_SR 暫存器中的 ADC OVR 位清零

3. 觸發 ADC 以開始轉換。

在不使用 DMA 的情況下管理轉換序列

如果轉換過程足夠慢,則可使用軟體來處理轉換序列。在這種情況下,必須將 ADC_CR2 寄 存器中的 EOCS 位置 1,才能使 EOC 狀態位在每次轉換結束時置 1,而不僅是在序列結束 時置 1。當 EOCS = 1 時,會自動使能溢位檢測。因此,每當轉換結束時,EOC 都會置 1, ᅠ ᅠ

並且可以讀取 ADC_DR 暫存器。溢位管理與使用 DMA 時的管理相同。

要在 EOCS 位置 1 時將 ADC 從 OVR 狀態中恢復,請按以下步驟操作:

1.將 ADC_SR 暫存器中的 ADC OVR 位清零

2. 觸發 ADC 以開始轉換。

在不使用 DMA 和溢位檢測的情況下進行轉換

ADC 在轉換一個或多個通道時不是每次都讀取資料的情況下,這可能會很有用(例如,存在 模擬看門狗時)。為此,必須禁止 DMA (DMA = 0) 並且僅在序列結束 (EOCS = 0) 時才將 ᅠ ᅠ ᅠ ᅠ

EOC 位置 1。在此配置中,溢位檢測已禁止。