I2C匯流排的同步和仲裁

阿新 • • 發佈:2019-02-12

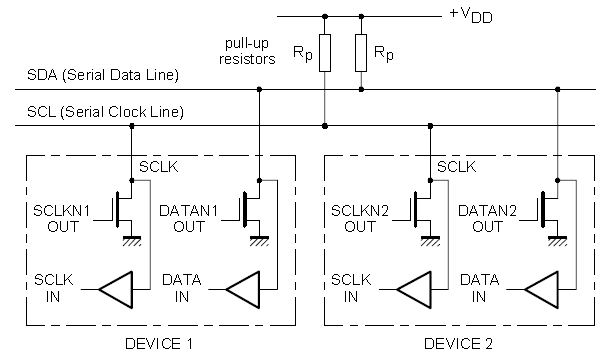

每一個IIC匯流排器件內部的SDA、SCL引腳電路結構都是一樣的,引腳的輸出驅動與輸入緩衝連在一起。其中輸出為漏極開路的場效電晶體、輸入緩衝為一隻高輸入阻抗的同相器[1]。這種電路具有兩個特點:

①由於SDA、SCL為漏極開路結構,藉助於外部的上拉電阻實現了訊號的“線與”邏輯;

②引腳在輸出訊號的同時還將引腳上的電平進行檢測,檢測是否與剛才輸出一致。為 “時鐘同步”和“匯流排仲裁”提供硬體基礎。

I2C匯流排介面內部結構

IIC裝置對匯流排的操作僅有“把線路接地”——輸出邏輯0。基於IIC匯流排的設計,線路上不可能出現電平衝突現象。如果一裝置傳送邏輯0,其他傳送邏輯1,那麼線路看到的只有邏輯0。也就是說,如果出現電平衝突,傳送邏輯0的始終是“贏家”。匯流排的物理接法允許主裝置往匯流排寫資料的同事讀取資料。這樣兩主裝置爭匯流排的時候“贏家”並不知道競爭的發生,只有“輸家”發現了衝突——當寫一個邏輯1,卻讀到了0——而退出競爭。

時鐘同步

如果被控器希望主控器降低傳送速度可以通過將SCL主動拉低延長其低電平時間的方法來通知主控器,當主控器在準備下一次傳送發現SCL的電平被拉低時就進行等待,直至被控器完成操作並釋放SCL線的控制控制權。這樣以來,主控器實際上受到被控器的時鐘同步控制。可見SCL線上的低電平是由時鐘低電平最長的器件決定;高電平的時間由高電平時間最短的器件決定。這就是時鐘同步,它解決了I2C匯流排的速度同步。

匯流排仲裁

假設主控器1要傳送的資料DATA1為“101 ……”;主控器2要傳送的資料DATA2為“1001 ……”匯流排被啟動後兩個主控器在每傳送一個數據位時都要對自己的輸出電平進行檢測,只要檢測的電平與自己發出的電平一致,他們就會繼續佔用匯流排。在這種情況下匯流排還是得不到仲裁。當主控器1傳送第3位資料“1”時(主控器2傳送“0” ),由於“線與”的結果SDA上的電平為“0”,這樣當主控器1檢測自己的輸出電平時,就會測到一個與自身不相符的“0”電平。這時主控器1只好放棄對匯流排的控制權;因此主控器2就成為匯流排的唯一主宰者。不難看出:

- ① 對於整個仲裁過程主控器1和主控器2都不會丟失資料;

- ② 各個主控器沒有對匯流排實施控制的優先級別;

- ③匯流排控制隨即而定,他們遵循“低電平優先”的原則,即誰先發送低電平誰就會掌握對匯流排的控制權。

- ①主控器通過檢測SCL上的電平來調節與從器件的速度同步問題——時鐘同步;

- ②主控器通過檢測SDA上自身傳送的電平來判斷是否發生匯流排“衝突”——匯流排仲裁。因此,I2C匯流排的“時鐘同步”與“匯流排仲裁”是靠器件自身介面的特殊結構得以實現的。

[1]同相器:當輸入高電平時輸出也是高電平,輸入低電平時輸出也是低電平。主要要於需要緩衝的場合,就是隻要輸入很小的電流,可輸出較大的電流,增加帶載能力。