Vivado使用技巧(2):封裝自己設計的IP核

概述

Vivado在設計時可以感覺到一種趨勢,它鼓勵用IP核的方式進行設計。“IP Integrator”提供了原理圖設計的方式,只需要在其中呼叫設計好的IP核連線。IP核一部分來自於Xilinx官方IP;一部分來自於第三方IP,其中有的是在網路上開源的;另一部分就是自己設計的IP。有時候我們需要把自己的一個設計反覆用到以後的工程中,利用Vivado的“IP Package”將其封裝起來,再以後的工程中直接呼叫即可。

本文致力於講述如何將自己的設計封裝為IP核,以及示範一下如何在其它工程中呼叫自己設計好的IP核。本文采用的設計是一個簡單的位寬可設定的加法器。博主使用的Vivado版本是2017.1,其它版本在一些設定的地方可能存在一些差異。

封裝IP

1. 首先建立一個工程用於設計IP核,這個工程最好放在Vivado目錄下或不會被刪除的地方。新增一個原始檔,輸入一個簡單的組合邏輯加法器的程式碼:

`timescale 1ns / 1ps

module Add_USR_IP #(parameter WIDTH = 1)(

input [WIDTH:0] a,

input [WIDTH:0] b,

output cout,

output [WIDTH:0] c

);

assign {cout, c} = a + b;

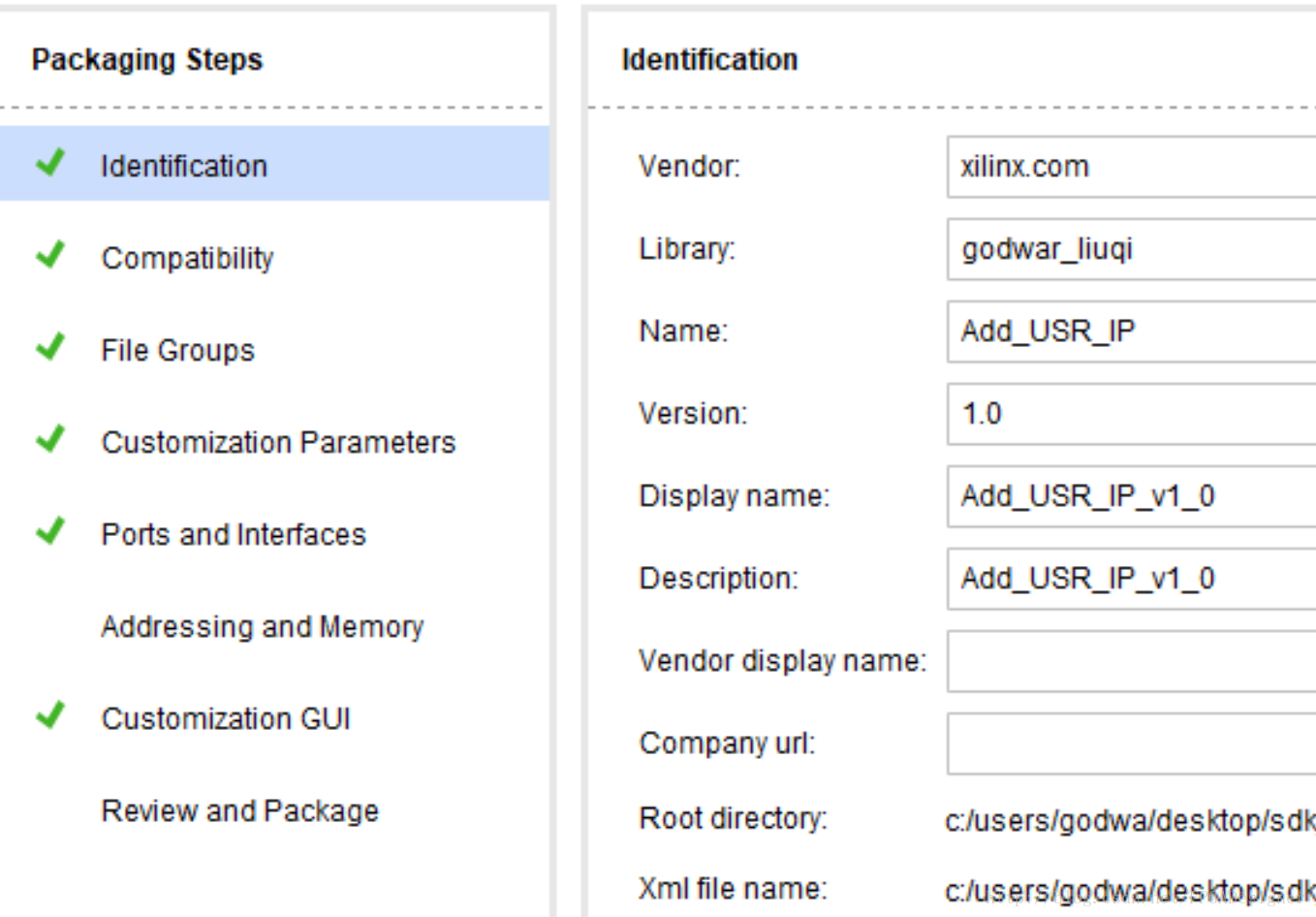

endmodule 2. 點選左邊“Flow Navigator”中的“Settings”,開啟“IP”下的“Packager”。設定自己的IP核的庫名和目錄,我將Library更改為了“godwar_liuqi”,Category更改為了“/godwar_liuqi_IPLib”。這裡也可以用預設值。

3

**4**. 在上述介面的“Compatibility”標籤下給出了這個IP可以支援的FPGA系列,預設是支援全部系列。“File Groups”中可以看到這個IP包含的檔案,可以為這個IP新增一個模擬檔案來驗證其功能。

**5**. 我為了實現加法位寬可調整,源程式中使用了parameter引數。開啟上述介面中的“Customization Parameters”標籤,將看到這個引數WIDTH:

**4**. 在上述介面的“Compatibility”標籤下給出了這個IP可以支援的FPGA系列,預設是支援全部系列。“File Groups”中可以看到這個IP包含的檔案,可以為這個IP新增一個模擬檔案來驗證其功能。

**5**. 我為了實現加法位寬可調整,源程式中使用了parameter引數。開啟上述介面中的“Customization Parameters”標籤,將看到這個引數WIDTH:

呼叫自己的IP核

再另外新建一個工程,我們嘗試呼叫剛才自己製作的IP核。建立好工程後先不新增原始檔。在“Flow Navigator”的“Settings”中選中“IP”下的“Repository”,點選“+”新增,路徑指定到剛才封裝IP核的目錄。點選ok後便會彈出一個框提示找到了一個名為“Add_USR_IP_v1_0”的IP核,也就是剛才建立的加法器。

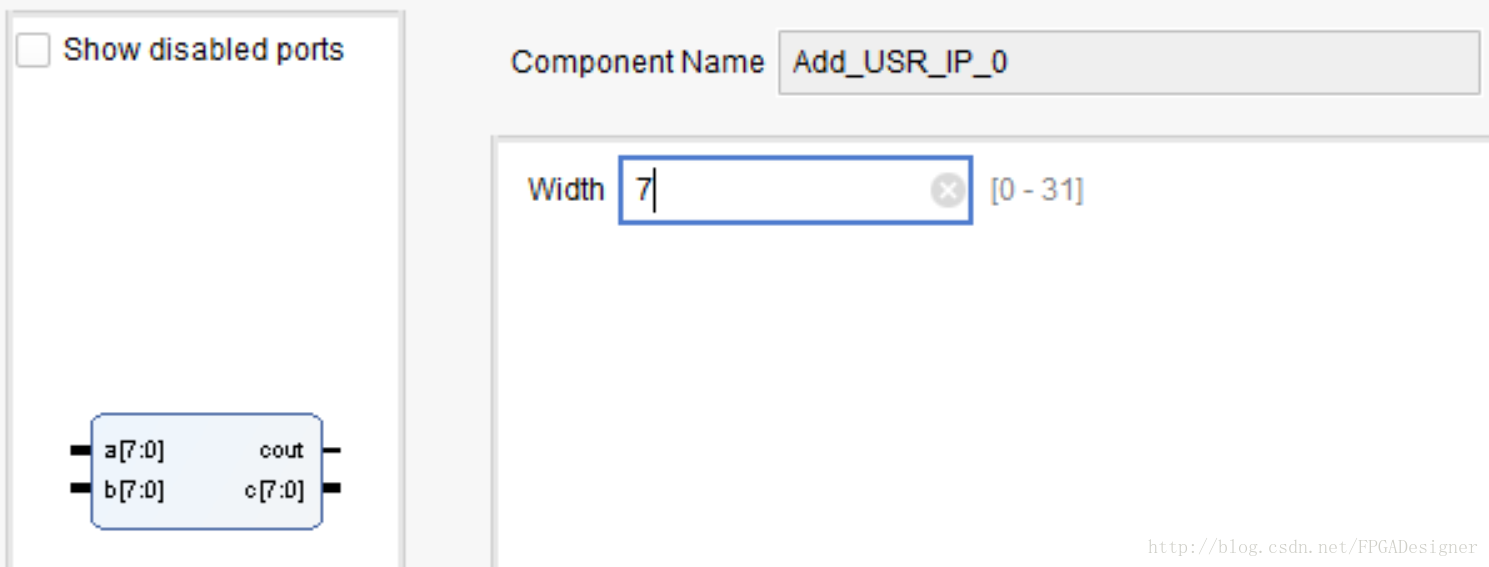

設定好後在“IP Integrator”中點選“Create Block Design”,建立一張原理圖。原理圖中點選“+”搜尋Add_USR_IP_v1_0,即可看到自己製作的IP核,雙擊新增到原理圖中。如果設計中還需要其它IP核,新增IP後用連線連線起整個系統即可。雙擊IP核圖形,即可彈出配置介面,可以更改加法器的位寬。

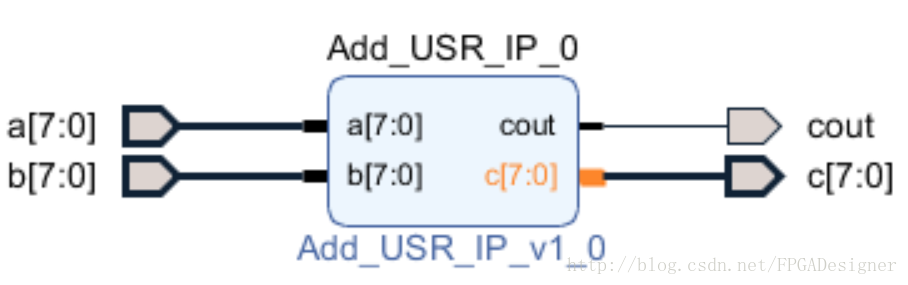

這裡我們不使用其它IP,直接在Add_USR_IP_v1_0的管腳上右鍵,點選“Make External”生成管腳訊號。結果如下:

在“Design Sources”中我們將看到bd字尾的原理圖檔案。為了使用方便,儲存原理圖後我們在檔案上點右鍵,點選“Create HDL Wrapper”,軟體會將原理圖封裝為一個Verilog檔案,這個Verilog檔案可以供其它模組呼叫。結果如下所示:

設計好後可以像普通的工程一樣綜合、實現、生成bit流。值得一提的是,在這個工程中我們是無法檢視到Add_USR_IP_v1_0這個IP核的原始碼的,它是一個黑盒的狀態。這也是Vivado提供的IP加密技術,以保護設計者的權益。