[2]Vivado中非同步FIFO的實現和使用

阿新 • • 發佈:2019-02-16

FIFO應用:

1、

1、

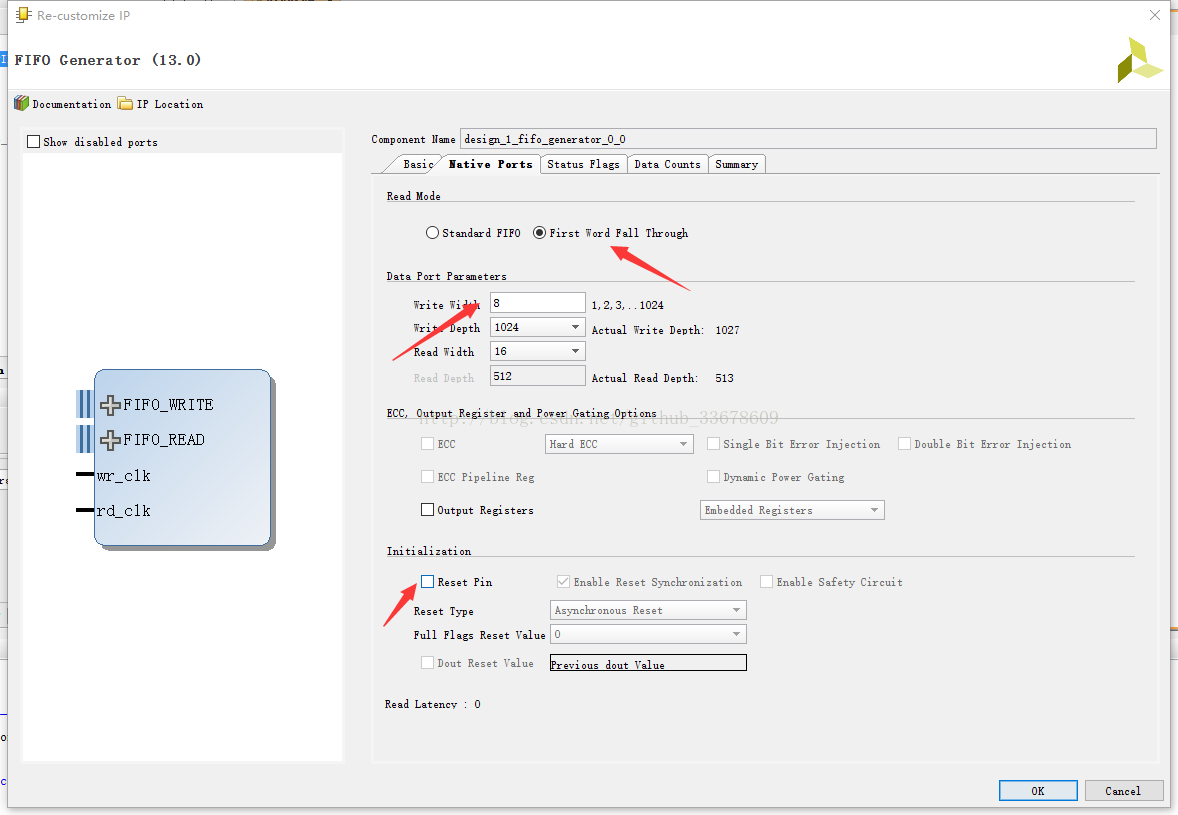

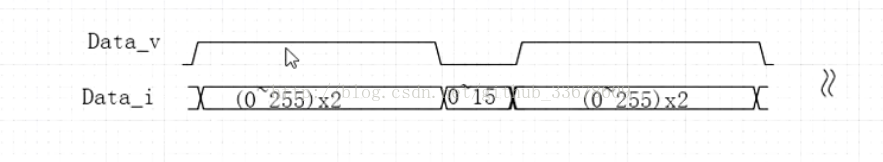

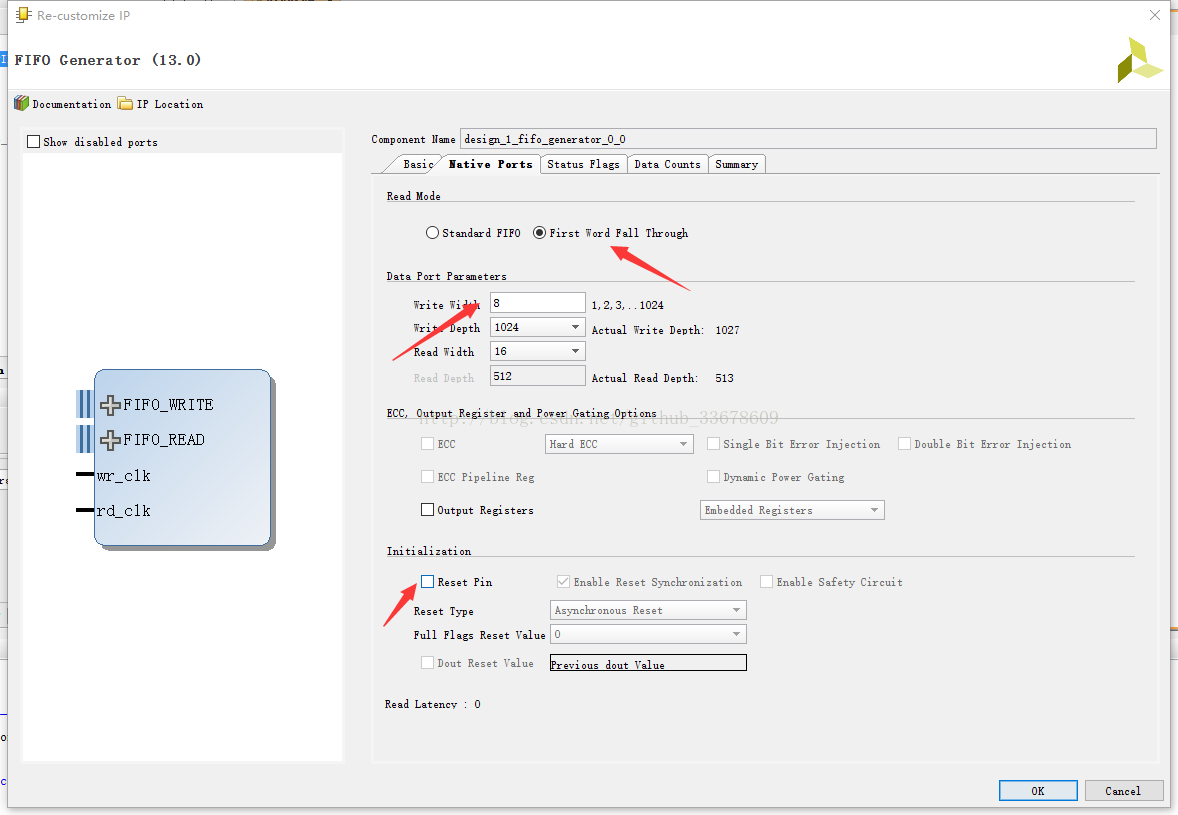

2、standard FIFO read mode讀取時會延遲一個週期時鐘,first word fall through read mode 讀取時沒有延時時鐘週期,給使能就有資料,read latency=0。

3、

read data count表示fifo中有多少個數據了。

- 1、在千兆乙太網資料寫入,往DDR3裡面寫資料時候

- 2、AD取樣時鐘和內部時鐘不同時,需要FIFO進行轉換

- 3、同頻異相時也需要用FIFO進行轉換

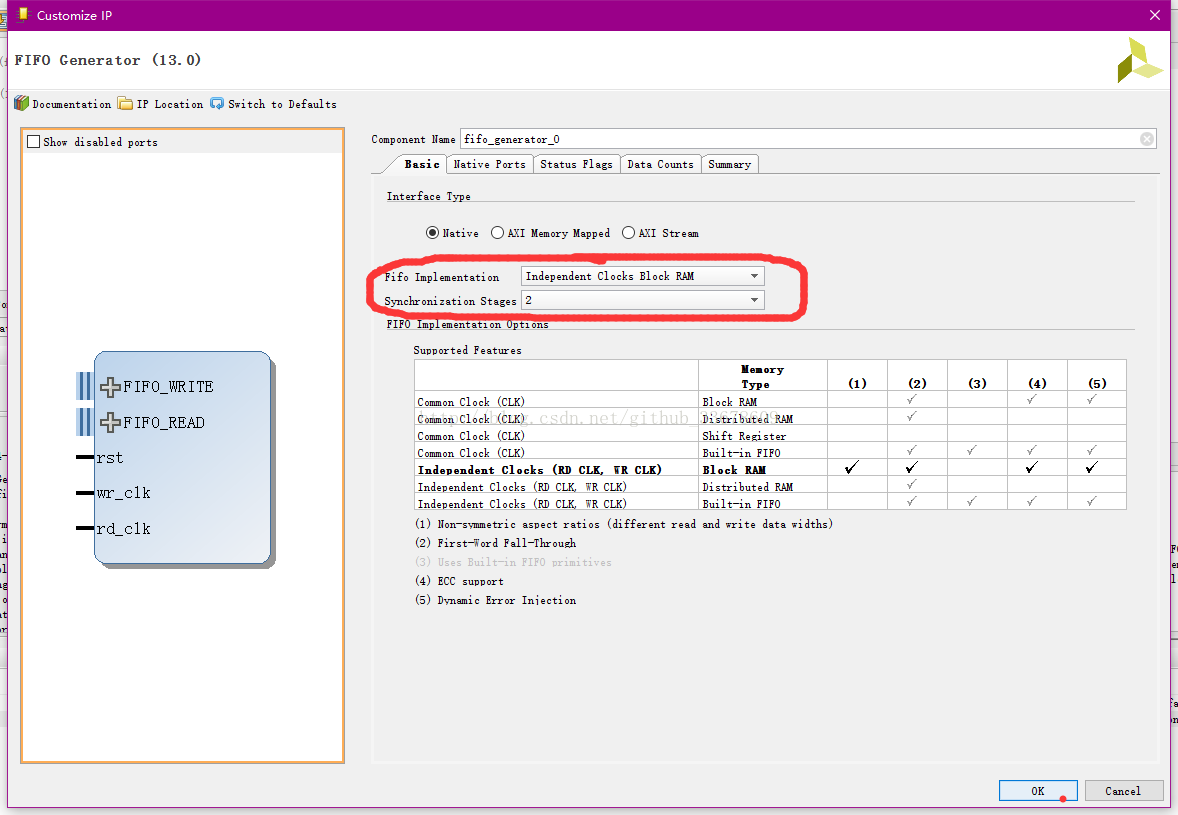

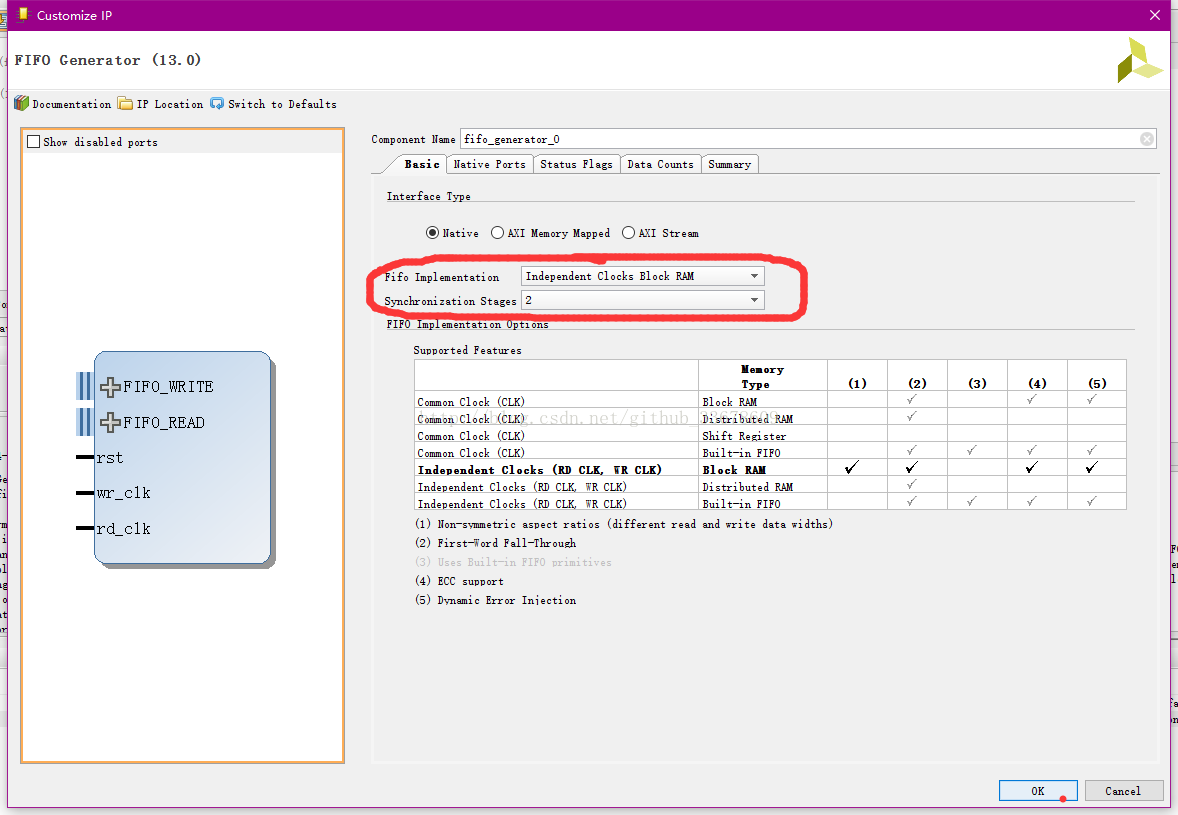

Vivado中FIFO generator的配置方法

2、standard FIFO read mode讀取時會延遲一個週期時鐘,first word fall through read mode 讀取時沒有延時時鐘週期,給使能就有資料,read latency=0。

3、

read data count表示fifo中有多少個數據了。

非同步FIFO實現

具體實現程式碼:

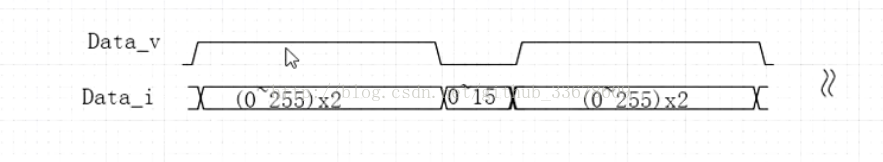

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date: 2016/08/10 14:42:33 // Design Name: // Module Name: fifo_timing // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // ////////////////////////////////////////////////////////////////////////////////// module fifo_timing( input wire sclk, input wire rst_n, input wire r_clk, input wire data_v, input wire [7:0] data_in, output wire data_ov, output wire [15:0] data_out, output wire fifo_w_clk, output wire fifo_r_clk, output wire fifo_w_en, output wire [7:0] fifo_w_data, input wire fifo_full, output wire fifo_r_en, input wire [15:0] fifo_r_data, input wire fifo_empty, input wire [8:0] fifo_rd_count ); wire full; wire empty; // r_clk reg r_flag; wire [8:0] rd_data_count; reg [8:0] r_cnt; wire rd_en; assign fifo_w_clk = sclk; assign fifo_r_clk = r_clk; assign fifo_w_en = data_v & (~fifo_full); assign fifo_w_data = data_in; assign fifo_r_en = r_flag & (~fifo_empty); assign data_out = fifo_r_data; assign data_ov = r_flag; assign rd_en = r_flag; always @(posedge r_clk or negedge rst_n) if(rst_n == 1'b0) r_flag <= 1'b0; else if(r_flag == 1'b1 && r_cnt == 'd255 ) r_flag <= 1'b0; else if(fifo_rd_count >= 'd255 && r_flag == 1'b0) r_flag <= 1'b1; always @(posedge r_clk or negedge rst_n) if(rst_n == 1'b0) r_cnt <='d0; else if(r_flag == 1'b1) r_cnt <= r_cnt + 1'b1; else r_cnt <='d0; assign data_ov = r_flag; endmodule