Android+高通 MIPI轉LVDS顯示屏除錯之---基於SD65DSI84

阿新 • • 發佈:2019-02-17

1.硬體介面

顯示屏解析度是1920×RGB×1080 pixels。

1.1 硬體連線示意圖

1.2 硬體連線引腳

CPU | SN65DSI84 DSI轉LVDS | LM3492HCMH 背光控制IC | 顯示屏 |

GPIO126_LCD_1V8_EN | VCC | ||

GPIO129_LCD_5V_EN | 5V_BL | ||

GPIO125_LCD_COMM | COMM | ||

MPP2_LCD_BL_PWM | DIM1/CLK | ||

GPIO123_LCD_DIM2 | DIM2 | ||

GPIO7_LCD_I2C2_SCL | SCL | ||

GPIO6_LCD_I2C2_SDA | SDA | ||

GPIO124_LVDS_INT | IRQ | ||

GPIO130_LVDS_EN | EN |

2.SD65DSI84

The SN65DSI8x can be used between a GPU with DSI output and a video panel with LVDS inputs,MIPI DSI-to-LVDS

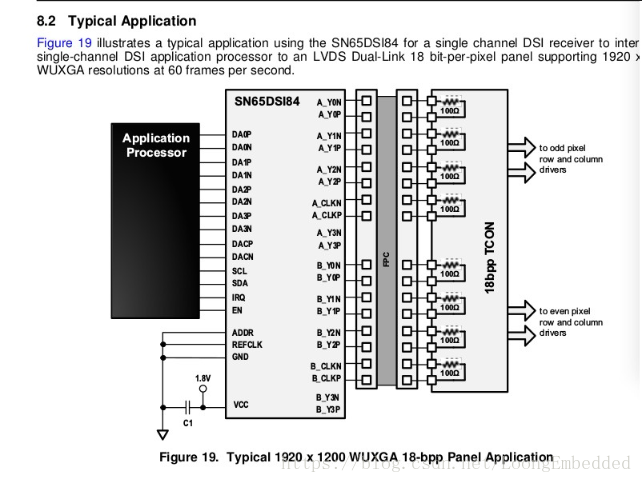

SN65DSI84 非常適合於每秒 60 幀的 WUXGA 1920 x 1200 應用,每畫素位元位高達 24。 執行了部分線路緩衝以適應 DSI 與 LVDS 介面間的資料流不匹配。

2.1 SN65DSI84的主要特徵

(1)單DSI接收通道,可配置為使用1~4個D-PHY資料通道,每個資料通道最高可工作在1Gbps。

(2)支援18bpp(RGB666)和24bpp(RGB888)資料格式的DSI視訊包。

(3)支援低壓差分信令(LVDS)單通道DSI 至雙鏈路LVDS 橋 (Rev. E)

(4)LVDS輸出時鐘範圍為25MHz~154MHz。

(5)低功耗特性包括關斷 (SHUTDOWM) 模式、精簡 LVDS 輸出電壓擺幅、共模和 MIPI® 超低功耗狀態 (ULPS,ultra-low power state,超低功耗) 支援

2.2 復位晶片

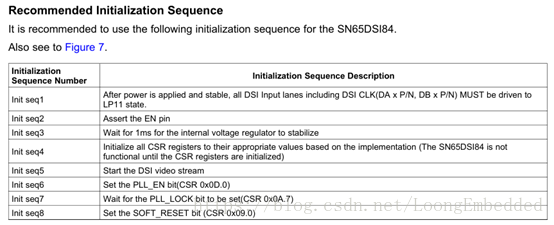

2.3 SN65DSI84推薦的初始化時序

2.4 時鐘配置和倍頻器

(2)採用外部參考時鐘源

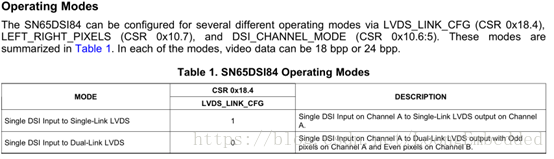

2.5 SN65DSI84的工作模式

工作模式由DSI和LVDS通道的使用數量與CSR暫存器配置的DSI資料輸入選項來決定。

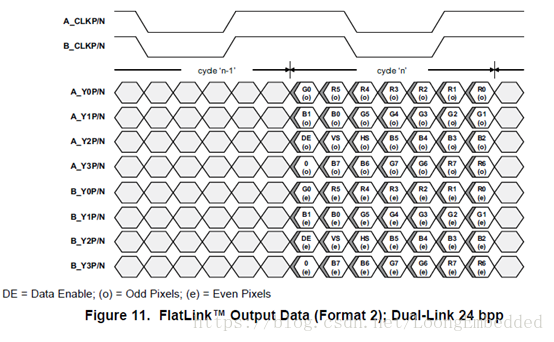

2.6 LVDS輸出格式

當使用雙通道配置,通道A傳輸奇數畫素資料,通道B傳輸偶數畫素資料when

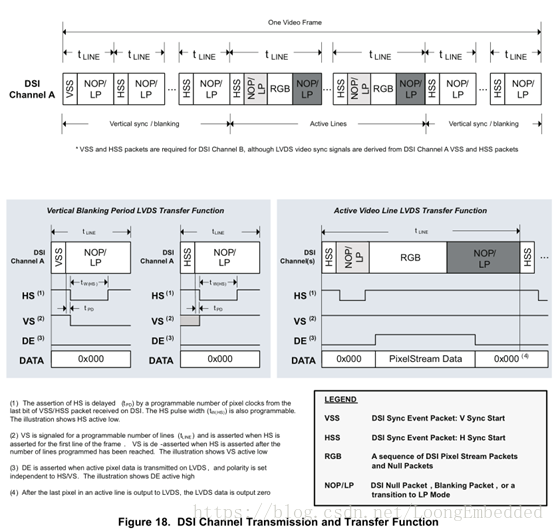

SN65DSI84處理DSI包和以工業標準格式來產生視訊資料驅動LVDS介面,上圖這是我們產品使用的視訊資料格式。

2.7 DSI lane資料合併

我們採用4路DSI資料通道。

2.8 DSI 畫素流包

2.9 DSI視訊傳輸規範

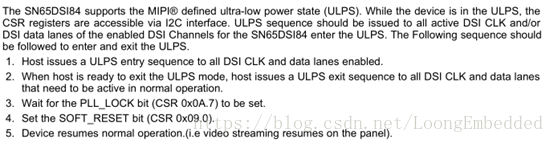

2.10ULPS

LVDS的輸出時序由CSR暫存器對應的視訊引數來產生。HSync pulse width, HSync Back Porch duration,and VSync pulse width.這些值需要變成用來建立LVDS顯示屏的時序。

2.11LVDS模式生成

此特徵可用來測試LVDS輸出路徑和LVDS面板。

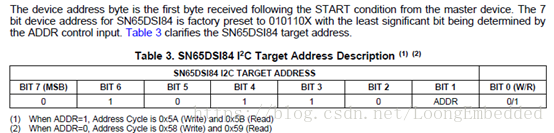

2.12SN65DSI84的I2C地址

我們硬體設定是ADDR引腳通過下拉電阻接地,也就是ADDR=0,所以I2C寫地址為0x58,讀地址為0x59,但在程式碼裡I2C從裝置地址為0x2C,採用前7位作為I2C從裝置的地址。