Xilinx A7 晶片內部結構分析(1)-- CLB

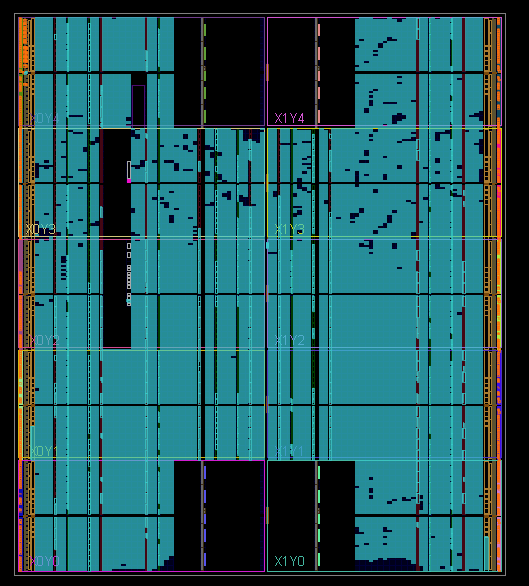

一直以來,覺得自己關於FPGA方面,摸不到“低”——對底層架構認識不清,夠不著“高”——沒真正獨立做過NB的應用,如高速、複雜協議或演算法、神經網路加速等高大上的應用,所以能力和認識水平都處於中間水平。這段時間做時序優化,感覺心有餘而力不足了,可能要觸及手動佈局佈線了,開啟Device佈局圖才開始有興趣探究一些底層結構的東西。

可能翻開任何一本有關FPGA的書籍,上來就會介紹FPGA的歷史,原理,內部結構什麼的,大部分人看著都極其枯燥,常常要麼直接略過,要麼就看一遍,久了也就忘記了(部分靠翻譯文件的書作者該好好反思)。我硬著頭皮去彌補之前缺失的一些基礎知識,結合Xilinx A7 晶片,總結一下自己的收穫。

1. 總覽

平臺:Vivado

晶片:XC7A200

FPGA主要有六部分組成:可程式設計輸入輸出單元、可程式設計邏輯單元、完整的時鐘管理、嵌入塊狀RAM、佈線資源、內嵌的底層功能單元和內嵌專用硬體模組。其中最為主要的是可程式設計輸出輸出單元、可程式設計邏輯單元和佈線資源。

2. 可配置邏輯單元

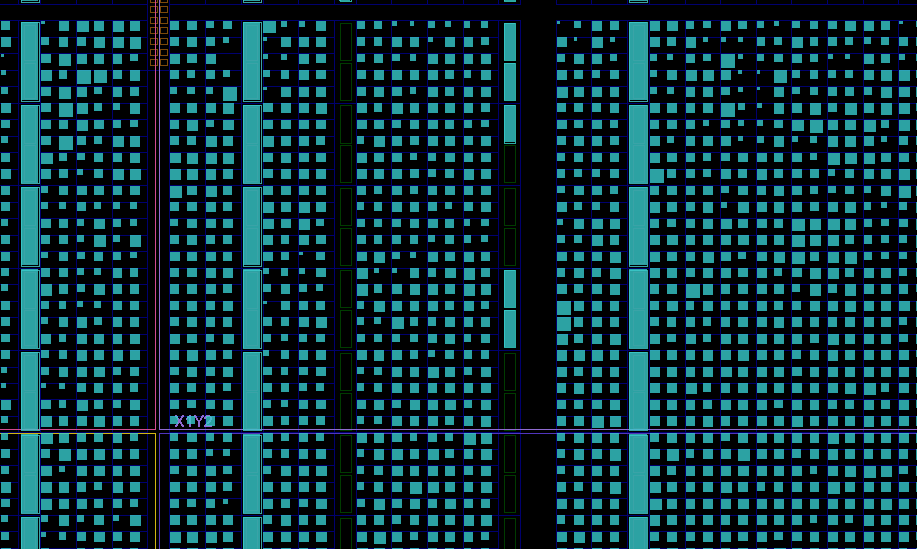

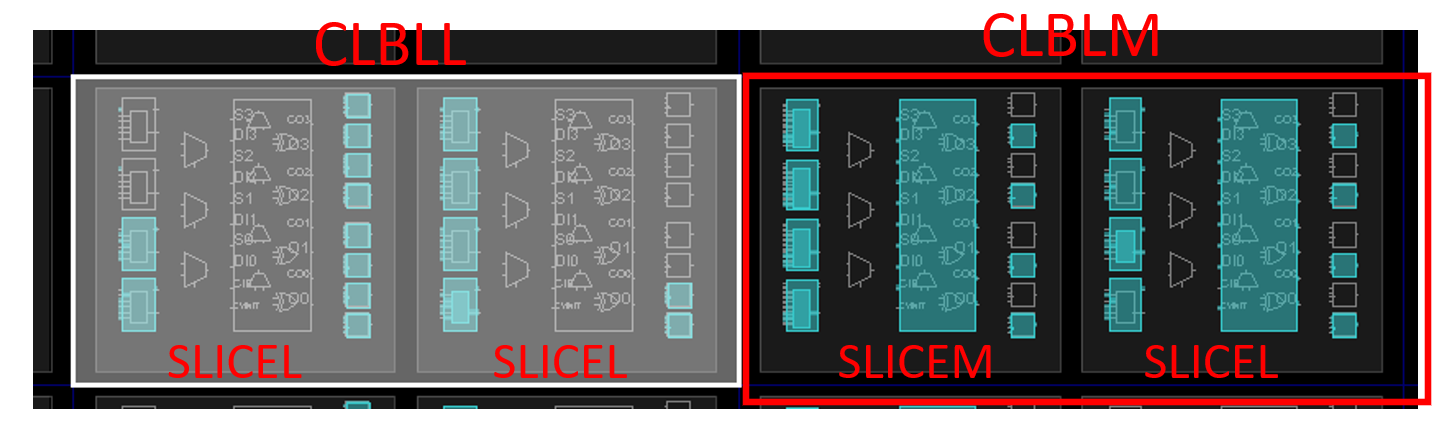

可配置邏輯單元(Configurable Logic Block,CLB)在FPGA中最為豐富,由兩個SLICE組成。由於SLICE有SLICEL(L:Logic)和SLICEM(M:Memory)之分,因此CLB可分為CLBLL和CLBLM兩類。

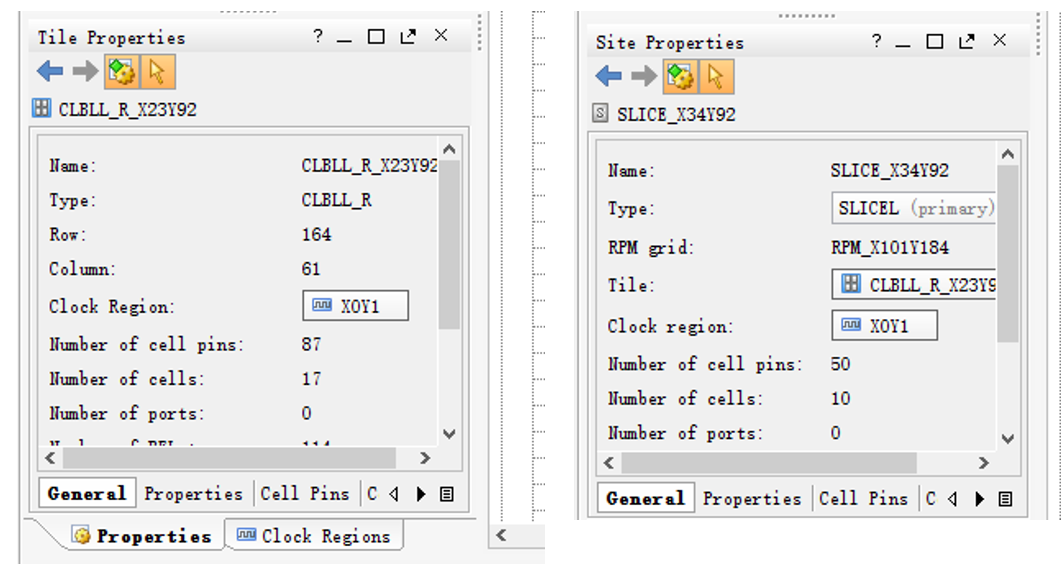

點選內部的邏輯單元,通過陰影區別包含的範圍,你可以清晰的看到結構劃分的層級。在旁邊視窗可以清晰的看到選中部分的屬性(Properties)。

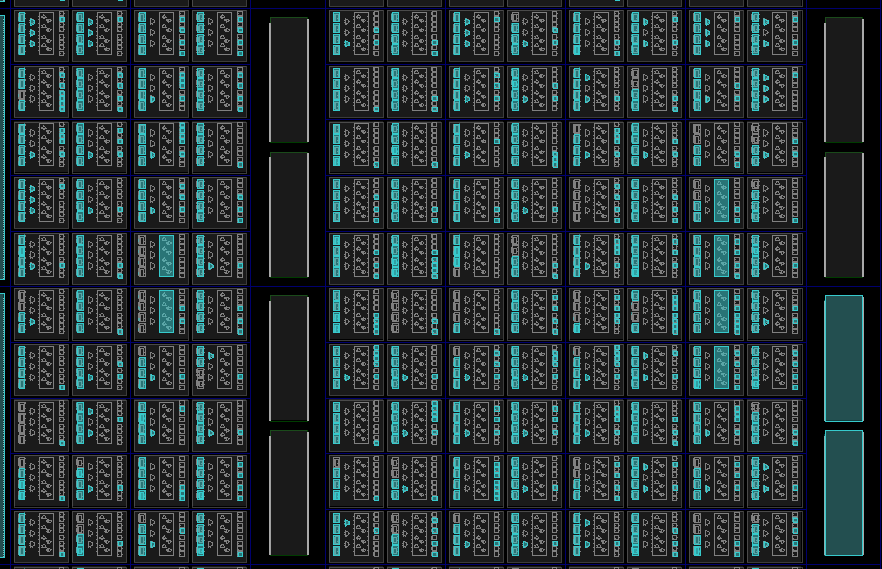

來,再放大,放大到一個SLICEL,如下圖所示。

SLICEL和SLICEM內部都包含4個6輸入查詢表(Look-Up-Table,LUT6)、3個數據選擇器(MUX)、1個進位鏈(Carry Chain)和8個觸發器(Flip-Flop),下面分部分介紹的時候,時不時可以再回頭看這張結構圖。

2.1 LUT6

雖然SLICEL和SLICEM的結構組成一樣,但兩者更細化的結構上略有不同,區別在於LUT6上(如下圖所示),從而導致LUT6的功能有所不同(如下表格所示)。

| LUT功能 | SLICEL | SLICEM |

|---|---|---|

| 邏輯函式發生器 | v | v |

| ROM | v | v |

| 分散式RAM | v | |

| 移位暫存器 | v |

上邊的功能可以看到,不論是SLICEL還是SLICEM,他們的LUT6都可以作為ROM使用,配置為64x1(佔用1個LUT6,64代表深度,1代表寬度)、128x1(佔用2個LUT6)和256(佔用4個LUT6)的ROM。

另外既然SLICEM中的M代表memory的意思,所以增加了更多儲存功能。可以配置為RAM,尤其指分散式RAM。其中RAM的寫操作為同步,而讀操作是非同步的,即與時鐘訊號無關。如果要實現同步讀操作,則要額外佔用一個觸發器,從而增加了意識時鐘的延遲(Latency),但提升了系統的效能。這就解釋了為什麼我們實現RAM同步讀寫的時候,讀出輸出要延遲一個clk。一個LUT6可配置64x1的RAM,當RAM的深度大於64時,會佔用額外的MUX(F7AMUX,F7BMUX,F8MUX,即一個SLICE中的那3個MUX)。

SLICEM中的LUT還可以配置為移位暫存器,每個LUT6可實現深度為32的移位暫存器,且同一個SLICEM中的LUT6(4個)可級聯實現128深度的移位暫存器。

2.2 MUX

SLICE中的三個MUX(Multiplexer:F7AMUX,F7BMUX和F8MUX)可以和LUT6聯合共同實現更大的MUX。事實上,一個LUT6可實現4選1的MUX。

SLICE中的F7MUX(F7AMUX和F7BMUX)的輸入資料來自於相鄰的兩個LUT6的O6埠。

一個F7MUX和相鄰的兩個LUT6可實現一個8選1的MUX。因此,一個SLICE可實現2個8選1的MUX。

4個LUT6、F7AMUX、F7BMUX和F8MUX可實現一個16選1的MUX。因此,一個SLICE可實現一個16選1的MUX。

2.3 進位鏈(Carry Chain)

進位鏈用於實現加法和減法執行。就是結構圖中,中間那個大的部分,可以看到它內部實際還包含4個MUX和4個2輸入異或門(XOR)。

異或運算是加法運算中必不可少的運算。

2.4 觸發器

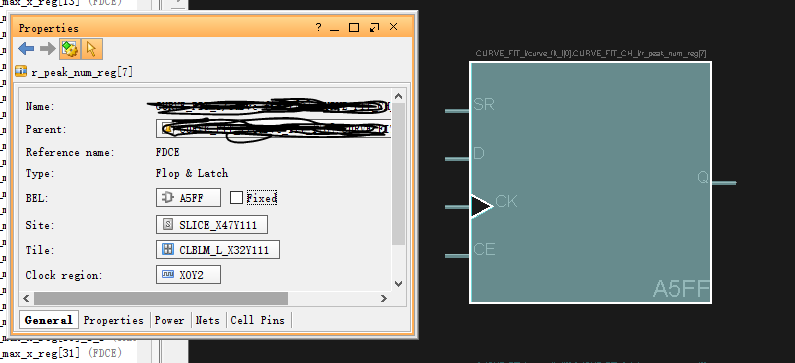

每個SLICE中有8個觸發器。這個8個觸發器可分為兩大類:4個只能配置為邊沿敏感的D觸發器(Flip-Flop)和4個即可配置為邊沿敏感的D觸發器又可配置為電平敏感的鎖存器(Flop&Latch)。當後者被用作鎖存器的時候,前者將無法使用。

當這8個觸發器都用作D觸發器時,他們的控制埠包括使能端CE、置位/復位埠S/R和時鐘埠CLK是對應共享的,也就是就是說共用的。{CE,S/R,CLK}稱為觸發器的控制集。顯然,在具體的設計中,控制集種類越少越好,這樣可以提高觸發器的利用率。那麼怎樣減少控制集種類呢?我的理解是:

- 減少時鐘種類,即頻率越少越好;

- 統一規範的設計邏輯,如復位。

S/R埠可配置為同步/非同步置位或同步/非同步復位,且高有效,因此可形成4種D觸發器,如下表所示。

| 原語(Primitive) | 功能描述 | 原語(Primitive) | 功能描述 |

|---|---|---|---|

| FDCE | 同步使能,非同步復位 | FDRE | 同步使能,同步復位 |

| FDPE | 同步使能,非同步置位 | FDSE | 同步使能,同步置位 |

在我們的常規設計中,FDCE和FDPE佔了絕大多數。

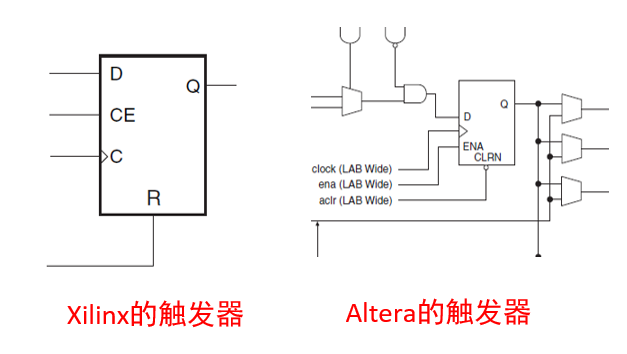

說到高有效,讓我想起了一個大家習以為常,但很少深究的問題:為什麼一開始接觸FPGA的時候,都告訴我們低電平復位?後來查了一些資料,有說從功耗、噪聲可靠性方面考慮等等,但是偶然看到Xilinx和Altera兩家晶片的觸發器不一樣!如下圖所示,Xilinx的觸發器是高電平復位,而Altera的觸發器時低電平復位。所以這也是需要考慮的一點嗎?

參考文獻:

- 《7 Series FPGAs Configurable Logic Block》(UG474)

- 《VIVADO從此開始》——高亞軍著(強烈推薦此書!!!!本部落格論述部分大多來自高老師的書)