arm異常中lr儲存pc的情況

移植程式碼中存在的很多問題比如中斷的關閉和開啟,任務級別的情景切換,中斷到任務的情景切換都是我們在平時移植中講到,我也不在此強調了。在官網中提供的移植過程中存在異常處理機制,這個本不是在移植過程中考慮的,但是文件中確實提供了一個比較好的處理方式。我在此對這一段時間的學習做一個總結。

首先需要了解ARM的異常處理機制,異常是每一種處理器都必須考慮的問題之一,關鍵在於如何讓處理,返回地址在什麼位置都是需要考慮的,

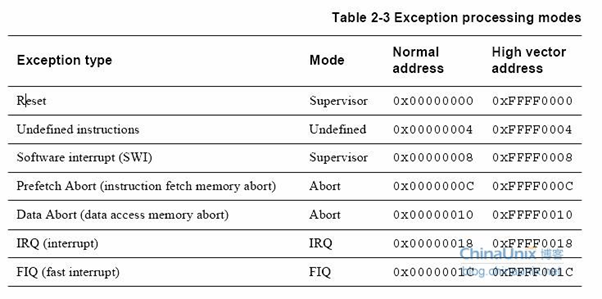

ARM中支援7種異常,其中包括復位、未定義指令異常、軟中斷異常、預取指令中止、資料中止、IRQ、IFQ。每一種異常執行在特定的處理器模式下。我在此逐一的分析。

一般異常發生後,CPU都會進行一系列的操作,這些操作有一部分是CPU自動完成,有一部分是需要我們程式設計師完成。

首先說明CPU會自動完成的部分,用ARM結構手冊中的程式碼描述如下:

R14_= return link //這個可以參看暫存器的說明,兩個作用

SPSR_<exception_mode > = CPSR

CPSR[4:0]= exception mode number

CPSR[5]= 0 ; //AEM指令

If==Reset or Fiq then //只有在復位和FIQ模式下才會關閉FIQ中斷

CPSR[6] = 1 ;

CPSR[7]= 1 ; //任何異常模式下都會關閉IRQ中斷

PC= exception vector address

從上面的程式碼中我們可以發現CPU自動處理的過程包括如下:

1、 拷貝CPSR到SPSR_

2、 設定適當的CPSR位: 改變處理器狀態進入ARM狀態;改變處理器模式進入相應的異常模式;設定中斷禁止位禁止相應中斷。

3、 更新LR_,這個暫存器中儲存的是異常返回時的連結地址

4、 設定PC到相應的異常向量

以上的操作都是CPU自動完成,異常的向量表如下:

返回地址問題

異常的返回地址也是需要我們注意的地方,不同的異常模式返回地址也是存在差異的,這主要是因為各種異常產生的機理存在差別所導致的。這樣我們的需要在異常進入處理函式之前或者在返回時調整返回地址,一般採用進入異常處理函式前進行手動調整。下面每一種異常R14儲存的值都給了出來,其中也包含了CPU自動處理的部分,根據儲存的R14就可以知道怎樣實現地址的返回。

復位異常:

可以看出該模式下的先對來說返回地址也比較簡單,不需要做太多的描述。

未定義的指令異常:

MOVS PC, R14

軟中斷異常:

返回的方式也比較簡單:

MOVS PC, R14

預取指令中止異常:

返回需要做下面的調整:

SUBS PC, R14, #4

資料中止

返回地址需要做下面的調整:

如果需要重新訪問資料則:

SUBS PC, R14, #8

如果不需要重新訪問資料則:

SUBS PC, R14, #4

IRQ中斷的處理過程:

返回地址需要做下面的調整:

SUBSPC,R14,#4

IFQ中斷:

返回地址需要做下面的調整:

SUBS PC, R14 ,#4

從上面的程式碼可以知道,對於每一種異常,儲存的返回地址都是不一樣的,一般都需要我們手動的跳轉,當然調整的時機也需要我們選擇,是在進入處理前跳轉還是返回時調整都是需要我們程式設計師控制的。

在ARM Developer Suite DeveloperGuide中對ARM處理器的異常處理操作提供能更加詳細的解釋,每一種異常下的處理方式如下文描述:

異常返回時另一個非常重要的問題是返回地址的確定,在前面曾提到進入異常時處理器會有一個儲存LR 的動作,但是該儲存值並不一定是正確的返回地址,下面以一個簡單的指令執行流水狀態圖來對此加以說明。

我們知道在ARM 架構裡,PC值指向當前執行指令的地址加8處,也就是說, 當執行指令A(地址0x8000)時,PC 等於指令C 的地址(0x8008)。假如指令A 是“BL”指令,則當執行該指令時,會把PC(=0x8008)儲存到LR 暫存器裡面,但是接下去處理器會馬上對LR 進行一個自動的調整動作:LR=LR-0x4。這樣,最終儲存在 LR 裡面的是 B 指令的地址,所以當從 BL 返回時,LR 裡面正好是正確的返回地址。同樣的調整機制在所有LR自動儲存操作中都存在,比如進入中斷響應時,處理器所做的LR 儲存中,也進行了一次自動調整,並且調整動作都是LR=LR-0x4。

下面,我們對不同型別的異常的返回地址依次進行說明:

假設在指令A 處(地址0x8000)發生了異常,進入異常響應後,LR 上經過調整儲存的地址值應該是B 的地址0x8004。

1、 如果發生的是軟體中斷,即A 是“SWI”指令

異常是由指令本身引起的,從 SWI 中斷返回後下一條執行指令就是B,正好是LR 暫存器儲存的地址, 所以只要直接把LR 恢復給PC。

MOVS pc,lr

2、 發生的是Undefinedinstruction異常

異常是由指令本身引起的,從異常返回後下一條執行指令就是B,正好是LR 暫存器儲存的地址, 所以只要直接把LR 恢復給PC。

MOVS pc,lr

3、 發生的是IRQ或FIQ中斷

因為指令不可能被中斷打斷,所以A指令執行完以後才能響應中斷,此時PC已更新,指向指令D的地址(地址0x800C),LR 上經過調整儲存的地址值是C 的地址0x8008。中斷返回後應該執行B指令,所以返回操作是:

SUBS pc,lr, #4

4、 發生的是Prefetch Abort異常

該異常並不是處理器試圖從一個非法地址取指令時觸發,取出的指令只是被標記為非法,按正常處理流程放在流水線上,在執行階段觸發Prefetch Abort異常,此時LR 上經過調整儲存的地址值是B 的地址0x8004。異常返回應該返回到A指令,嘗試重新取指令,所以返回操作是:

SUBS pc,lr, #4

5、 發生的是“Data Abort”

CPU訪問儲存器時觸發該異常,此時PC指向指令D的地址(地址0x800C),LR 上經過調整儲存的地址值是C 的地址0x8008。異常返回後,應回到指令A,嘗試重新操作儲存器,所以返回操作是:

SUBS pc,lr, #8

以上就是ARM異常的CPU操作部分,接下來就是程式設計師應該完成的操作。

1. 由於CPU會自動跳轉到對應的異常向量中,因此只需要在在各個異常向量中存放對應的操作,最簡單的都是存放一個B指令跳轉到對應的異常處理函式的操作即可。但由於B指令的跳轉返回只有+-32M,而異常處理函式的地址可能會超過+-32M,因此可以採用另一種方式實現方式:在異常向量中儲存一條指令LDR PC[addr],其中的addr中就儲存了異常處理函式的地址,當然addr的相對地址要小於+-32M。這樣也就解決了跳轉範圍的問題。

2. 接下來就是異常處理函式對應的操作,可以在進入異常處理之前就進行返回地址的調整,這樣後面就不用進行處理啦,當然也可以在返回過程中再調整。一般都是在這個過程中進行調整。進行壓棧操作,儲存對應的環境變數。呼叫實際的處理過程等。

3. 出棧,恢復CPU的狀態和暫存器的值。由於第一步中已經調整好返回地址,這一步不需要再次調整。當然如果之前沒有調整,這裡則需要進行相應的調整。

在uC/OS-II的官網移植中採用通用異常處理函式的方式實現異常的處理,下面我們來分析其中的部分程式碼:

首先是處理器部分的移植,包括異常向量、異常的ID號,儲存異常處理函式地址的地址等:

/*ARM的異常ID號,支援7種類型的異常,每一種異常都存在一個ID號*/

#define OS_CPU_ARM_EXCEPT_RESET 0x00

#define OS_CPU_ARM_EXCEPT_UNDEF_INSTR 0x01

#define OS_CPU_ARM_EXCEPT_SWI 0x02

#define OS_CPU_ARM_EXCEPT_PREFETCH_ABORT 0x03

#define OS_CPU_ARM_EXCEPT_DATA_ABORT 0x04

#define OS_CPU_ARM_EXCEPT_ADDR_ABORT 0x05

#define OS_CPU_ARM_EXCEPT_IRQ 0x06

#define OS_CPU_ARM_EXCEPT_FIQ 0x07

#define OS_CPU_ARM_EXCEPT_NBR 0x08

/*異常向量地址*/

#define OS_CPU_ARM_EXCEPT_RESET_VECT_ADDR (OS_CPU_ARM_EXCEPT_RESET * 0x04 + 0x00) //0x00

#define OS_CPU_ARM_EXCEPT_UNDEF_INSTR_VECT_ADDR (OS_CPU_ARM_EXCEPT_UNDEF_INSTR * 0x04 + 0x00) //0x04

#define OS_CPU_ARM_EXCEPT_SWI_VECT_ADDR (OS_CPU_ARM_EXCEPT_SWI * 0x04 + 0x00) //0x08

#define OS_CPU_ARM_EXCEPT_PREFETCH_ABORT_VECT_ADDR (OS_CPU_ARM_EXCEPT_PREFETCH_ABORT * 0x04 +0x00) //0x0c

#define OS_CPU_ARM_EXCEPT_DATA_ABORT_VECT_ADDR (OS_CPU_ARM_EXCEPT_DATA_ABORT * 0x04 + 0x00) //0x10

/*這個異常是ARM中不支援的異常*/

#define OS_CPU_ARM_EXCEPT_ADDR_ABORT_VECT_ADDR (OS_CPU_ARM_EXCEPT_ADDR_ABORT * 0x04 + 0x00) //0x14

#define OS_CPU_ARM_EXCEPT_IRQ_VECT_ADDR (OS_CPU_ARM_EXCEPT_IRQ * 0x04 + 0x00) //0x18

#define OS_CPU_ARM_EXCEPT_FIQ_VECT_ADDR (OS_CPU_ARM_EXCEPT_FIQ * 0x04 + 0x00) //0x1c

/*儲存異常處理函式地址的地址*/

/* ARMexception handlers addresses */

#define OS_CPU_ARM_EXCEPT_RESET_HANDLER_ADDR (OS_CPU_ARM_EXCEPT_RESET * 0x04 + 0x20) //0x20

#define OS_CPU_ARM_EXCEPT_UNDEF_INSTR_HANDLER_ADDR (OS_CPU_ARM_EXCEPT_UNDEF_INSTR * 0x04 + 0x20) //0x24

#define OS_CPU_ARM_EXCEPT_SWI_HANDLER_ADDR (OS_CPU_ARM_EXCEPT_SWI * 0x04 + 0x20) //0x28

#define OS_CPU_ARM_EXCEPT_PREFETCH_ABORT_HANDLER_ADDR (OS_CPU_ARM_EXCEPT_PREFETCH_ABORT * 0x04 +0x20) //0x2c

#define OS_CPU_ARM_EXCEPT_DATA_ABORT_HANDLER_ADDR (OS_CPU_ARM_EXCEPT_DATA_ABORT * 0x04 + 0x20) //0x30

#define OS_CPU_ARM_EXCEPT_ADDR_ABORT_HANDLER_ADDR (OS_CPU_ARM_EXCEPT_ADDR_ABORT * 0x04 + 0x20) //0x34

#define OS_CPU_ARM_EXCEPT_IRQ_HANDLER_ADDR (OS_CPU_ARM_EXCEPT_IRQ * 0x04 + 0x20) //0x38

#define OS_CPU_ARM_EXCEPT_FIQ_HANDLER_ADDR (OS_CPU_ARM_EXCEPT_FIQ * 0x04 + 0x20) //0x3c

/*儲存在異常向量中的內容,實質上是LDR PC,[PC,#0x18]的機器碼*/

#define OS_CPU_ARM_INSTR_JUMP_TO_SELF 0xEAFFFFFE

/* ARM"Jump To Exception Handler" asm instruction */

異常的初始化函式,首先,完成了在異常向量中儲存指令的操作,採用機器碼的形式就能避免直接訪問暫存器什麼的,其次,完成在固定的地址處存放對應異常處理函式的地址。其中採用了賦值的形式也是需要注意的,採用的強制型別轉換和指標相結合的形式。保證了是修改地址處的內容。而不是修改地址。

/*初始化異常中斷向量*/

void OS_CPU_InitExceptVect (void)

{

/*

OS_CPU_ARM_EXCEPT_UNDEF_INSTR_VECT_ADDR是對應中斷向量表的地址

OS_CPU_ARM_INSTR_JUMP_TO_HANDLER是儲存了對應的OS_CPU_ARM_INSTR_JUMP_TO_HANDLER(實質上是一個指令)

實質上就是在異常向量中存放了:LDR PC [PC, #0x18],也就是讓PC指向對應的異常處理地址中的內容,

也就是實現到實際處理函式的跳轉。

異常處理地址中儲存了實際的異常處理函式的地址

其他的異常也有相同的操作,OS_CPU_ARM_INSTR_JUMP_TO_HANDLER是一個指令的機器碼形式

*/

(*(INT32U*)OS_CPU_ARM_EXCEPT_UNDEF_INSTR_VECT_ADDR) = OS_CPU_ARM_INSTR_JUMP_TO_HANDLER;

(*(INT32U*)OS_CPU_ARM_EXCEPT_UNDEF_INSTR_HANDLER_ADDR) = (INT32U)OS_CPU_ARM_ExceptUndefInstrHndlr;

(*(INT32U *)OS_CPU_ARM_EXCEPT_SWI_VECT_ADDR) = OS_CPU_ARM_INSTR_JUMP_TO_HANDLER;

(*(INT32U*)OS_CPU_ARM_EXCEPT_SWI_HANDLER_ADDR) = (INT32U)OS_CPU_ARM_ExceptSwiHndlr;

(*(INT32U*)OS_CPU_ARM_EXCEPT_PREFETCH_ABORT_VECT_ADDR) = OS_CPU_ARM_INSTR_JUMP_TO_HANDLER;

(*(INT32U*)OS_CPU_ARM_EXCEPT_PREFETCH_ABORT_HANDLER_ADDR) =(INT32U)OS_CPU_ARM_ExceptPrefetchAbortHndlr;

(*(INT32U*)OS_CPU_ARM_EXCEPT_DATA_ABORT_VECT_ADDR) = OS_CPU_ARM_INSTR_JUMP_TO_HANDLER;

(*(INT32U*)OS_CPU_ARM_EXCEPT_DATA_ABORT_HANDLER_ADDR) = (INT32U)OS_CPU_ARM_ExceptDataAbortHndlr;

(*(INT32U *)OS_CPU_ARM_EXCEPT_ADDR_ABORT_VECT_ADDR) = OS_CPU_ARM_INSTR_JUMP_TO_HANDLER;

(*(INT32U*)OS_CPU_ARM_EXCEPT_ADDR_ABORT_HANDLER_ADDR) = (INT32U)OS_CPU_ARM_ExceptAddrAbortHndlr;

(*(INT32U*)OS_CPU_ARM_EXCEPT_IRQ_VECT_ADDR) = OS_CPU_ARM_INSTR_JUMP_TO_HANDLER;

(*(INT32U*)OS_CPU_ARM_EXCEPT_IRQ_HANDLER_ADDR) = (INT32U)OS_CPU_ARM_ExceptIrqHndlr;

/*在異常向量中儲存對應的操作,實質上就是將PC值調轉*/

(*(INT32U*)OS_CPU_ARM_EXCEPT_FIQ_VECT_ADDR) = OS_CPU_ARM_INSTR_JUMP_TO_HANDLER;

(*(INT32U*)OS_CPU_ARM_EXCEPT_FIQ_HANDLER_ADDR) = (INT32U)OS_CPU_ARM_ExceptFiqHndlr;

}

|

異常型別 |

Mode |

異常向量 |

內容 |

|

IFQ異常 |

IFQ |

0x0000001C |

LDR PC,[PC,#0x18] 0xE59FF018 |

|

0x00000038 |

Address of OS_CPU_ARM_ExceptIrqHndlr() |

||

|

0x0000003C |

Address of OS_CPU_ARM_ExceptFiqHndlr() |

有必要的討論一下,為什麼在向量中儲存的是指令: LDR PC,[PC,#0x18],我們從上面的地址可以知道,IRQ異常處理函式地址被儲存到了0x00000038中,異常向量與該地址之間的差值是0x20,那麼為什麼在其中儲存的值只是0x18呢?這還要討論ARM的流水線結構,當前執行的命令相比PC指向的地址差0x08。也就是當前執行的指令的地址是PC-0x08.當PC指向異常向量以後(取值),還需要等待一個時鐘(譯碼)之後才會被執行(真正意義上的執行操作),而這時PC值已經被更新了。指向了Vector+0x8的位置,因此我們可以知道,當執行向量中的程式碼時,這時PC=Vector+0x8,而這時相對於固定的0x20-0x08=0x18,這也就是為什麼是LDRPC,[PC,#0x18],而不是LDR PC,[PC,#0x20].

採用上面的例子說明IRQ的向量為0x00000018,而設定好的固定地址用來儲存對應異常處理函式地址的地址是0x00000038,當CPU執行完PC =0x00000018以後,還需要譯碼、才能被執行,這時候PC值已經更新為PC =0x00000018 + 0x08;這時候固定地址距離PC的相對位置位0x00000038 – PC = 0x18,而該地址中儲存了IRQ中斷的通用處理函式OS_CPU_ARM_ExceptIrqHndlr()的地址,LDRPC,[PC,#0x18]這條指令是指將PC+0x18地址處的內容載入到PC中,實質上也就完成跳轉到異常處理函式的操作。

這樣處理的好處是因為LDR的載入範圍是一個固定值+-32M,我們不能保證異常處理程式的地址剛好在+-32M左右,採用這種LDR PC,ADDR(固定地址)的形式就能實現大範圍的跳轉操作。

我們僅僅以FIQ中斷處理的形式進行討論,其他的異常有一定的相似性,只是在返回地址上存在差別。這段程式碼主要是完成暫存器的壓棧,返回地址的調整,儲存等操作。具體的看下面的分析:

AREA CODE, CODE, READONLY

CODE32

OS_CPU_ARM_ExceptFiqHndlr

;修改中斷返回地址,這屬於進入真正處理函式前的返回地址調整,具體的返回地址依據前面儲存的R14進行相應的修改。

SUB LR, LR, #4 ; LRoffset to return from this exception: -4.

;壓棧操作

STMFD SP!, {R0-R12, LR} ; Pushworking registers.

;儲存連結暫存器

MOV R2, LR ; Savelink register.

;設定好ID號,這是非常必要的,只有這樣才能辨別屬於那種異常

MOV R0, #OS_CPU_ARM_EXCEPT_FIQ ;Set exception ID

/*跳轉到通用的異常處理函式,傳遞的引數是異常ID號*/

B OS_CPU_ARM_ExceptHndlr; Branch toglobal exception handler.

OS_CPU_ARM_ExceptHndlr(except_type)是一個通用的異常處理函式,可以對除了IRQ以外的其他異常進行控制操作。在這個通用處理函式中又呼叫了下面的函式OS_CPU_ARM_ExceptHndlr_BreakExcept()或者OS_CPU_ARM_ExceptHndlr_BreakTask()。這兩個函式中又呼叫了通用處理函式OS_CPU_ExceptHndlr(),然後OS_CPU_ExceptHndlr()中呼叫具體的中斷處理操作。

一般的OS_CPU_ExceptHndlr()處理形式,可以認為是一個模板如下:

void OS_CPU_ExceptHndlr(INT32U except_type)

{

/*Determine behavior according to exception type (except_type) */

/*If an IRQ or FIQ ,具體的可能要使用中斷向量等形式實現*/

while(there are interrupting devices) {

/*Clear interrupting device */

OS_CPU_SR_INT_En();/* Enable nesting, if desired */

/*Handle interrupt */

}

}

這是其中的一段關於IRQ中斷的文字複述:

IRQ中斷的基本的流程圖如下:

以上的uC/OS-II異常處理就分析完了,這種方式的實現實質上是採用了通用模板的形式,這樣實現出來的形式只需要控制一定的,具體的一些IRQ中斷處理函式(如定時器,GPIO等的中斷),與具體的廠商有很大的關係,有的廠商採用硬體暫存器的方式進行設計,有的採用軟體方式實現,因此具體的中斷。

後面我再分析我們通常認為的中斷(實質上就是IRQ和IFQ中某一個具體中斷)處理方式。

近來翻了翻uC/OS-II官網給出來的ARM7-ARM9移植手冊(AN-104),分析了在ARM中移植的問題,想想從來沒有認真的學習過ARM的彙編,趁著這個機會複習複習吧。其實底層的東西才是創造力的心臟。

其中的移植程式碼中存在的很多問題比如中斷的關閉和開啟,任務級別的情景切換,中斷到任務的情景切換都是我們在平時移植中講到,我也不在此強調了。在官網中提供的移植過程中存在異常處理機制,這個本不是在移植過程中考慮的,但是文件中確實提供了一個比較好的處理方式。我在此對這一段時間的學習做一個總結。

首先需要了解ARM的異常處理機制,異常是每一種處理器都必須考慮的問題之一,關鍵在於如何讓處理,返回地址在什麼位置都是需要考慮的,

ARM中支援7種異常,其中包括復位、未定義指令異常、軟中斷異常、預取指令中止、資料中止、IRQ、IFQ。每一種異常執行在特定的處理器模式下。我在此逐一的分析。

一般異常發生後,CPU都會進行一系列的操作,這些操作有一部分是CPU自動完成,有一部分是需要我們程式設計師完成。

首先說明CPU會自動完成的部分,用ARM結構手冊中的程式碼描述如下:

R14_= return link //這個可以參看暫存器的說明,兩個作用

SPSR_<exception_mode > = CPSR

CPSR[4:0]= exception mode number

CPSR[5]= 0 ; //AEM指令

If==Reset or Fiq then //只有在復位和FIQ模式下才會關閉FIQ中斷

CPSR[6] = 1 ;

CPSR[7]= 1 ; //任何異常模式下都會關閉IRQ中斷

PC= exception vector address

從上面的程式碼中我們可以發現CPU自動處理的過程包括如下:

1、 拷貝CPSR到SPSR_

2、 設定適當的CPSR位: 改變處理器狀態進入ARM狀態;改變處理器模式進入相應的異常模式;設定中斷禁止位禁止相應中斷。

3、 更新LR_,這個暫存器中儲存的是異常返回時的連結地址

4、 設定PC到相應的異常向量

以上的操作都是CPU自動完成,異常的向量表如下:

返回地址問題

異常的返回地址也是需要我們注意的地方,不同的異常模式返回地址也是存在差異的,這主要是因為各種異常產生的機理存在差別所導致的。這樣我們的需要在異常進入處理函式之前或者在返回時調整返回地址,一般採用進入異常處理函式前進行手動調整。下面每一種異常R14儲存的值都給了出來,其中也包含了CPU自動處理的部分,根據儲存的R14就可以知道怎樣實現地址的返回。

復位異常:

可以看出該模式下的先對來說返回地址也比較簡單,不需要做太多的描述。

未定義的指令異常:

MOVS PC, R14

軟中斷異常:

返回的方式也比較簡單:

MOVS PC, R14

預取指令中止異常:

返回需要做下面的調整:

SUBS PC, R14, #4

資料中止

返回地址需要做下面的調整:

如果需要重新訪問資料則:

SUBS PC, R14, #8

如果不需要重新訪問資料則:

SUBS PC, R14, #4

IRQ中斷的處理過程:

返回地址需要做下面的調整:

SUBSPC,R14,#4

IFQ中斷:

返回地址需要做下面的調整:

SUBS PC, R14 ,#4

從上面的程式碼可以知道,對於每一種異常,儲存的返回地址都是不一樣的,一般都需要我們手動的跳轉,當然調整的時機也需要我們選擇,是在進入處理前跳轉還是返回時調整都是需要我們程式設計師控制的。

在ARM Developer Suite DeveloperGuide中對ARM處理器的異常處理操作提供能更加詳細的解釋,每一種異常下的處理方式如下文描述:

異常返回時另一個非常重要的問題是返回地址的確定,在前面曾提到進入異常時處理器會有一個儲存LR 的動作,但是該儲存值並不一定是正確的返回地址,下面以一個簡單的指令執行流水狀態圖來對此加以說明。

我們知道在ARM 架構裡,PC值指向當前執行指令的地址加8處,也就是說, 當執行指令A(地址0x8000)時,PC 等於指令C 的地址(0x8008)。假如指令A 是“BL”指令,則當執行該指令時,會把PC(=0x8008)儲存到LR 暫存器裡面,但是接下去處理器會馬上對LR 進行一個自動的調整動作:LR=LR-0x4。這樣,最終儲存在 LR 裡面的是 B 指令的地址,所以當從 BL 返回時,LR 裡面正好是正確的返回地址。同樣的調整機制在所有LR自動儲存操作中都存在,比如進入中斷響應時,處理器所做的LR 儲存中,也進行了一次自動調整,並且調整動作都是LR=LR-0x4。

下面,我們對不同型別的異常的返回地址依次進行說明:

假設在指令A 處(地址0x8000)發生了異常,進入異常響應後,LR 上經過調整儲存的地址值應該是B 的地址0x8004。

1、 如果發生的是軟體中斷,即A 是“SWI”指令

異常是由指令本身引起的,從 SWI 中斷返回後下一條執行指令就是B,正好是LR 暫存器儲存的地址, 所以只要直接把LR 恢復給PC。

MOVS pc,lr

2、 發生的是Undefinedinstruction異常

異常是由指令本身引起的,從異常返回後下一條執行指令就是B,正好是LR 暫存器儲存的地址, 所以只要直接把LR 恢復給PC。

MOVS pc,lr

3、 發生的是IRQ或FIQ中斷

因為指令不可能被中斷打斷,所以A指令執行完以後才能響應中斷,此時PC已更新,指向指令D的地址(地址0x800C),LR 上經過調整儲存的地址值是C 的地址0x8008。中斷返回後應該執行B指令,所以返回操作是:

SUBS pc,lr, #4

4、 發生的是Prefetch Abort異常

該異常並不是處理器試圖從一個非法地址取指令時觸發,取出的指令只是被標記為非法,按正常處理流程放在流水線上,在執行階段觸發Prefetch Abort異常,此時LR 上經過調整儲存的地址值是B 的地址0x8004。異常返回應該返回到A指令,嘗試重新取指令,所以返回操作是:

SUBS pc,lr, #4

5、 發生的是“Data Abort”

CPU訪問儲存器時觸發該異常,此時PC指向指令D的地址(地址0x800C),LR 上經過調整儲存的地址值是C 的地址0x8008。異常返回後,應回到指令A,嘗試重新操作儲存器,所以返回操作是:

SUBS pc,lr, #8

以上就是ARM異常的CPU操作部分,接下來就是程式設計師應該完成的操作。

1. 由於CPU會自動跳轉到對應的異常向量中,因此只需要在在各個異常向量中存放對應的操作,最簡單的都是存放一個B指令跳轉到對應的異常處理函式的操作即可。但由於B指令的跳轉返回只有+-32M,而異常處理函式的地址可能會超過+-32M,因此可以採用另一種方式實現方式:在異常向量中儲存一條指令LDR PC[addr],其中的addr中就儲存了異常處理函式的地址,當然addr的相對地址要小於+-32M。這樣也就解決了跳轉範圍的問題。

2. 接下來就是異常處理函式對應的操作,可以在進入異常處理之前就進行返回地址的調整,這樣後面就不用進行處理啦,當然也可以在返回過程中再調整。一般都是在這個過程中進行調整。進行壓棧操作,儲存對應的環境變數。呼叫實際的處理過程等。

3. 出棧,恢復CPU的狀態和暫存器的值。由於第一步中已經調整好返回地址,這一步不需要再次調整。當然如果之前沒有調整,這裡則需要進行相應的調整。

在uC/OS-II的官網移植中採用通用異常處理函式的方式實現異常的處理,下面我們來分析其中的部分程式碼:

首先是處理器部分的移植,包括異常向量、異常的ID號,儲存異常處理函式地址的地址等:

/*ARM的異常ID號,支援7種類型的異常,每一種異常都存在一個ID號*/

#define OS_CPU_ARM_EXCEPT_RESET 0x00

#define OS_CPU_ARM_EXCEPT_UNDEF_INSTR 0x01

#define OS_CPU_ARM_EXCEPT_SWI 0x02

#define OS_CPU_ARM_EXCEPT_PREFETCH_ABORT 0x03

#define OS_CPU_ARM_EXCEPT_DATA_ABORT 0x04

#define OS_CPU_ARM_EXCEPT_ADDR_ABORT 0x05

#define OS_CPU_ARM_EXCEPT_IRQ 0x06

#define OS_CPU_ARM_EXCEPT_FIQ 0x07

#define OS_CPU_ARM_EXCEPT_NBR 0x08

/*異常向量地址*/

#define OS_CPU_ARM_EXCEPT_RESET_VECT_ADDR (OS_CPU_ARM_EXCEPT_RESET * 0x04 + 0x00) //0x00

#define OS_CPU_ARM_EXCEPT_UNDEF_INSTR_VECT_ADDR (OS_CPU_ARM_EXCEPT_UNDEF_INSTR * 0x04 + 0x00) //0x04

#define OS_CPU_ARM_EXCEPT_SWI_VECT_ADDR (OS_CPU_ARM_EXCEPT_SWI * 0x04 + 0x00) //0x08

#define OS_CPU_ARM_EXCEPT_PREFETCH_ABORT_VECT_ADDR (OS_CPU_ARM_EXCEPT_PREFETCH_ABORT * 0x04 +0x00) //0x0c

#define OS_CPU_ARM_EXCEPT_DATA_ABORT_VECT_ADDR (OS_CPU_ARM_EXCEPT_DATA_ABORT * 0x04 + 0x00) //0x10

/*這個異常是ARM中不支援的異常*/

#define OS_CPU_ARM_EXCEPT_ADDR_ABORT_VECT_ADDR (OS_CPU_ARM_EXCEPT_ADDR_ABORT * 0x04 + 0x00) //0x14

#define OS_CPU_ARM_EXCEPT_IRQ_VECT_ADDR (OS_CPU_ARM_EXCEPT_IRQ * 0x04 + 0x00) //0x18

#define OS_CPU_ARM_EXCEPT_FIQ_VECT_ADDR (OS_CPU_ARM_EXCEPT_FIQ * 0x04 + 0x00) //0x1c

/*儲存異常處理函式地址的地址*/

/* ARMexception handlers addresses */

#define OS_CPU_ARM_EXCEPT_RESET_HANDLER_ADDR (OS_CPU_ARM_EXCEPT_RESET * 0x04 + 0x20) //0x20

#define OS_CPU_ARM_EXCEPT_UNDEF_INSTR_HANDLER_ADDR (OS_CPU_ARM_EXCEPT_UNDEF_INSTR * 0x04 + 0x20) //0x24

#define OS_CPU_ARM_EXCEPT_SWI_HANDLER_ADDR (OS_CPU_ARM_EXCEPT_SWI * 0x04 + 0x20) //0x28

#define OS_CPU_ARM_EXCEPT_PREFETCH_ABORT_HANDLER_ADDR (OS_CPU_ARM_EXCEPT_PREFETCH_ABORT * 0x04 +0x20) //0x2c

#define OS_CPU_ARM_EXCEPT_DATA_ABORT_HANDLER_ADDR (OS_CPU_ARM_EXCEPT_DATA_ABORT * 0x04 + 0x20) //0x30

#define OS_CPU_ARM_EXCEPT_ADDR_ABORT_HANDLER_ADDR (OS_CPU_ARM_EXCEPT_ADDR_ABORT * 0x04 + 0x20) //0x34

#define OS_CPU_ARM_EXCEPT_IRQ_HANDLER_ADDR (OS_CPU_ARM_EXCEPT_IRQ * 0x04 + 0x20) //0x38

#define OS_CPU_ARM_EXCEPT_FIQ_HANDLER_ADDR (OS_CPU_ARM_EXCEPT_FIQ * 0x04 + 0x20) //0x3c

/*儲存在異常向量中的內容,實質上是LDR PC,[PC,#0x18]的機器碼*/

#define OS_CPU_ARM_INSTR_JUMP_TO_SELF 0xEAFFFFFE

/* ARM"Jump To Exception Handler" asm instruction */

異常的初始化函式,首先,完成了在異常向量中儲存指令的操作,採用機器碼的形式就能避免直接訪問暫存器什麼的,其次,完成在固定的地址處存放對應異常處理函式的地址。其中採用了賦值的形式也是需要注意的,採用的強制型別轉換和指標相結合的形式。保證了是修改地址處的內容。而不是修改地址。

/*初始化異常中斷向量*/

void OS_CPU_InitExceptVect (void)

{

/*

OS_CPU_ARM_EXCEPT_UNDEF_INSTR_VECT_ADDR是對應中斷向量表的地址

OS_CPU_ARM_INSTR_JUMP_TO_HANDLER是儲存了對應的OS_CPU_ARM_INSTR_JUMP_TO_HANDLER(實質上是一個指令)

實質上就是在異常向量中存放了:LDR PC [PC, #0x18],也就是讓PC指向對應的異常處理地址中的內容,

也就是實現到實際處理函式的跳轉。

異常處理地址中儲存了實際的異常處理函式的地址

其他的異常也有相同的操作,OS_CPU_ARM_INSTR_JUMP_TO_HANDLER是一個指令的機器碼形式

*/

(*(INT32U*)OS_CPU_ARM_EXCEPT_UNDEF_INSTR_VECT_ADDR) = OS_CPU_ARM_INSTR_JUMP_TO_HANDLER;

(*(INT32U*)OS_CPU_ARM_EXCEPT_UNDEF_INSTR_HANDLER_ADDR) = (INT32U)OS_CPU_ARM_ExceptUndefInstrHndlr;

(*(INT32U *)OS_CPU_ARM_EXCEPT_SWI_VECT_ADDR) = OS_CPU_ARM_INSTR_JUMP_TO_HANDLER;

(*(INT32U*)OS_CPU_ARM_EXCEPT_SWI_HANDLER_ADDR) = (INT32U)OS_CPU_ARM_ExceptSwiHndlr;

(*(INT32U*)OS_CPU_ARM_EXCEPT_PREFETCH_ABORT_VECT_ADDR) = OS_CPU_ARM_INSTR_JUMP_TO_HANDLER;

(*(INT32U*)OS_CPU_ARM_EXCEPT_PREFETCH_ABORT_HANDLER_ADDR) =(INT32U)OS_CPU_ARM_ExceptPrefetchAbortHndlr;

(*(INT32U*)OS_CPU_ARM_EXCEPT_DATA_ABORT_VECT_ADDR) = OS_CPU_ARM_INSTR_JUMP_TO_HANDLER;

(*(INT32U*)OS_CPU_ARM_EXCEPT_DATA_ABORT_HANDLER_ADDR) = (INT32U)OS_CPU_ARM_ExceptDataAbortHndlr;

(*(INT32U *)OS_CPU_ARM_EXCEPT_ADDR_ABORT_VECT_ADDR) = OS_CPU_ARM_INSTR_JUMP_TO_HANDLER;

(*(INT32U*)OS_CPU_ARM_EXCEPT_ADDR_ABORT_HANDLER_ADDR) = (INT32U)OS_CPU_ARM_ExceptAddrAbortHndlr;

(*(INT32U*)OS_CPU_ARM_EXCEPT_IRQ_VECT_ADDR) = OS_CPU_ARM_INSTR_JUMP_TO_HANDLER;

(*(INT32U*)OS_CPU_ARM_EXCEPT_IRQ_HANDLER_ADDR) = (INT32U)OS_CPU_ARM_ExceptIrqHndlr;

/*在異常向量中儲存對應的操作,實質上就是將PC值調轉*/

(*(INT32U*)OS_CPU_ARM_EXCEPT_FIQ_VECT_ADDR) = OS_CPU_ARM_INSTR_JUMP_TO_HANDLER;

(*(INT32U*)OS_CPU_ARM_EXCEPT_FIQ_HANDLER_ADDR) = (INT32U)OS_CPU_ARM_ExceptFiqHndlr;

}

|

異常型別 |

Mode |

異常向量 |

內容 |

|

IFQ異常 |

IFQ |

0x0000001C |

LDR PC,[PC,#0x18] 0xE59FF018 |

|

0x00000038 |

Address of OS_CPU_ARM_ExceptIrqHndlr() |

||

|

0x0000003C |

Address of OS_CPU_ARM_ExceptFiqHndlr() |

有必要的討論一下,為什麼在向量中儲存的是指令: LDR PC,[PC,#0x18],我們從上面的地址可以知道,IRQ異常處理函式地址被儲存到了0x00000038中,異常向量與該地址之間的差值是0x20,那麼為什麼在其中儲存的值只是0x18呢?這還要討論ARM的流水線結構,當前執行的命令相比PC指向的地址差0x08。也就是當前執行的指令的地址是PC-0x08.當PC指向異常向量以後(取值),還需要等待一個時鐘(譯碼)之後才會被執行(真正意義上的執行操作),而這時PC值已經被更新了。指向了Vector+0x8的位置,因此我們可以知道,當執行向量中的程式碼時,這時PC=Vector+0x8,而這時相對於固定的0x20-0x08=0x18,這也就是為什麼是LDRPC,[PC,#0x18],而不是LDR PC,[PC,#0x20].

採用上面的例子說明IRQ的向量為0x00000018,而設定好的固定地址用來儲存對應異常處理函式地址的地址是0x00000038,當CPU執行完PC =0x00000018以後,還需要譯碼、才能被執行,這時候PC值已經更新為PC =0x00000018 + 0x08;這時候固定地址距離PC的相對位置位0x00000038 – PC = 0x18,而該地址中儲存了IRQ中斷的通用處理函式OS_CPU_ARM_ExceptIrqHndlr()的地址,LDRPC,[PC,#0x18]這條指令是指將PC+0x18地址處的內容載入到PC中,實質上也就完成跳轉到異常處理函式的操作。

這樣處理的好處是因為LDR的載入範圍是一個固定值+-32M,我們不能保證異常處理程式的地址剛好在+-32M左右,採用這種LDR PC,ADDR(固定地址)的形式就能實現大範圍的跳轉操作。

我們僅僅以FIQ中斷處理的形式進行討論,其他的異常有一定的相似性,只是在返回地址上存在差別。這段程式碼主要是完成暫存器的壓棧,返回地址的調整,儲存等操作。具體的看下面的分析:

AREA CODE, CODE, READONLY

CODE32

OS_CPU_ARM_ExceptFiqHndlr

;修改中斷返回地址,這屬於進入真正處理函式前的返回地址調整,具體的返回地址依據前面儲存的R14進行相應的修改。

SUB LR, LR, #4 ; LRoffset to return from this exception: -4.

;壓棧操作

STMFD SP!, {R0-R12, LR} ; Pushworking registers.

;儲存連結暫存器

MOV R2, LR ; Savelink register.

;設定好ID號,這是非常必要的,只有這樣才能辨別屬於那種異常

MOV R0, #OS_CPU_ARM_EXCEPT_FIQ ;Set exception ID

/*跳轉到通用的異常處理函式,傳遞的引數是異常ID號*/

B OS_CPU_ARM_ExceptHndlr; Branch toglobal exception handler.

OS_CPU_ARM_ExceptHndlr(except_type)是一個通用的異常處理函式,可以對除了IRQ以外的其他異常進行控制操作。在這個通用處理函式中又呼叫了下面的函式OS_CPU_ARM_ExceptHndlr_BreakExcept()或者OS_CPU_ARM_ExceptHndlr_BreakTask()。這兩個函式中又呼叫了通用處理函式OS_CPU_ExceptHndlr(),然後OS_CPU_ExceptHndlr()中呼叫具體的中斷處理操作。

一般的OS_CPU_ExceptHndlr()處理形式,可以認為是一個模板如下:

void OS_CPU_ExceptHndlr(INT32U except_type)

{

/*Determine behavior according to exception type (except_type) */

/*If an IRQ or FIQ ,具體的可能要使用中斷向量等形式實現*/

while(there are interrupting devices) {

/*Clear interrupting device */

OS_CPU_SR_INT_En();/* Enable nesting, if desired */

/*Handle interrupt */

}

}

這是其中的一段關於IRQ中斷的文字複述:

IRQ中斷的基本的流程圖如下:

以上的uC/OS-II異常處理就分析完了,這種方式的實現實質上是採用了通用模板的形式,這樣實現出來的形式只需要控制一定的,具體的一些IRQ中斷處理函式(如定時器,GPIO等的中斷),與具體的廠商有很大的關係,有的廠商採用硬體暫存器的方式進行設計,有的採用軟體方式實現,因此具體的中斷。

後面我再分析我們通常認為的中斷(實質上就是IRQ和IFQ中某一個具體中斷)處理方式。