intel FPGA CLKn pin 是否能直接進PLL?

原創 by DeeZeng

FPGA的時鐘需要從專用的時鐘管腳輸入,那CLKn 作為Single-End時鐘pin時是否能直接進 PLL呢?

通過檢視對應FPGA型號的手冊,得出以下結論

1. Cyclone V, Stratix V 的 CLKn 不能直接進PLL,需要走GCLK,RCLK之後才行

2. MAX10 ,Arria 10 的 PLL ,CLKn 可以直接進PLL。 (Arria10 的 fPLL CLKn不能直接走,但 XCVR bank 的一般是 差分時鐘輸入)

如下以部分FPGA 系列舉例

1. Cyclone V,Stratix V FPGA

如下 Cyclone V, Stratix V手冊:

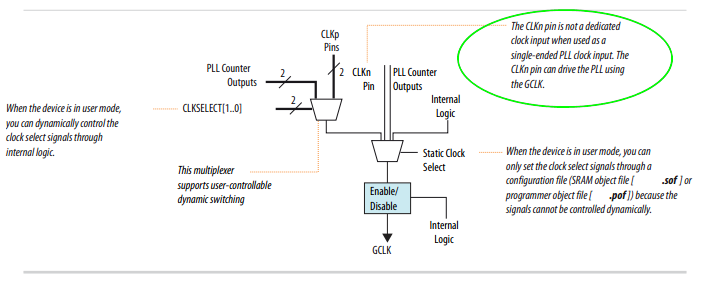

The CLKn pin is not a dedicated clock input when used as a single-ended PLL clock input.

The CLKn pin can drive the PLL using the GCLK.

如果quartus工程中,我們直接用 CLKn 的pin 進PLL

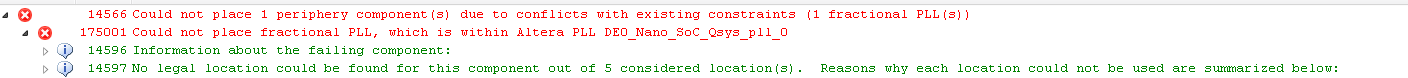

如果quartus工程中,我們直接用 CLKn 的pin 進PLL

那會出現如下報錯:

(如果實際硬體已經必須用CLKn進 PLL了,可以先用 CLK_CTRL ip 讓 CLKn 走GCLK)

2. MAX10 ,Arria10 FPGA

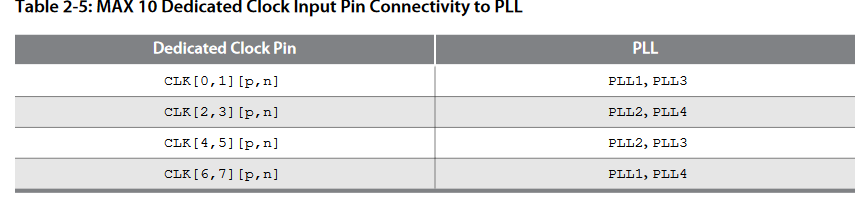

MAX10 的 CLKp,CLKn 都可以drive PLL

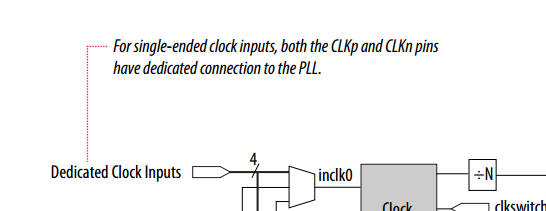

Arria 10 的IOPLL 的 CLKn可以直接進 IOPLL (both the CLKp and CLKn pins hav dedicated ...)

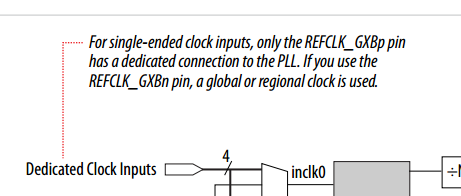

Arria 10 的fPLL 的 REFCLK_GXBn 不能直接進 fPLL (不過 XCVR bank 一般也都是 差分時鐘輸入,影響不大)

所以我們在設計FPGA 或 做工程的時候需要注意下當前 FPGA系列的 CLK屬性。能用專用pin 的就用專用pin

專用pin GCLK 等的好處, low slew rate , high fan out 等等。 timing 更容易滿足