低功耗設計技術--Multi VDD--Level shifter

本文轉自:自己的微信公眾號《積體電路設計及EDA教程》

前面的推文中我們分別介紹了低功耗設計中的Multi-VDD技術以及門控電源技術。在實際的低功耗設計中,門控電源技術中也常常結合Multi-VDD技術一起使用。

在使用了Multi-VDD技術之後,設計中會形成多個Power Domain(PD):

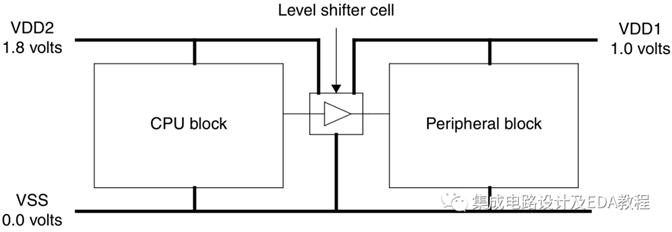

不同Power Domain之間如果需要資料的Talk,那麼在中間需要插入Level Shifter(電平轉換單元):

本推文我們來講解一下第二個特殊的Cell -- Level Shifter。

Level shifter Cell

Level Shifters主要是多供電電壓(MSV)的設計中,在2個不同電壓域之間有資料互動的情況下,需要將某個電壓域輸出的電平轉換成另一個電壓域可以識別的邏輯電平,因此需要用到電平轉換的器件,這就是Level Shifter。這種Cell在我們使用的IO中也廣泛存在,用於將外部的電壓與Core電壓之間進行轉換。

根據電平轉換的方向,Level Shifter可以分為三種:

HL -> 高電平轉低電平

LH -> 低電平轉高電平

HL_LH -> 雙向轉換均可

另外,如果設計中還採用了前面推文中講的Power Gating技術,在不通電壓域之間進行通訊的情況下,除了需要新增Level Shifter之外還需要用到另外一種Cell -> Isolation Cell。因為電源關斷之後,其驅動的電路就出現了輸入浮空的情況,它的輸入會處於高阻態,會用洩放電流將上面的電荷緩慢洩放掉,再次期間,其狀態是不能確定的(如下圖所示)。因此,為了解決這個問題,我們需要在電源關閉電路的輸出端新增一個隔離單元(Isolation Cell)將輸出鉗位到一個確定的狀態。

一般來說Isolation Cell的輸出部分有較大的電容負載,也就是說Isolation Cell的延時將會比較大,對時序有一定的影響,是需要注意的。

關於Isolation Cell的詳細內容下篇推文單獨講。

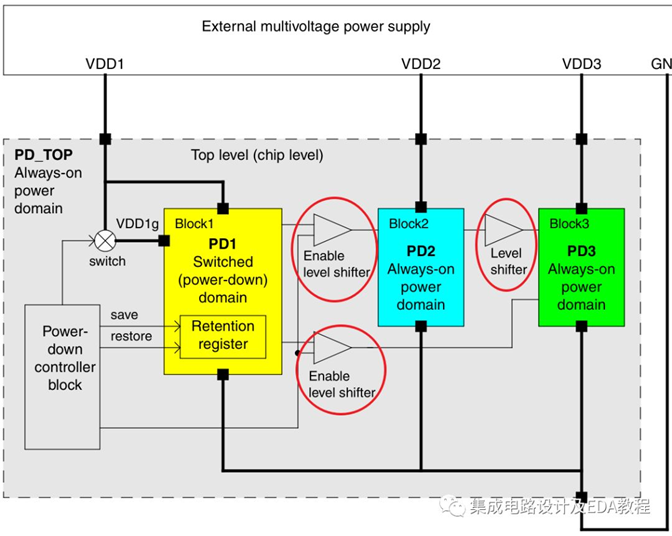

如果設計中含有Multi-VDD且有的Power Domain可以被關斷,多個Domain之間還有資料互動,那麼既需要用到Level Shifter也需要Isolation Cell,這種情況也非常常見。因此一般Foundary都會那種帶有Isolation功能的Level shifter,兼兩種功能。

下圖就是這種情況,PD1是可被關斷的,它與PD2以及PD3之間用的Level Shifter就是帶有Isolation功能的Level Shifter。而PD2是Always On的,所以它送到PD3的資料只需要用普通的Level Shifter即可。

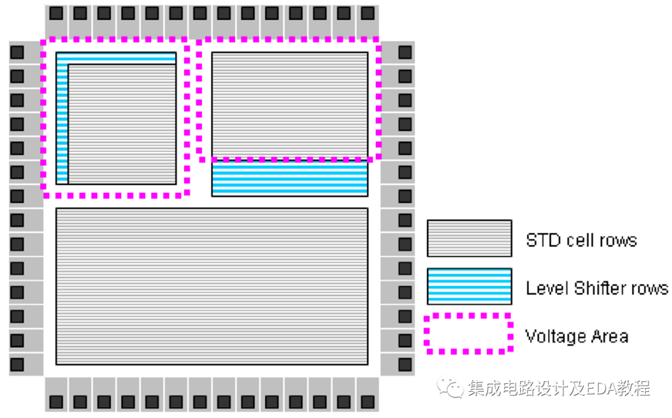

Level Shifter的物理佈局

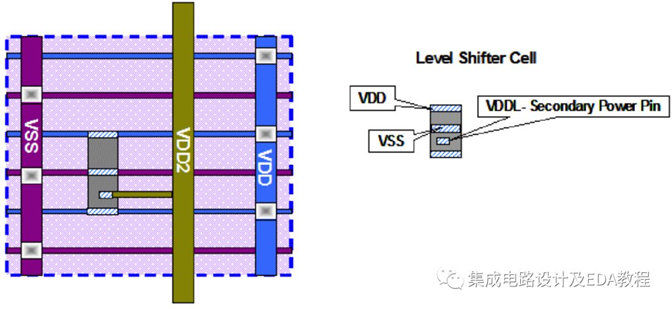

Level shifter是 Always-on Cell,一般有多個電源地Pin。它們的結構比較複雜,一般要比普通的Cell高度要高,它們的作用非常關鍵,我們需要保證它們的電源地連線是正確的。

考慮到以上因素,很多設計會採用下面的方案來擺放Level Shifter,將它們放置在特定區域內,Level Shifter的電源地Rail以及PG Pin的連線也更加規範有條理:

如下圖所示為Dual Height的Level shifter Cell在版圖中的擺放及其PG Pin的連線:

上面這種PG的連線特別的不方便,可能會佔用較多的Routing Resources引起DRC。

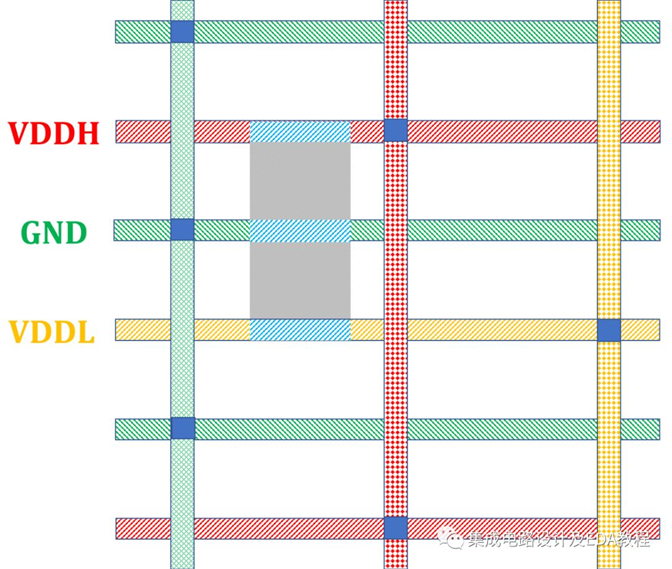

除此之外,還可以採用下面的雙Power Rail的方式,Level shifter橫跨兩個Rail的高度,兩個不同的VDD,一個GND。

下面描述的是Level Shifter的Liberty格式:

|

cell(level_shifter) { is_level_shifter : true ; #定義為true,則該Cell被認為是lever shifter cell level_shifter_type : HL | LH | HL_LH ; #定義電平轉換方向,HL表示高電平轉低電平,LH表示低電平轉高電平,HL_LH表示都可以用 input_voltage_range (<float>, <float>); #輸入電壓範圍,指該Cell輸入連線的電路,電壓工作範圍,EDA工具會根據Operating Condition的選擇,檢查該Cell是否滿足電路需要,可以在功能pin中進行定義,如果在cell主體定義,則必須與output_voltage_range同時存在 output_voltage_range (<float>, <float>);#輸出電壓範圍,指該Cell輸出連線的電路,電壓工作範圍,EDA工具會根據Operating Condition的選擇,檢查該Cell是否滿足電路需要,可以在功能pin中進行定義,如果在cell主體定義,則必須與input_voltage_range同時存在 … pg_pin(<pg_pin_name_P>) { pg_type : primary_power; std_cell_main_rail : true; #該primary_power連線在Cell設計中的主rail … } pg_pin(<pg_pin_name_G>) { pg_type : primary_ground; … } pin (data) { direction : input; input_signal_level : “<voltage_rail_name>”; #輸入訊號電壓環名 input_voltage_range ( <float> , <float>); level_shifter_data_pin : true ; #資料功能Pin … }/* End pin group */ pin (enable) { direction : input; input_voltage_range ( <float> , <float>); level_shifter_enable_pin : true ; #使能Pin,如果level shifter還作為isolation cell的時候,使能訊號會在電源關閉時停止level shifter功能,僅僅作為isolation cell存在 … }/* End pin group */ pin (output) { direction : output; output_voltage_range ( <float> , <float>); power_down_function : (!pg_pin_name_P + pg_pin_name_G); … }/* End pin group */ … }/* End Cell group */

#power_down_function 屬性用來識別出何時output pin處於電源被關斷的狀態。 The power_down_function string attribute is used to identify the condition when an output pin is switched off by pg_pin and to specify the Boolean condition under which the cell’s output pin is switched off (when the cell is in "off" mode due to the external power pin states) |

參考文獻:

孫軼群 ,國民技術股份有限公司,數字積體電路低功耗物理實現技術與UPF

Synopsys Low-Power Flow User G