FPGA中亞穩態相關問題及跨時鐘域處理

阿新 • • 發佈:2017-09-14

設計 時鐘 比特 產生 solution 至少 nbsp 觸發器 路徑規劃

前言

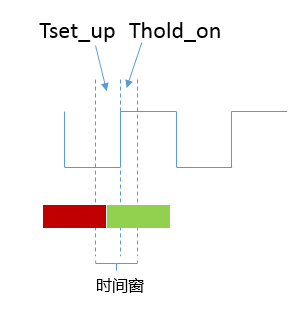

觸發器輸入端口的數據在時間窗口內發生變化,會導致時序違例。觸發器的輸出在一段時間內徘徊在一個中間電平,既不是0也不是1。這段時間稱為決斷時間(resolution time)。經過resolution time之後Q端將穩定到0或1上,但是穩定到0或者1,是隨機的,與輸入沒有必然的關系。

觸發器由於物理工藝原因,數據並不是理想化的只要觸發沿時刻不變即可。觸發器有固定的建立時間,保持時間。

建立時間:在時鐘有效沿到來前數據需要穩定的時間。

保持時間:在時鐘有效沿之後數據還需要保持不變的時間。

後果:會給設計帶來致命的功能故障。

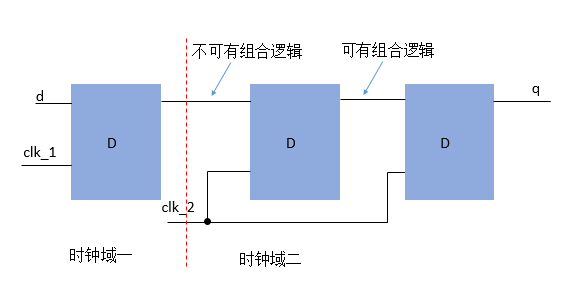

一般來說,信號是在異步信號,跨時鐘域,復位電路中產生亞穩態。

解決方式:

1.單比特信號:

①采用同步器同步,低速設計打兩拍,高速設計可能需要打三拍。

低速到高速時鐘域,低速信號一般能被高速時鐘域采到甚至多次。但高速時鐘域到低速時鐘域就不太好辦了:

②閉環解決方案:采用握手反饋信號,這會導致延時開銷大。

③開環解決方案:把信號展寬,至少為采樣T的1.5倍。這樣至少能采到一次。

2.多比特信號:

傳遞多比特信號,普通同步器就沒啥卵用了,因為多比特信號偶發數據變化歪斜,導致采到的不一定是正確數據。

①多比特信號融合:把多比特信號轉換為單比特信號,再用同步器同步。

②多周期路徑規劃:數據不需要同步,至需要同時傳遞一個同步的使能信號到接收時鐘域即可,使能信號沒被同步到接收時鐘域並被識別之前數據不被采集。即在信號某個沿產生同步脈沖指示信號。

③異步fifo。

以上。

FPGA中亞穩態相關問題及跨時鐘域處理