<DC guide ---4>

這是一個實驗課.

讀入一個vhdl文件,並完成整個dc流程。

實驗lab2總結:

復盤: 一開始讀入verilog時候,cwd出現了大量的中間文件。 查了read_vhdl也沒找到怎麽修改存儲路徑。後來在student guide裏面有。

之後讀入之後,link時,報錯 無法read sc_max.db ,一開始以為是vhdl和verilog不一樣呢。 後來才發現 search_path路徑寫錯了,dc找不到這個文件根本。

其實應該在dc invoke的時候就報出來了,沒仔細看。

之後讀入vhdl、設置current-design、link、check_design、保存一個ddc文件,進行compile,再保存一個ddc。exit退出。

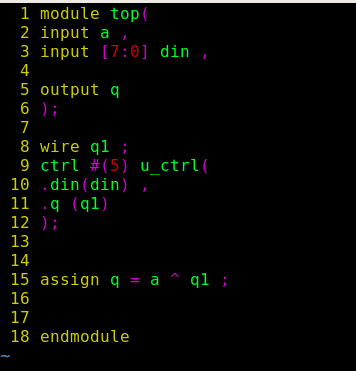

新增實驗: 設計一個帶有module例化的多層級top,完成對其的dc綜合。

復盤:

隨便寫了一個module,需要例化參數的。然後讀入 verilog時候,沒有報錯,執行link時候,報出了如下:

後來看到 student guide 關於analyze的介紹才知道, analyse是唯一的讀入帶parameter參數的途徑。所以以後都得用analyze這個命令了

使用之後,生成了一堆的中間文件,把cwd目錄弄得很亂。

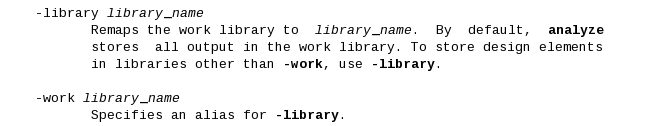

我們先查下analyze的help文檔:

我們先挑這4個。

-work : 是為WORK重新制定一個路徑,存放中間文件。

-library librname 沒看懂。。。。

-define 是為了預編譯準備的。

來實驗下:

在cwd上新建了一個jjj的目錄裏面存放了臨時文件。

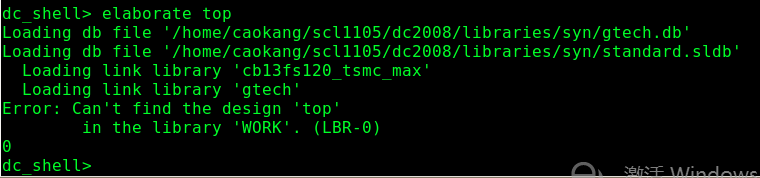

接下來: elaborate top ,既然報錯了。

說是 在WORK裏面找不到 top。 因為我們重新制定了WORK,所以沒有WORK。

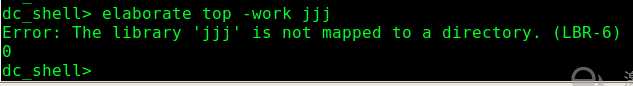

我們需要為elaborate指定路徑,好,看下圖:

居然報錯了,為什麽呢?再看下elaborate的man手冊。發現 -library 後面跟的是library_name 我們的jjj只是一個路徑,並不是library_name、

elaborate的man手冊如下圖:

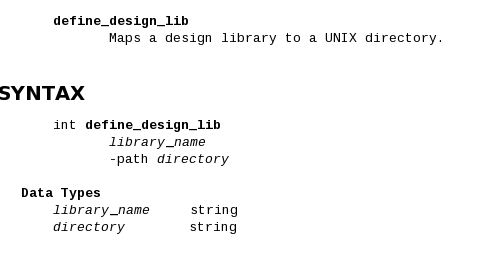

我們得想辦法給 路徑賦值一個name,這樣或許就行了。可以使用define_design_lib命令,語法如下:

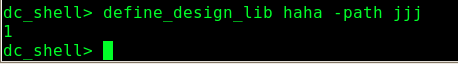

我們給路徑jjj,定義一個名字叫haha

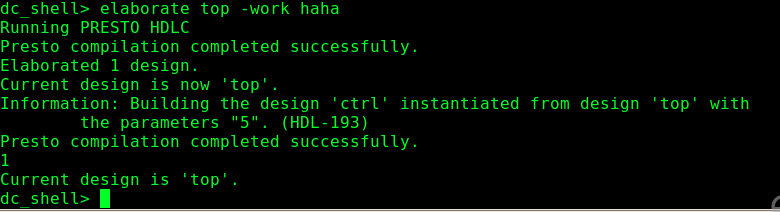

然後我們進行我們再去 elaborate,結果如下圖:好像成功了。

最後再綜合,保存netlist.v 得到結果:

<DC guide ---4>