[轉]FPGA使用LVDS差分信號的一些註意事項

最近在調試一個LVDS的屏顯功能,涉及到了一些LVDS的東東,簡單地整理如下,後續會再補充。

(1)對於altera FPGA(CYCLONE III)

1、對於作為LVDS傳輸的BANK必須接2.5V的VCCIO;

2、左右BANK(即1/2/5/6 BANK)的LVDS發送差分對信號無需外接匹配電阻,而上下BANK(即3/4/7/8 BANK)則需要,如果硬件工程師忘了,還可以在FPGA的IO引腳分配時裏加端接電阻設置;

3、分配管腳時,左右BANK的LVDS差分信號腳在IO分配時選擇的IO電平標準是LVDS,而上下BANK的LVDS差分信號腳在IO分配時選擇的IO電平標準是LVDS_E_3R;

4、分配管腳時,只要指定LVDS信號的p端(+),則n端(-)會自動分配。在verilog代碼中只要一個信號接口即可,無需在代碼中定義一個差分對接口;

5、在altera FPGA內使用的LVDS收發IP核是altlvds_rx和altlvds_tx,相應的IP使用說明在megawizard裏有。

(2)對於xilinx FPGA

區別altera的地方在於首先在Verilog的代碼裏,xilinx的LVDS信號需要定義一對差分對信號,通過xilinx的原語進行差分對轉單端或者單端轉成差分對信號。另外在IO引腳分配時,xilinx的電平標準都是一樣的,比如都是LVDS_33。

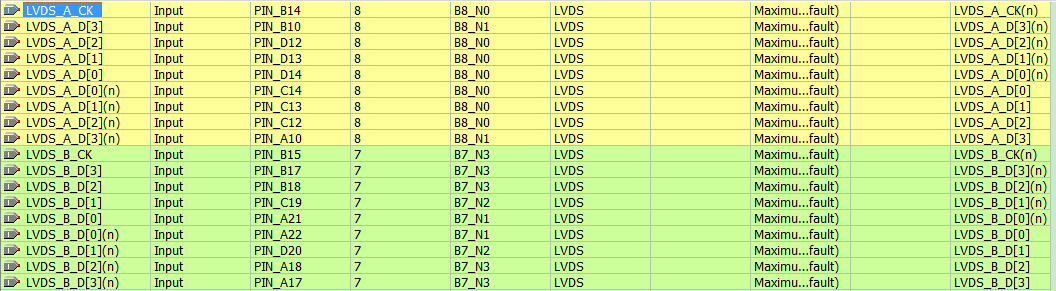

下圖1是altera下的LVDS信號引腳分配,可見用戶只需要分配p端(+)引腳即可。

圖1 altera LVDS引腳分配情況

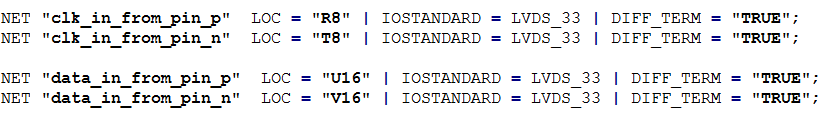

下圖2是xilinx的LVDS信號引腳分配,xilinx的LVDS引腳區分p端和n端。當然在vivado下引腳分配可以只分配P端腳號,N端腳號會自動分配。而在代碼裏都需要寫明差分對信號,再通過原語轉成單端信號。

圖2 xilinx下LVDS的引腳分配情況

[轉]FPGA使用LVDS差分信號的一些註意事項