tlm源碼分析——uvm**port/export/imp class的實現

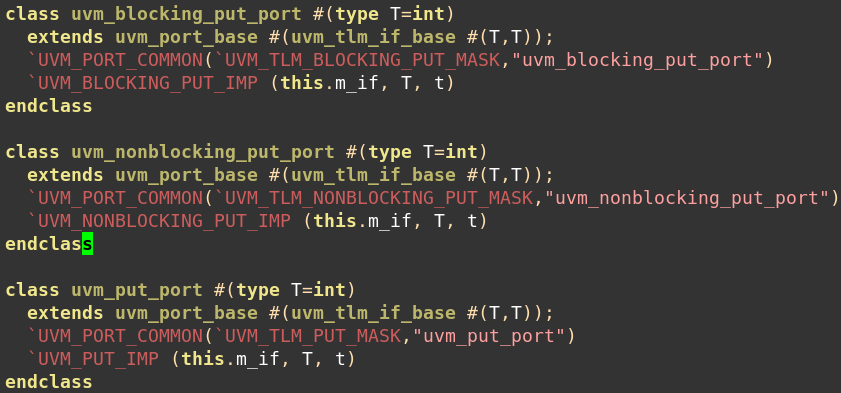

uvm在各種port,export,impclass的聲明,都是通過宏來定義的;

對於port的定義;有四種,put,get,peek,get_peek,

每一種都分為blocking,non_blocking,和都包含的部分;

在這種的port中,發出與接收的trans都是相同的,也是就不需要resp,是單向的。

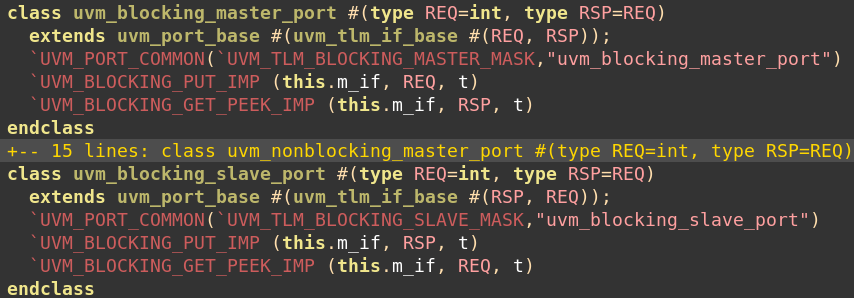

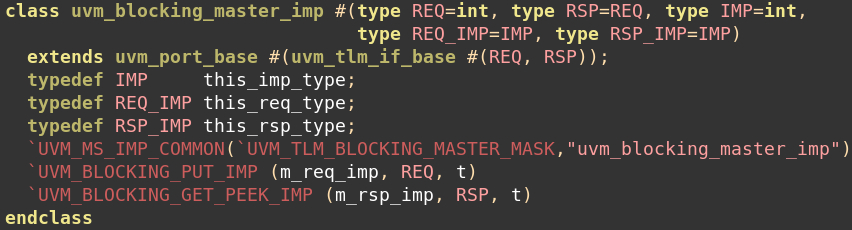

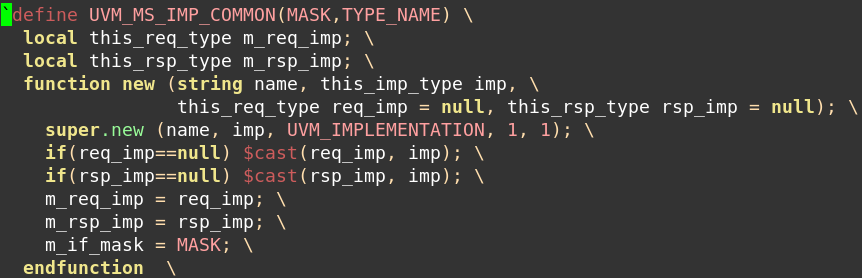

uvm也提供了雙向的master,slave的需要resp的class;跟transport不同的是,它分別定義了put和get的function,而不是

通過transport的方法;

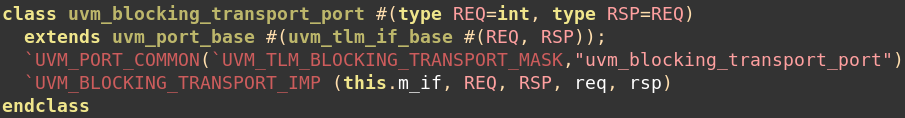

transport的三種function,block,non_block,transport_port;

export類似;

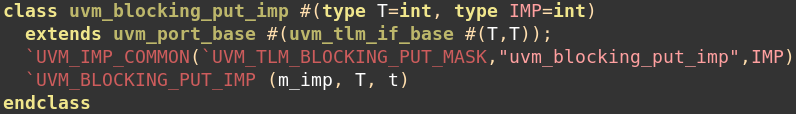

imp中最重要的一部分是進行m_imp的重載,實現通信一方調用imp的parent的function;

通信一方,拿到imp的指針,是在resolve_bindings中實現的。

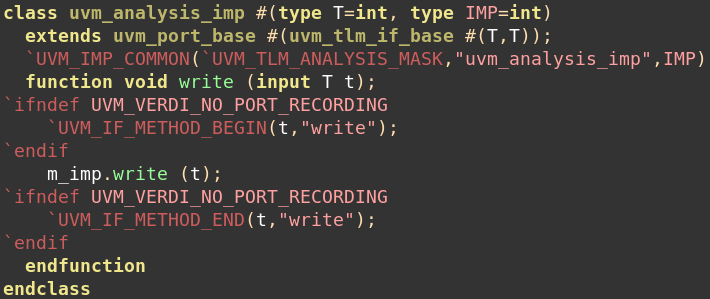

imp的class聲明中,也會包括兩個參數,第一個表示trans的類型,第二個表示聲明該tmp的class;

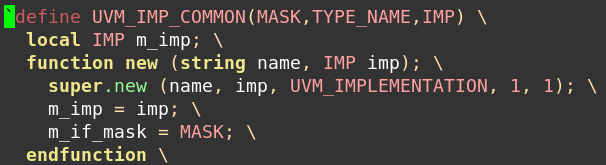

imp_common中主要實現new函數的聲明,和一個imp parent變量的賦值;imp的parent設為this;

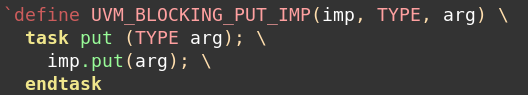

BLOCKING_PUT_IMP函數,調用m_imp中的函數,所以在imp的parent那個class中,必須實現相應的方法;

之上的imp,也是會實現put/get/peek/get_peek的imp,對於存在resp的imp,其中會定義兩個m_imp,要求在imp所在的

parent上的實現多個方法;兩個m_imp指向的其實是同一個;

以上這些函數在new的時候,都會設置min_szie和max_size都設置為1,所以,這些定義了之後有且只能連接一個;

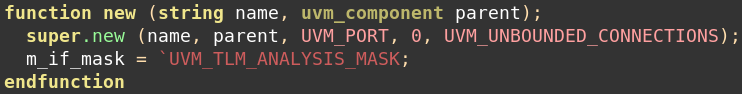

analysis_port 在new時,一般min_size賦值為0,max_size不規定上限,

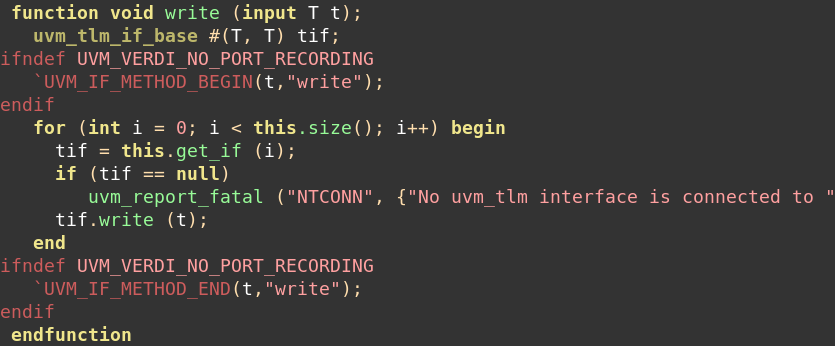

對於port和export,重載的write函數,會遍歷其中的m_if接口,依次調用其中的write函數;

imp函數,則只是調用m_imp中的write函數,m_imp也是imp parent的一個類型;

以上這些函數在聲明時,都會定義uvm_port_base從uvm_tlm_if_base中進行擴展;

tlm源碼分析——uvm**port/export/imp class的實現